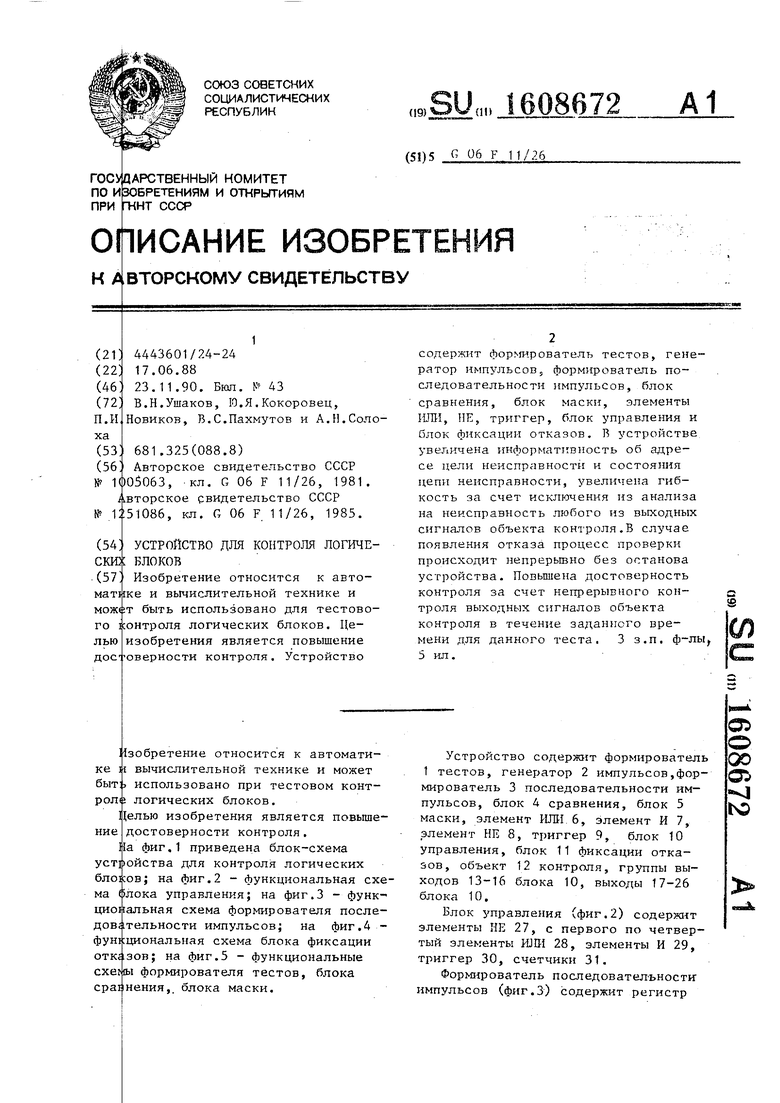

1зобретение относится к автоматике и вычислительной технике и может быть использовано при тестовом контроле логических блоков.

1елью изобретения является повышение

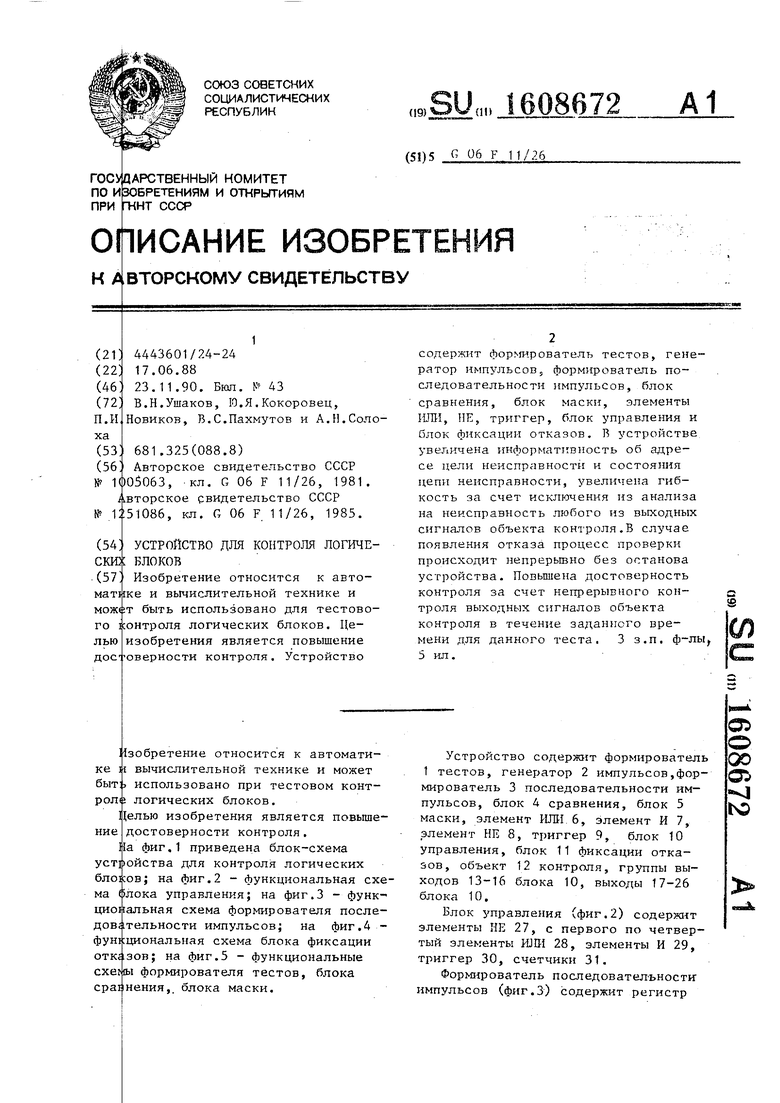

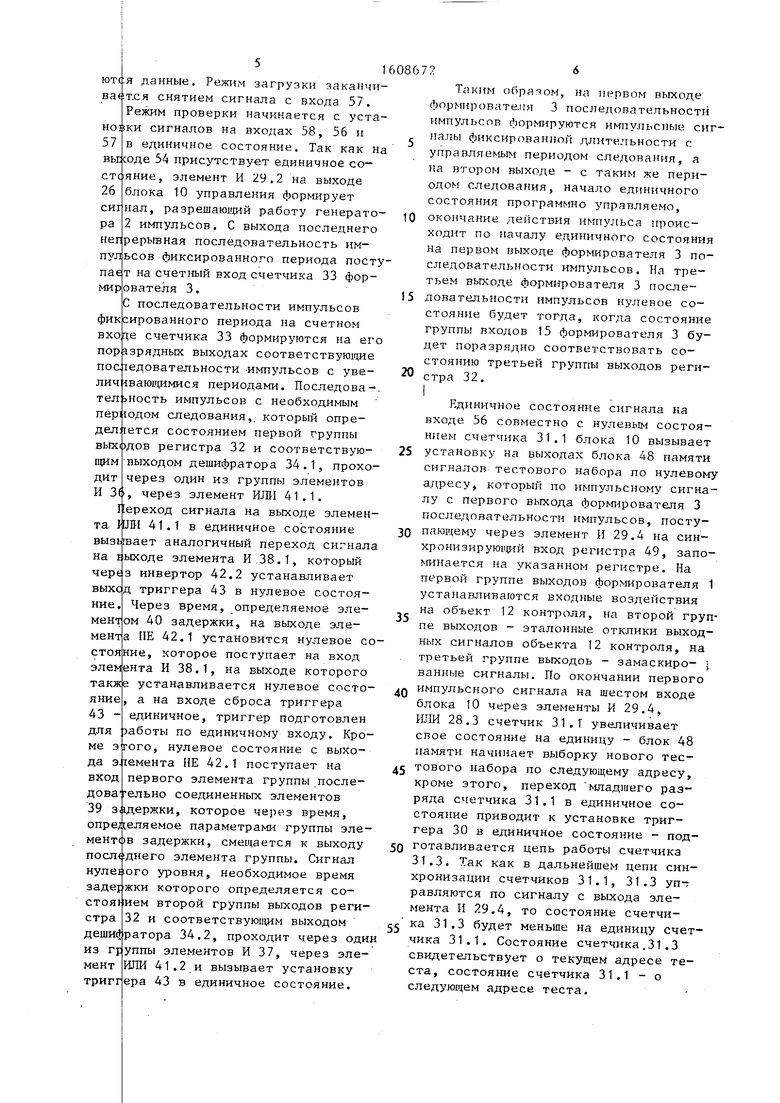

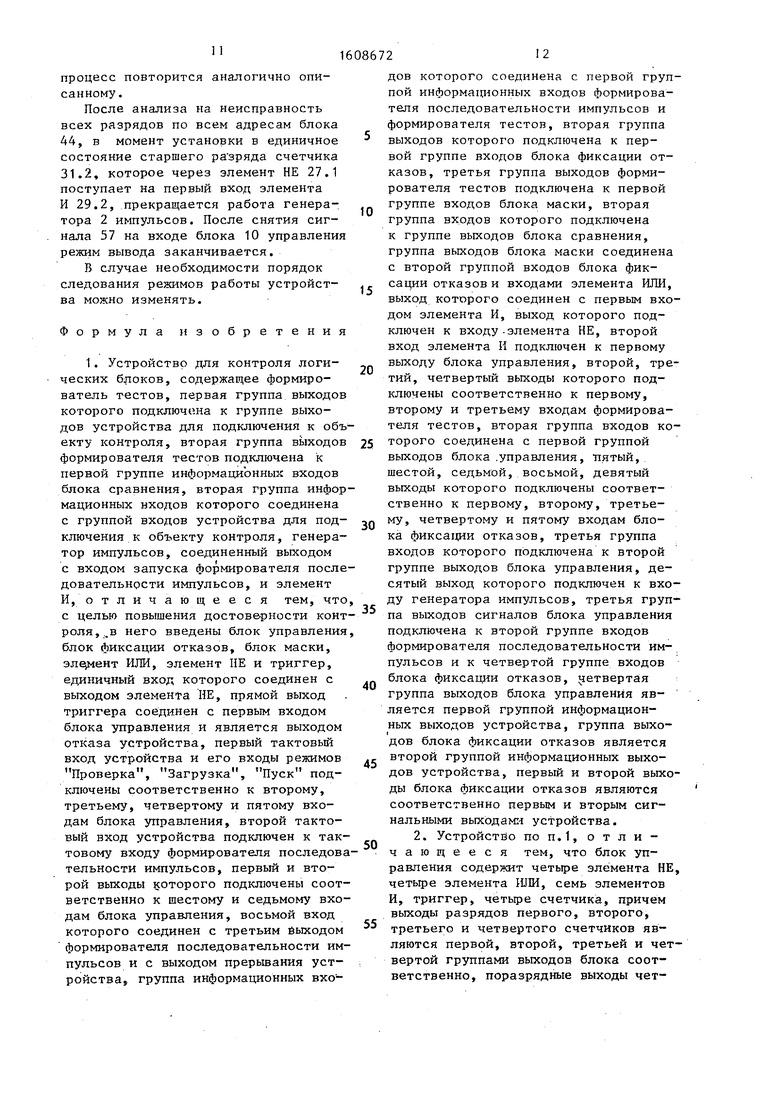

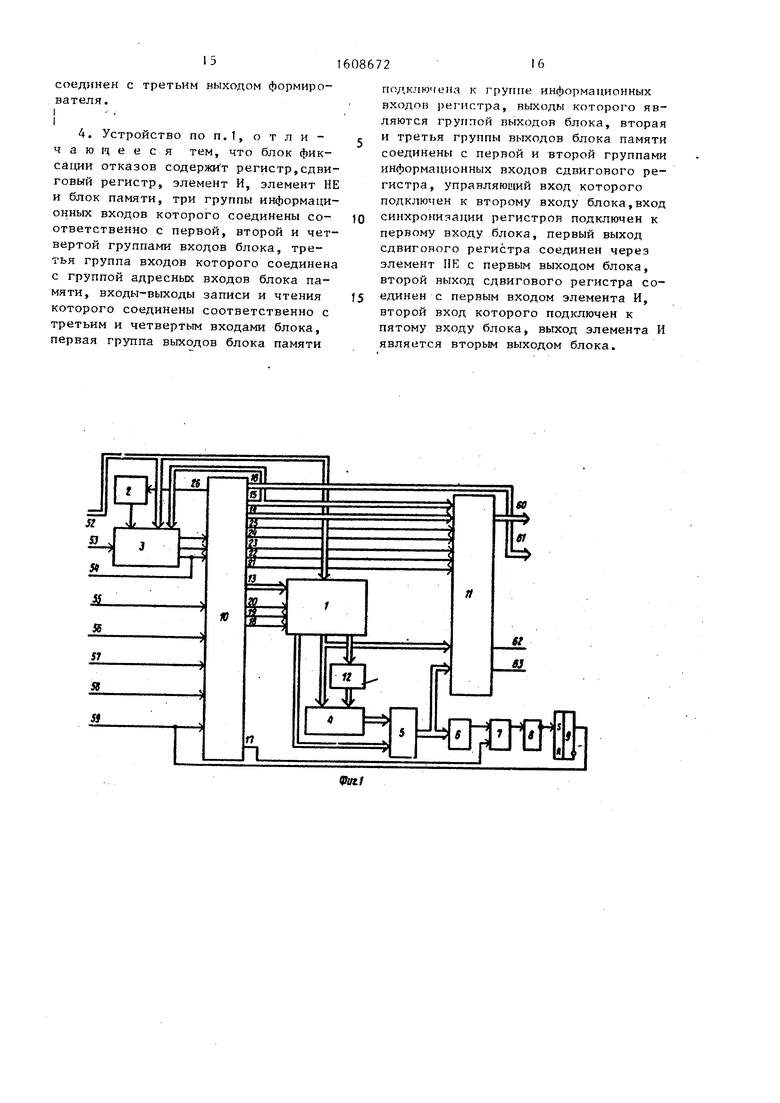

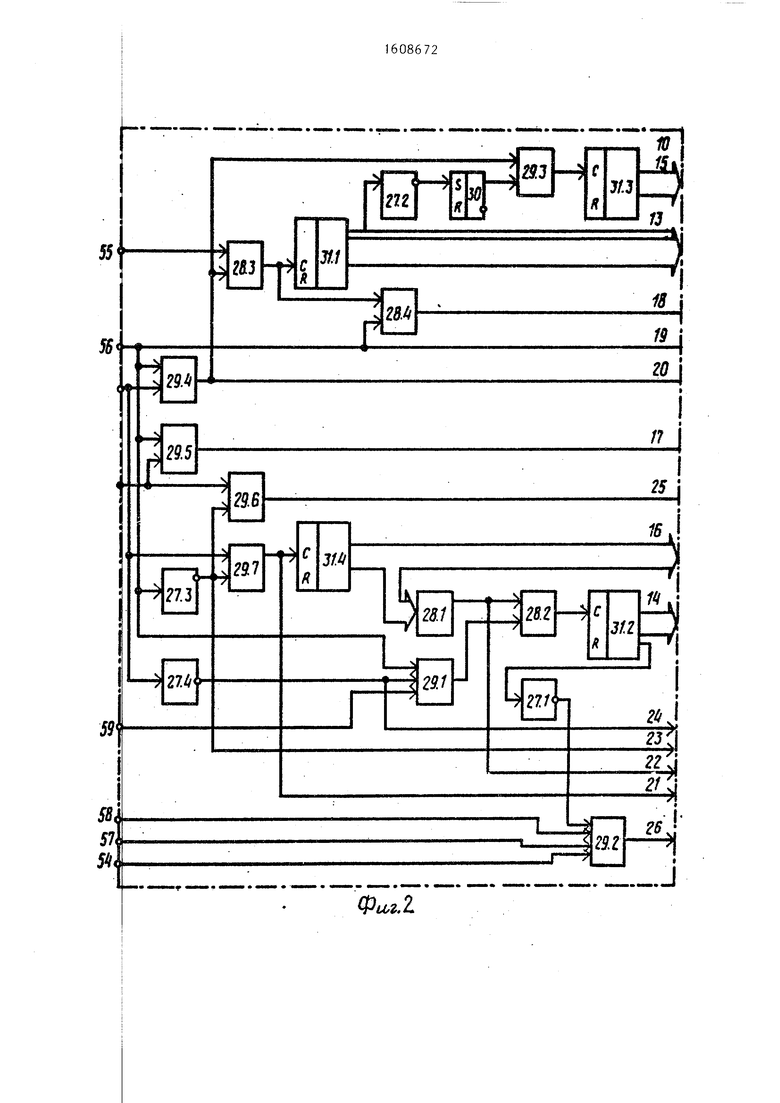

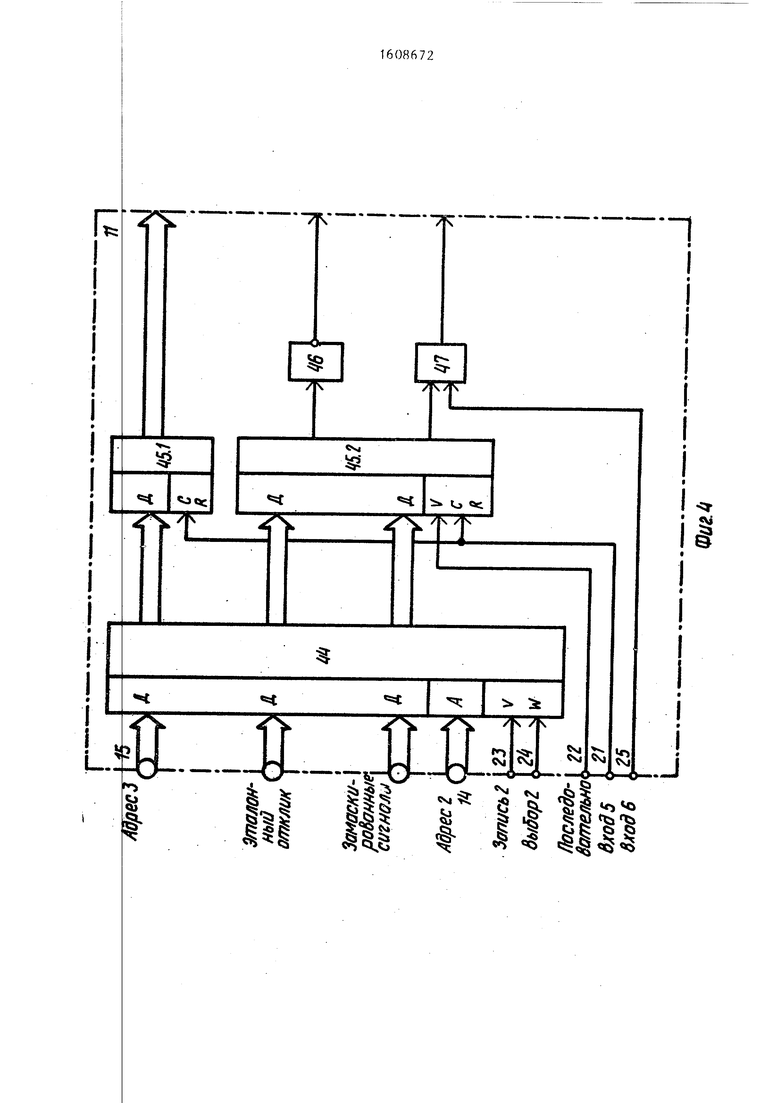

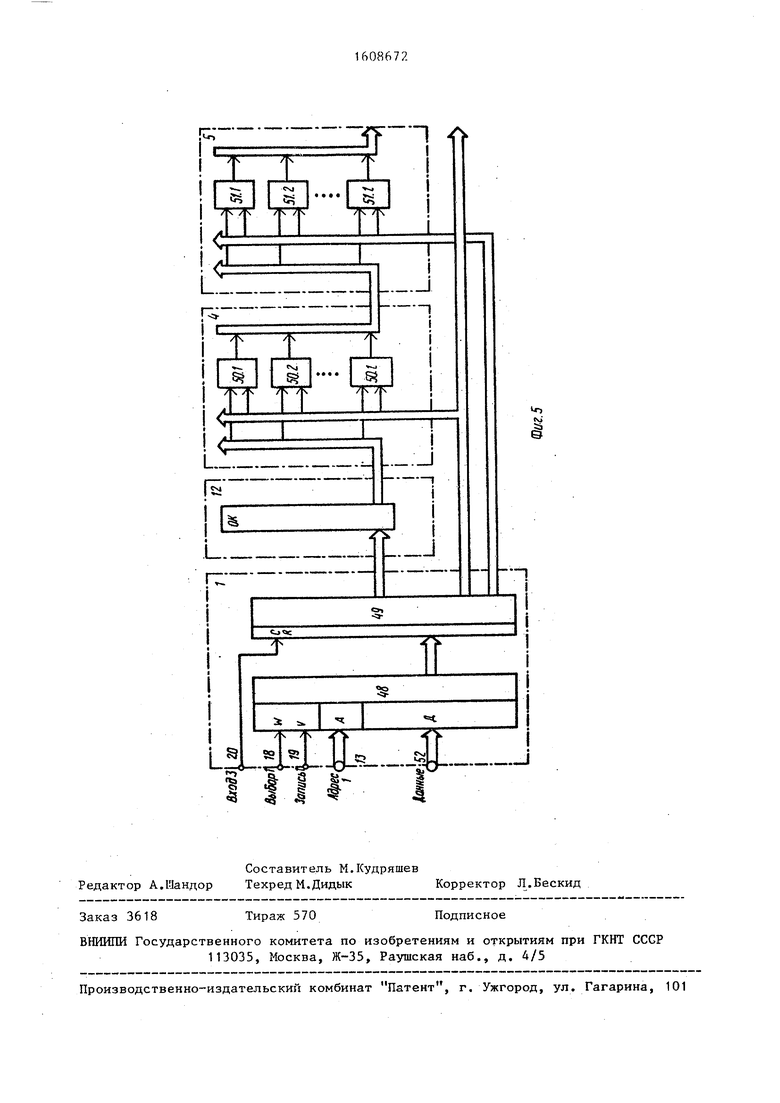

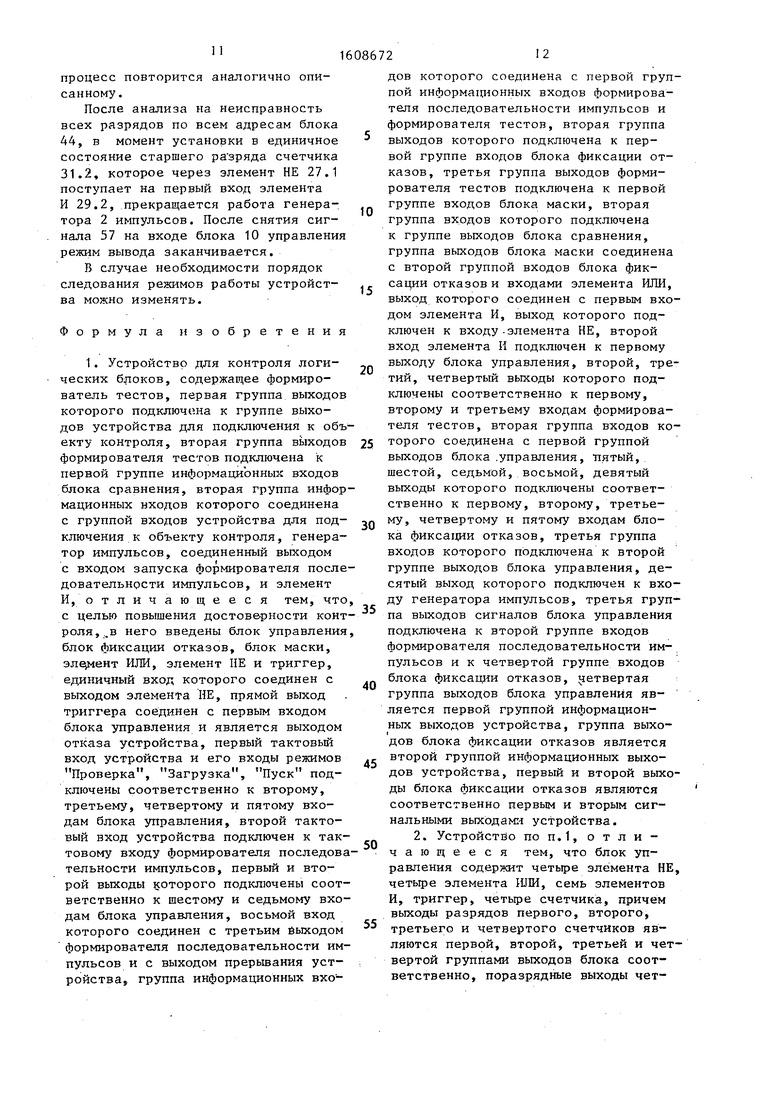

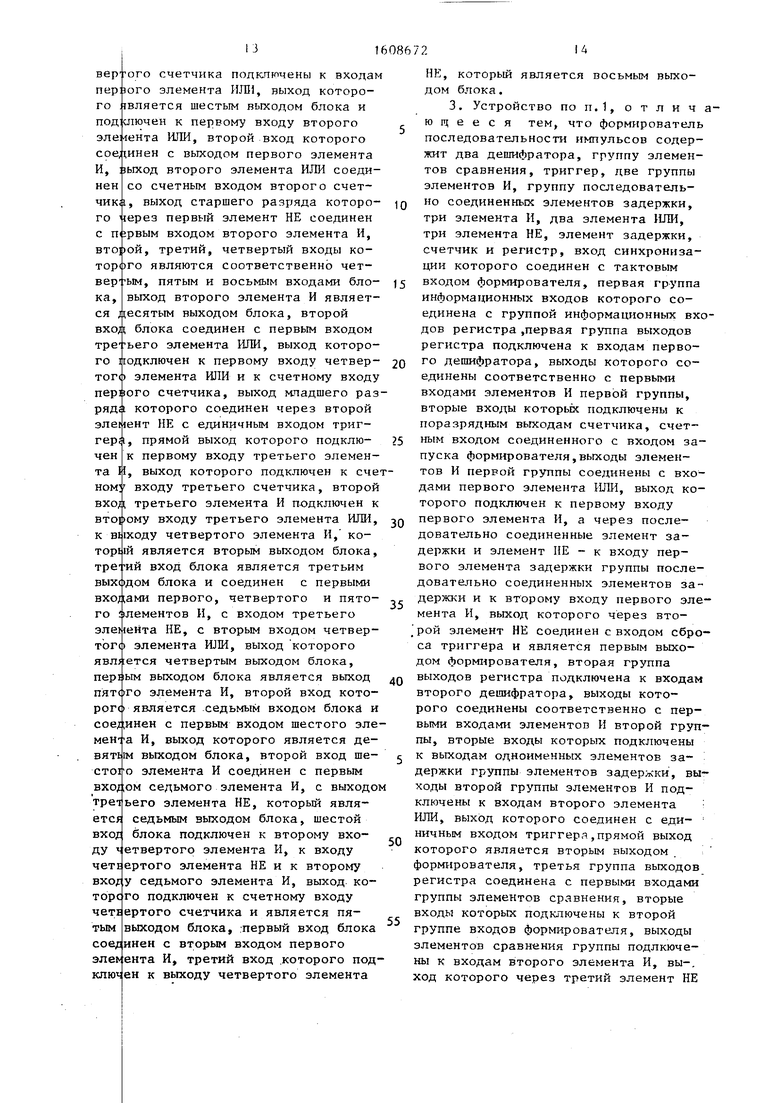

достоверности контроля. 1а фиг.1 приведена блок-схема юйства для контроля логических :ов; на Лиг.2 - функциональная схеустбло

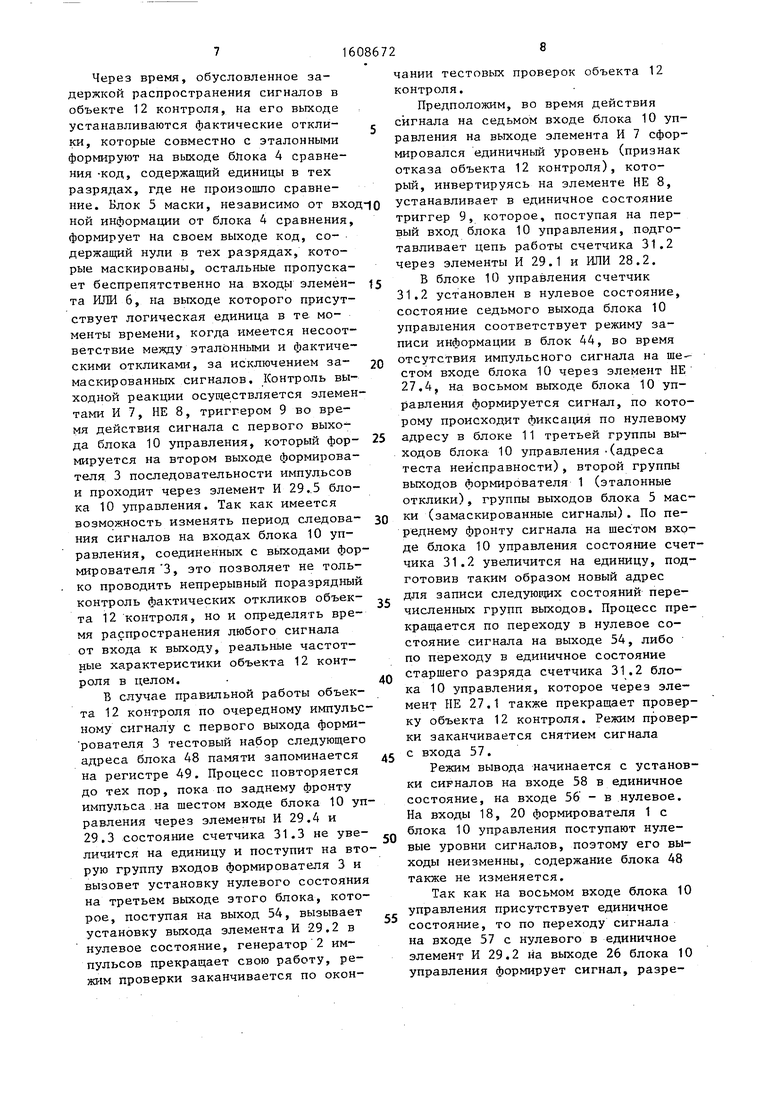

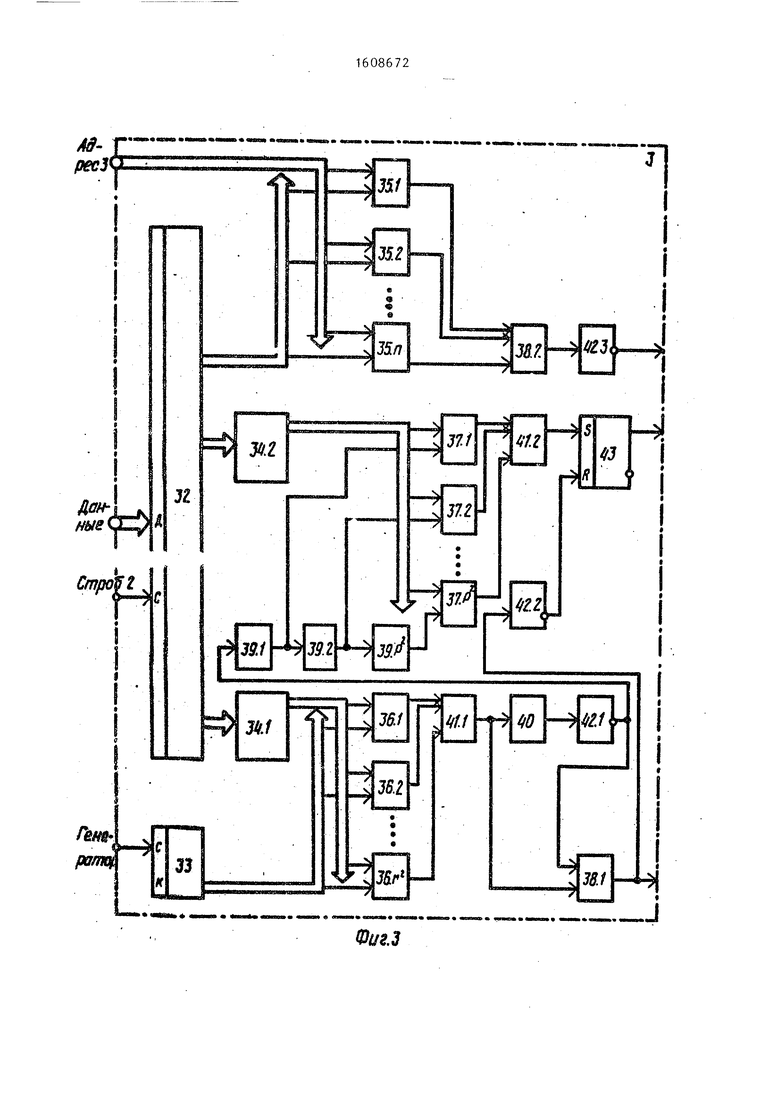

ма (шока управления; на фиг.З - функциональная схема формирователя после- тельности импульсов; на фиг.4 дов;фун1

ОТКс

:циональная схема блока фиксации зов; на фиг.5 - функциональные

схемы формирователя тестов, блока

cpai

нения,, олока маски.

Устройство содержит формирователь 1 тестов, генератор 2 импульсов,формирователь 3 последовательности импульсов, блок 4 сравнения, блок 5 маски, злемент ИЛИ 6, элемент И 7, элемент НЕ 8, триггер 9, блок 10 управления, блок 11 фиксации отказов, объект 12 контроля, группы выходов 13-16 блока 10, выходы 17-26 блока 10.

Блок З правления (фиг.2) содержит элементы НЕ 27, с первого по четвертый элементы ИЛИ 28, элементы И 29, триггер 30, счетчики 31.

Форм1фователь последовател-ьностк импульсов (фиг.З) содержит регистр

СЮ

о: ю

316

32, счетчик 33, дешифратор 34, элементы 35 сравнения, элементы И 36, элементы И 37, элементы И 38, элементы 39 и 40 задержки, элементы ШШ 41, элементы НЕ 42 и триггер 43,Блок фиксации отказов (фиг.4) содержит блок 44 памяти, регистры 45, элемент НЕ 46 и элемент И 47,

Формирователь тестовых сигналов (фиг.5) содержит блок 48 памяти, регистр 49.

Блок сравнения (фиг.5) содержит элементы 50 сравнения.

Блок маски (фиг.5) содержит элементы И 51 .

Устройство (фиг.1) .содержит также группу информационных входов 52 устройства, тактовый вход 53 устройства выход 54 прерьгоания устройства, тактовый вход 55 устройства, вход 56 режима проверки устройства, вход 57

режима Пуск устройства, вход 58 режима Загрузка устройства, выход 59 отказа устройства, группу 60 информационных выходов устройства, группу информационных выходов 61 устройства, сигнальный выход 62 устройства, сигнальный выход 63 устройства.

Устройство работает следующим образом.

После записи в формирователь 1 программы проверки, в формирователь 3 последовательности импульсов времени смены тестовых сигналов и времени начала непрерывного контроля вы ХОДНЫ55 реакций объекта 12 контроля в каждом тесте, блок 10 управления формирует начальный номер теста и включает генератор 2 импульсов. Формируется тестовое воздействие формирователем 1 тестов, анализируется выходная реакция проверяемого логического блока, если отказа нет изменяется номер теста и формируется но- вое тестовое воздействие. После окончания программы проверки при отсутствии отказа индицируется Годен.

В случае появления отказа в блоке 11 фиксации отказов записываются текущий и все последуюпще Адрес тес та, Эталонные отклики, Замаскированные сигналы, при этом увеличения времени смены тестовых сигналов не происходит. Это дает возможность продолжать проверку на заранйе за- данной частоте.

После окончания программы проверк блок 10 управления формирует началь

ный адрес теста неисправности, начальный адрес неисправности (номер контакта) и включает генератор 2 импульсов. В блоке 11 фикса1щи отказов формируется слово отказа, состоящее из адреса теста, эталонного отклика и замаскированных сигналов. При наличии признака Неисправность на устройство вывода выводятся полные дан- ные - адрес теста неисправности, состояние цепи неисправности, адрес неисправности,в противном случае фор5

0

5

0

5

0

I

мируется новый адр.ес неисправности, процесс повторяется. После анализа всех адресов неисправности формируется новый адрес теста неисправности, анализируются все адреса неисправностей. Работа заканчивается после исчерпания всех адресов тестов неисправностей с индикацией Отказ.

Устройство имеет три режима работы: загрузка, проверка, вывод. Для указанных режимов работы установлен следующий -приоритет: режим загрузки обладает высшим приоритетом, затем режим проверки и режим вывода. Режимы включаются сигналами, поступающими на входы 58 и 56. Нулевое состояние сигнала на входе 57 устанавливает . устройство в исходное положение (является сигналом сброса счетчиков и регистров).

Работа начинается с режима загрузки, для этого устанавливаются сигналы на входах 58 и 56 в нулевое состояние, а сигнал на входе 57 - в единичное. По импульсному сигналу на входе 53 в регистр 32 формирователя 3 записывается информационное слово с входов 52. Так как в блоке 10 управления счетчик 31.1 установлен в нулевое состояние, состояние выхода 19 блока 10 соответствует режиму записи информации в блок 48, то во время действия импульсного сигнала на входе 55 через элементы ИЛИ 28.3 и 28.4 на выходе 18 блока 10 формируется сигнал, по которому происходит фиксация по нулевому адресу в блоке 48 формирователя 1 тестов очередного информационного слова с входов 52. По окончании сигнала на входе 55 состояние счетчика 31.1 увеличивается на единицу, подготовив таким образом новый адрес для записи следующего информационного слова. Процесс повторяется пока не исчерпа5

ют(1я данные. Режим загрузки заканчива«

57

вы

стс

26

сиг|нал

ра

пульсов

пае т

16

т.ся снятием сигнала с входа 57. Режим проверки начинается с устасигналов на входах 58, 56 и в единичное состояние. Так как на соде 54 присутствует единичное со- яние, элемент И 2У.2 на выходе блока 10 управления формирует

, разрешающий работу генерато2импульсов. С выхода последнего нег рерывная последовательность имфиксированного периода посту- на счетный вход счетчика 33 формирователя 3.

С последовательности импульсов сированного периода на счетном

счетчика 33 формируются на его поразрядных выходах соответствующие постедовательности -импульсов с уве- {ваюпщмися периодами. Последова-. ность импульсов с необходимым периодом следования,, который опре- ется состоянием первой группы щов регистра 32 и соответствую- -выходом дешифратора 34.1, прохо- через один из группы элементов , через элемент ИЛИ 41.1. Гереход сигнала на выходе элемен41.1 в единичное состояние вает аналогичный переход сигнала 1|ыходе элемента И.38.1, который

3инвертор 42.2 устанавливает триггера 43 в нулевое состояЧерез время, определяемое эле40 задержки, на вькоде эле- ИЕ 42.1 установится нулевое со- хоторое поступает на вход И 38.1, на выходе которого е устанавливается нулевое состо- , а на входе сброса триггера единичное, триггер подготовлен аботы по единичному входу. Кро- гого, нулевое состояние с выхо- гемента НЕ 42.1 поступает на первого элемента группы после- ельно соединенных элементов задержки, которое через время,

параметрами группы эле- ентАв задержки, смещается к выходу оследнего элемента группы. Сигнал ого уровня, необходимое время которого определяется со- второй группы выходов реги- 32 и соответствующим выходом ешифратора 34.2, проходит через один группы элементов И 37, через элеИПИ 41.2 и вызывает установку риггера 43 в единичное состояние.

фик

Bxonie

лич

тел

дел:

ВЬГХ(

щим

ДИТ

и 3(

та ИШ

вызь

на

черб

выхс д

ние,

ментом

мента

стояние

элемента

такж

ние

3 ля

е э

а 3.

ход

оза

9

пределяемое

уле аде жки тоянием тра

з

ент

1608672

Таким образом, на первом выходе формироватаня 3 последовательности импульсов фopмIipyютcя импульсные сиг- палы фиксированной длительности с управляемым периодом следования, а на втором выходе - с таким же периодом следования, начало единичного состояния программно управляемо, окончание действия импульса происходит по началу единичного состояния на первом выходе формирователя 3 последовательности импульсов. На третьем вькоде формирователя 3 последовательности импульсов нулевое состояние будет тогда, когда состояние группы входов 15 формирователя 3 будет поразрядно соответствовать состоянию третьей группы выходов регистра 32.

25

30

35

Единичное состояние сигнала на входе 56 совместно с нулевым состоянием счетчика 31.1 блока 10 вызывает установку на выходах блока 48 памяти сигналов тестового набора по нулевому адресу, который по импульсному сигналу с первого выхода формирователя 3 последовательности импульсов, поступающему через элемент И 29,4 на син- хронизирую1гд{й вход регистра 49, запо- fинaeтcя на указанном регистре. На первой группе выходов формирователя 1 устанавливаются входные воздействия на объект 12 контроля, на второй группе выходов - эталонные отклики выходных сигналов объекта 12 контроля, на третьей группе выходов - замаскиро- - ванные сигналы. По окончании первого 4Q импульсного сигнала на шестом входе блока 10 через элементы И 29.4, ИЛИ 28.3 счетчик 31.Г увеличивает свое состояние на единицу - блок 48 памяти начинает выборку нового тес- 5 тового набора по следующему адресу, кроме этого, переход младшего разряда счетчика 31.1 в единичное состояние приводит к установке триггера 30 в единичное состояние - под- 0 готавливается цепь работы счетчика 31.3. Так как в дальнейшем цепи синхронизации счетчиков 31.1, 31.3 управляются по сигналу с выхода элемента И 29.4, то состояние счетчи- 5 ка 31.3 будет меньше на единицу счетчика 31.1. Состояние счетчика.31.3 свидетельствует о текущем адресе теста, состояние счетчика 31.1 - о следующем адресе теста.

Через время, обусловленное заержкой распространения сигналов в объекте 12 контроля, на его выходе устанавливаются фактические откли- j ки, которые совместно с эталонными формируют на выходе блока 4 сравнения -код, содержащий единицы в тех разрядах, где не произошло сравнение. Блок 5 маски, независимо от вход-|0 ной информации от блока 4 сравнения, формирует на своем выходе код, содержащий нули в тех разрядах, которые маскированы, остальные пропускает беспрепятственно на входы элемен- 15 та ИЛИ 6, на выходе которого присутствует логическая единица в те моменты времени, когда имеется несоответствие между эталонными и б.)актиче- скими откликами, за исключением за- 20 маскированных сигналов. Контроль выходной реакции осуществляется элементами И 7, НЕ 8, триггером 9 во время действия сигнала с первого выхо-- да блока 10 управления, который фор- 25 мируется на втором выходе формирователя 3 последовательности импульсов и проходит через элемент И 29..5 блока 10 управления. Так как имеется возможность изменять период следова- ЗО ния сигналов на входах блока 10 уп- равления, соединенных с выходами формирователя 3, это позволяет не только проводить непрерывный поразрядный контроль фактических откликов объек- та 12 контроля, но и определять время распространения любого сигнала от входа к выходу, реальные частотные характеристики объекта 12 контроля в целом. 40

В случае правильной работы объек- та 12 контроля по очередному импульсному сигналу с первого выхода форми- рователя 3 тестовый набор следующего адреса блока 48 памяти запоминается 45 на регистре 49. Процесс повторяется до тех пор, пока по заднему фронту импульса на шестом входе блока 10 управления через элементы И 29.4 и 29.3 состояние счетчика 31.3 не уве- д личится на единицу и поступит на вторую группу входов формирователя 3 и вызовет установку нулевого состояния на третьем выходе этого блока, которое, поступая на выход 54, вызывает установку выхода элемента И 29.2 в нулевое состояние, генератор 2 импульсов прекращает свою работу, режим проверки заканчивается по окон

чании тестовых проверок объекта 12 контроля.

Предположим, во время действия сигнала на седьмом входе блока 10 управления на выходе элемента И 7 сформировался единичный уровень (признак отказа объекта 12 контроля), который, инвертируясь на элементе НЕ 8, устанавливает в единичное состояние триггер 9, которое, поступая на первый вход блока 10 управления, подготавливает цепь работы счетчика 31.2 через элементы И 29.1 и ИЛИ 28.2. В блоке 10 управления счетчик 31.2 установлен в нулевое состояние, состояние седьмого выхода блока 10 управления соответствует режиму записи информации в блок 44, во время отсутствия импульсного сигнала на шестом входе блока 10 через элемент НЕ 27.4, на восьмом выходе блока 10 управления формируется сигнал, по которому происходит фиксация по нулевому адресу в блоке 11 третьей группы выходов блока 10 управления .(адреса теста неисправности), второй группы выходов формирователя 1 (эталонные отклики), группы выходов блока 5 маски (замаскированные сигналы). По переднему фронту сигнала на шестом входе блока 10 управления состояние счечика 31.2 увеличится на единицу, подготовив таким образом новый адрес для записи следующих состояний перечисленных групп выходов. Процесс прекращается по переходу в нулевое состояние сигнала на выходе 54, либо по переходу в единичное состояние старшего разряда счетчика 31.2 блока 10 управления, которое через элемент НЕ 27.1 также прекращает проверку объекта 12 контроля. Режим проверки заканчивается снятием сигнала с входа 57.

Режим вывода начинается с установки сигналов на входе 58 в единичное состояние, на входе 56 - в нулевое. На входы 18, 20 формирователя 1 с блока 10 управления поступают нулевые уровни сигналов, поэтому его выходы неизменны, содержание блока 48 также не изменяется.

Так как на восьмом входе блока 10 управления присутствует единичное состояние, то по переходу сигнала на входе 57 с нулевого в единичное элемент И 29.2 на выходе 26 блока 10 управления формирует сигнал, разре

шаю|ц1тй работу генератора 2 импульсо С вычода генератора 2 импульсов непрерывная последовательность импульсов (зиксированного периода поступае на в:сод запуска форм фователя 3, на первом и втором выходах которого формируются две последовательности импульсов.

В связи с тем, что до подачи сиг нала с входа 57 в блок 10 счетчик 31.2 установлен в нулевое состояние состояние выхода 23 блока 10 управлния (оответствует режиму чтения ин- формсНИИ из блока 44, на выходе 24 этогс же блока присутствует сигнал, разр шаюрщй выборку информации из блокс 44, счетчик 31.4 установлен в нулеюе состояние, которое на выход элемента ИЛИ 28.1 формирует нулевое состаяние сигнала, что соответствуе режиму записи информа регистр 45.2 (регистр 45.1 по в режиме параллельной запис после подачи сигнала на вход переднему фронту импульсного

на шестом входе блока 10, к проходит через элемент И 29.7 ход 21 и далее на первый вход 11, информация с выхода блока нулевому адресу фиксируется ре|гистрах 45.1 и 45.2. По задне- фронту импульсного сигнала на ше входе блока 10 состояние счет- 31.4 увеличится на единицу, на элемента ИЛИ 28.1 установит- едйничное состояние, которое со- ствует последовательному режи- информации в регистр 45.2 записанной информации) и со- до момента обнуления счет- 31.4. Состояние группы выходов гра 45.1, которые являются груп в jixoAOB блока 11 фиксации отка- го соответствует Адресу теста

, состояние группы вы- счетчика 31.4, которые являют- гвертой группой выходов блока , что соответствует

парал лельному

ции в

стояино

поэтому

57 по

сигна|ла

торьй

на вь

блока

44 по

на

му ф

стом

чика

выходу

ся

ответ

му

(сдви|г

за тиси

храни)гся

чика

регис

пой

зов ,ч

неисп авности

ходов

ся че

10

Адре

ВЫХОД

ется соотв правя стве

ПуЛЬС

блока

управления,

;у неисправности, состояние

элемента НЕ 46, который явля- :1ервым выходом блока 11, что гтствует состоянию цепи неис- )сти, зафиксируются на устрой- : Ывода. В случае, если им- 1ЫЙ сигнал на седьмом входе 10 управления проходит через И 29.6 на выход 25 этого же блока и далее на пятый вход блока 11

15

20

086

.Q , 25

30

35

40

45

0

5

2 10

фирссапии отказе и на нпч рсч г пход элемента И ч7, на выходе последнего, который является вторым ныходом блока 11 фиксации отказов, будет единичное состояние, что соотпегстпует признаку Неисправность. Единичное состояин-е на первом входе элемента И 47 с второго выхода регистра 45,2 будет тогда, когда в данном разряде группы замаскированных сигналов присутствует высокий уровень, что соответствует несраннившемуся разряду с объекта 12 контроля.

По очередному импульсному сигналу на шестом входе блока 10 управления регистр 45.2 сдвинет информацию на один разряд, подготовив к анализу на неисправность состояние очередного разряда из группы замаскированных сигналов, счетчик 31.4 соответственно также увеличит свое состояние на единицу. Процесс анализа на неисправность, фиксация на устройстве вывода несравнившихся разрядов объекта 12 контроля для данного адреса теста будет продолжаться до момента переполнения счетчика 31,4 (за это время пройдут анализ все или кроме последнего выходные сигналы объекта 12 контроля). По переднему фронту очередного импульсного сигнала на шестом входе блока 10 управления регистр 45.2 сдвинет информацию на один разряд, подготовив к анализу на неисправность состояние очередного разряда. По заднему фронту этого сигнала счетчик 31.4 установится в нулевое состояние, через элементы ИЛИ 28.1 и 28.2 отрицательный перепад увеличит состояние счетчика 31.2 на единицу, начнется выборка информации с очередного адреса оперативного запоминающего устройства 44, кроме этого, на выходе 22 блока 10 управления установится нулевое состояние, что соответствует параллельному режиму работы регистра 45.2.

По импульсному сигналу на седьмом входе блока 10 управления произойдет анализ на элементе И 47 нэ неисправность очередного разряда.

По переднему фронту импульсного сигнала.на шестом входе блока 10 управления илфармагщя с выхода блока 44 по очередному адресу зафиксируется на регистрах 45.1 и 45.2. Далее

процесс повторится аналогично описанному.

После анализа на неисправность всех разрядов по всем адресам блока 44, в момент установки в единичное состояние старшего ра зряда счетчика 31.2, которое через элемент НЕ 27.1 поступает на первый вход элемента И 29.2, прекращается работа генератора 2 импульсов. После снятия сигнала 57 на входе блока 10 управления режим вывода заканчивается.

В случае необходимости порядок следования режимов работы устройства можно изменять.

Формула изобретения

1. Устройство для контроля логических блоков, содержащее формирователь тестов, первая группа выходов которого подключена к группе выходов устройства для подключения к объекту контроля, вторая группа выходов формирователя тестов подключена к первой группе информационных входов блока сравнения, вторая группа информационных входов которого соединена с группой входов устройства для подключения к объекту контроля, генератор импульсов, соединенный выходом с входом запуска формирователя последовательности импульсов, и элемент И, отличающееся тем, что с целью повышения достоверности контроля,.,в него введены блок управления блок фиксации отказов, блок маски, ИЛИ, элемент НЕ и триггер, единичный вход которого соединен с выходом элемента НЕ, прямой выход триггера соединен с первым входом блока управления и является выходом отказа устройства, первый тактовый вход устройства и его входы режимов Проверка, Загрузка, Пуск подключены соответственно к второму, третьему, четвертому и пятому входам блока управления, второй тактовый вход устройства подключен к тактовому входу формирователя последовательности импульсов, первый и второй выходы которого подключены соответственно к шестому и седьмому входам блока управления, восьмой вход которого соединен с третьим выходом формирователя последовательности импульсов и с выходом прерывания устройства, группа информационных вхо0

5

0

5

0

5

0

5

0

5

дов которого соединена с первой группой информа1щонных входов формирователя последовательности импульсов и формирователя тестов, вторая группа выходов которого подключена к первой группе входов блока фиксации отказов, третья группа выходов формирователя тестов подключена к первой группе входов блока маски, вторая группа входов которого подключена к группе выходов блока сравнения, группа выходов блока маски соединена с второй группой входов блока фиксации отказов и входами элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которого подключен к входу-элемента НЕ, второй вход элемента И подключен к первому выходу блока управления, второй, третий, четвертый выходы которого подключены соответственно к первому, второму и третьему входам формирователя тестов, вторая группа входов которого соединена с первой группой выходов блока .управления, пятый, шестой, седьмой, восьмой, девятый выходы которого подключены соответственно к первому, второму, третьему, четвертому и пятому входам блока фиксатщи отказов, третья группа входов которого подключена к второй группе выходов блока управления, десятый выход которого подключен к входу генератора импульсов, третья группа выходов сигналов блока управления подключена к второй группе входов формирователя последовательности импульсов и к четвертой группе входов блока фиксации отказов, уетвертая группа выходов блока управления яв- ляется первой группой информационных выходов устройства, группа выходов блока фиксации отказов является второй группой информационных выходов устройства, первый и второй выходы блока фиксации отказов являются соответственно первым и вторым сигнальными выходами устройства.

2. Устройство по П.1, отличающееся тем, что блок управления содержит четыре элемента НЕ, четыре элемента ИЛИ, семь элементов И, триггер, четьфе счетчика, причем выходы разрядов первого, второго, третьего и четвертого счетчиков являются первой, второй, третьей и четвертой группами выходов блока соответственно, поразрядные выходы четверного счетчика подключены к входа пер:юго элемента ШВ1, выход которо- 1вляется шестым выходом блока и шючен к первому входу второго ИЛИ, второй вход которого с выходом первого элемента :)ыход второго элемента ИЛИ соеди со счетным входом второго счет- выход старшего разряда которо шрез первый элемент НЕ соединен П фвым входом второго элемента И, , третий, четвертый входы ко- Topibro являются соответственно четго . под: элеиента соед1инен

И,

нен

чики

го

с

ВТ

вер ка, ся

тре го

ым, пятым и восьмым входами бло- выход второго элемента И являет- фесятым выходом блока, второй

блока соединен с первым входом ьего элемента ИЛИ, выход которо- йодключен к первому входу четвер- того элемента ИЛИ и к счетному входу парного счетчика, выход младшего разряда которого соединен через второй элемент НЕ с единичным входом триггера, прямой выход которого подклю- чен к первому входу третьего элемента И, выход которого подключен к сченому входу третьего счетчика, второй вход третьего элемента И подключен к второму входу третьего элемента ИЛИ, к внходу четвертого элемента И, ко- торий является вторым выходом блока, вход блока является третьим выходом блока и соединен с первыми входами первого, четвертого и пятого элементов И, с входом третьего элемента НЕ, с вторым входом четвертого элемента ШШ, выход которого четвертым выходом блока, nepi ым выходом блока является выход пятого элемента И, второй вход которого является седьмым входом блока и сое;;инен с первым входом шестого эле И, выход которого является девятым выходом блока, второй вход шестого элемента И соединен с первым вxo,cм седьмого элемента И, с выходо третьего элемента НЕ, который является седьмым выходом блока, шестой Bxof блока подключен к второму входу ;етвертого элемента И, к входу четЕертого элемента НЕ и к второму BXOfу седьмого элемента И, выход ко- торс го подключен к счетному входу четвертого счетчика и является пятым выходом блока, .первый вход блока сое; инея с вторым входом первого злекента И, третий вход .которого под- к выходу четвертого элемента

10

35

15

20 5 -jg

40

50

5

НЕ, который является восьмым выходом блока.

3. Устройство по П.1, отличающееся тем, что формирователь последовательности импульсов содержит два дешифратора, группу элементов сравнения, триггер, две группы элементов И, группу последовательно соединенных элементов задержки, три элемента И, два элемента ИЛИ, три элемента НЕ, элемент задержки, счетчик и регистр, вход синхронизации которого соединен с тактовым входом формирователя, первая группа информационных входов которого соединена с группой информационных входов регистра ,первая группа выходов регистра подключена к входам первого дешифратора, выходы которого соединены соответственно с первыми входами элементов И первой группы, вторые входы которьЁх подключены к поразрядным выходам счетчика, счетным входом соединенного с входом запуска формгфователя,выходы элементов И первой группы соединены с входами первого элемента ИЛИ, выход которого подключен к первому входу первого элемента И, а через последовательно соединенные элемент задержки и элемент НЕ - к входу первого элемента задержки группы последовательно соединенных элементов задержки и к второму входу первого элемента И, выход которого через вто- рой элемент НЕ соединен с входом сброса триггера и является первым выходом формирователя, вторая группа выходов регистра подключена к входам второго дешифратора, выходы которого соединены соответственно с первыми входами элементов И второй группы, вторые входы которых подключены к выходам одноименных элементов за- держки группы элементов задерлски, выходы второй группы элементов И подключены к входам второго элемента ИЛИ, выход которого соединен с еди- ничным входом триггера,прямой выход которого является вторым выходом . формирователя, третья группа выходов регистра соединена с первыми входами группы элементов сравнения, вторые входы которых подключены к второй группе входов формирователя, выходы элементов сравнения группы подлкюче- ны к входам второго элемента И, вы-, ход которого через третий элемент НЕ

соединен с третьим выходом формирователя.

I I

4. Устройство по п.1, о т л и - ч а ю 14 е е с я тем, что блок фик- сагдии отказов содержит регистр,сдвиговый регистр, элемент И, элемент НЕ и блок памяти, три группы информационных входов которого соединены соответственно с первой, второй и четвертой группами входов блока, третья группа входов которого соединена с группой адресных входов блока памяти, входы-выходы записи и чтения которого соединены соответственно с третьим и четвертым входами блока, первая группа выходов блока памяти

подключена к группе информационных входов регистра, выходы которого являются группой выходов блока, вторая и третья группы выходов блока памяти соединены с первой и второй группами информационных входов сдвигового регистра, управляющий вход которого подключен к второму входу блока,вход

синхронизации регистров подключен к первому входу блока, первый выход сдвигового регистра соединен через элемент НЕ с первым выходом блока, второй выход сдвигового регистра соединен с первым входом элемента И, второй вход которого подключен к пятому входу блока, выход элемента И является вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блока памяти | 1981 |

|

SU1040525A2 |

| Устройство для контроля блока памяти | 1983 |

|

SU1137539A2 |

| Устройство для контроля логических блоков | 1981 |

|

SU1016786A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1262575A1 |

| Устройство для имитации отказов дискретной аппаратуры | 1990 |

|

SU1815642A1 |

| Устройство для контроля внешних абонентов вычислительных комплексов | 1982 |

|

SU1062710A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1108511A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для тестового контроля логических блоков. Целью изобретения является повышение достоверности контроля. Устройство содержит формирователь тестов, генератор импульсов, формирователь последовательности импульсов, блок сравнения, блок маски, элементы ИЛИ, НЕ, триггер, блок управления и блок фиксации отказов. В устройстве увеличена информативность от адресе цели неисправности и состояния цепи неисправности, увеличена гибкость за счет исключения из анализа на неисправность любого из выходных сигналов объекта контроля. В случае появления отказа процесс проверки происходит непрерывно без останова устройства. Повышена достоверность контроля за счет непрерывного контроля выходных сигналов объекта контроля в течение заданного времени для данного теста. 3 з.п. ф-лы, 5 ил.

Фи.г.г

/ft. ГЦ; ресЗуи.и.

I

Mff/f- ные

зг

flffm

f-$

35

J5/

Л

« в

1

Редактор А.Шандор

Составитель М.Кудряшев

Техред М.Дидык Корректор Л.Бескид

Заказ 3618

Тираж 570

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

lo

Подписное

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Бкш | |||

| Зубчатое колесо со сменным зубчатым ободом | 1922 |

|

SU43A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-23—Публикация

1988-06-17—Подача