(54) УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ОДНОКРАТНЫХ

СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации однократных сигналов | 1980 |

|

SU983742A1 |

| Устройство для регистрации однократных сигналов | 1980 |

|

SU983741A1 |

| Способ и устройство регистрации формы однократных электрических сигналов | 1981 |

|

SU983584A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для преобразования сейсмической информации | 1981 |

|

SU1038904A1 |

| Устройство для анализа распределений случайных процессов | 1985 |

|

SU1247896A1 |

| Устройство для измерения перемещений | 1986 |

|

SU1357695A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для обработки графической информации | 1988 |

|

SU1674222A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для исследования однократных сигналов.

Известно устройство для регистрации однократных сигналов, содержащее аналого-цифровой преобразователь, блок квантования, генератор импульсов, счетчик, блок управления и блок памяти С1 .

Недостатком этого устройства является низкая точность регистрации,

Наиболее близким техническим решением к предлагаемому является устройство для регистрации однократных сигналов, содержащее аналого-цифровой преобразователь, блок :свантования, блок памяти и блок управления 2.

Недостатком данного устройства является также низкая точность регистрации за счет потери высокочастотных составляющих между соседними отсчетами.

Цель изобретения - повышение точности устройства.

Поставленная цель достигается тем, что устройство для регистрации однократных сигналов, содержаи1ее блок квантования входного сигнала

по уровню, выход которого подключен к входу аналого-цифрового преобразователя, первый и второй выходы которого соединены с первым входом блока управления и информационным входом первого блока памяти соответственно, адресный и управляющий входы первого блока памяти подключены к илходу адресного блока и первому ai10ходу блока управления соответственно, а выход - к первому входу индикатора и генератор тактовых импульсов, первый выход которого подключен к счетному входу первого счет15чика, вход начальной установки которого соединен с входом начальной установки адресного блока и вторым выходом блока управления, а выход с вторым входом блока управления,

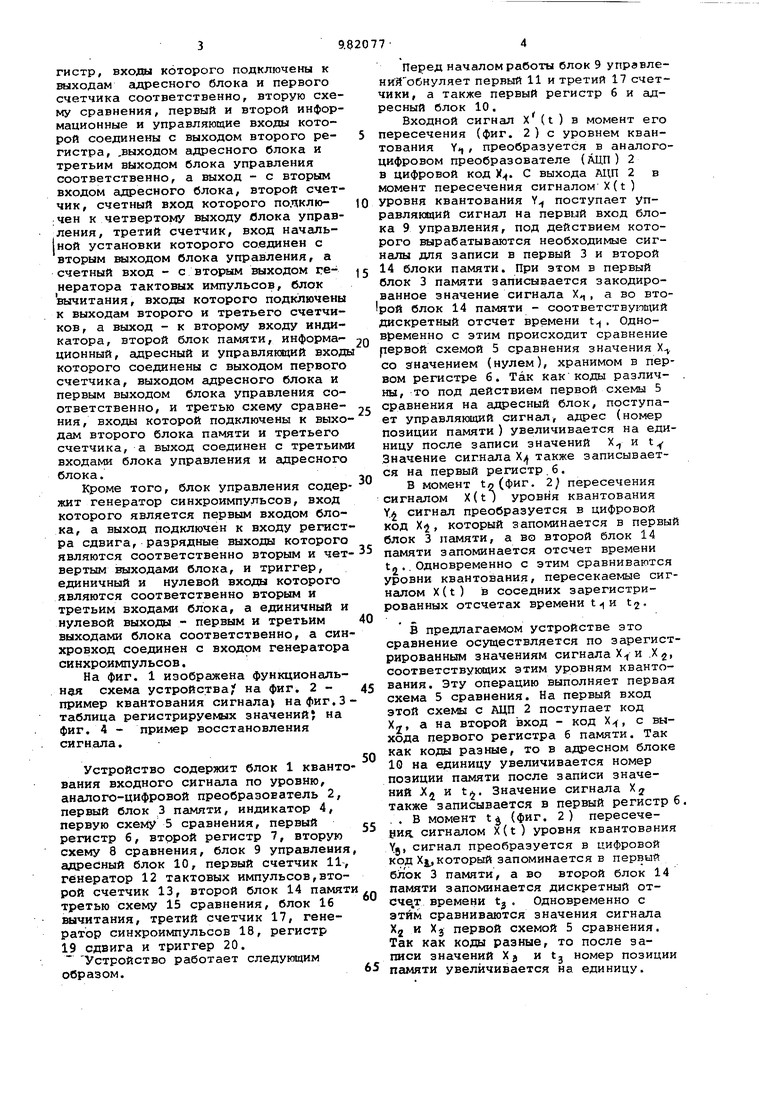

20 содержит первую схему сравнения, первый вход которой подключен к второму выходу аналого-цифрового преобразователя, а первый выход - к первому входу адресного блока, первый ре25гистр, информационный вход которого соединен с вторым выходом первой схема сравнения, вход начальной установки - с вторым выходом блока управления, а выход - с вторым входом 30 первой схемы сравнения, второй регистр, входы которого подключены к выходам адресного блока и первого счетчика соответственно, вторую схему сравнения, первый и второй информационные и управляющие входы которой соединены с выходом второго регистра, .выходом адресного блока и третьим выходом блока управления соответственно, а выход - с вторым входом адресного блока, второй счетчик, счетный вход которого полключен к четвертому выходу влока управления, третий счетчик, вход началь1ной установки которого соединен с вторым выходом блока управления, а счетный вход - с вторым выходом генератора тактовых импульсов, блок вычитания, входы которого подключены к выходам второго и третьего счетчиков, а выход - к второму входу индикатора, второй блок памяти, информационный, адресный и управляющий вход которого соединены с выходом первого счетчика, выходом адресного блока и первым выходом блока управления соответственно, и третью схему сравнения, входы которой подключены к выхо дам второго блока памяти и третьего счетчика, а выход соединен с третьим входами блока управления и адресного блока. Кроме того, блок управления содер жит генератор синхроимпульсов, вход которого является первым входом блока, а выход подключен к входу регист ра сдвига, разрядные выходы которого являются соответственно вторым и чет вертым выходами блока, и триггер, единичный и нулевой входы которого являются соответственно вторым и третьим входами блока, а единичный и нулевой выходы - первым и третьим выходами блока соответственно, а син хровход соединен с входом генератора синхроимпульсов. На фиг. 1 изображена функциональная схема устройства) на фиг. 2 пример квантования сигнала) на фиг.3 таблица регистрируемых значений} на фиг. 4 - пример восстановления сигнала. Устройство содержит блок 1 кванто вания входного сигнала по уровню, аналого-цифровой преобразователь 2, первый блок 3 памяти, индикатор 4, первую схему 5 сравнения, первый регистр б, втррой регистр 7, вторую схему 8 сравнения, блок 9 управления адресный блок 10, первый счетчик 11, генератор 12 тактовых импульсов,второй счетчик 13, второй блок 14 памят третью схему 15 сравнения, блок 16 вычитания, третий счетчик 17, генератор синхроимпульсов 18, регистр 19 сдвига и триггер 20. Устройство работает следующим образом. Перед началом работы блок 9 упрэвленийобнуляет первый 11 и третий 17 счетчики, а также первый регистр 6 и адресный блок 10. Входной сигнал х (t ) в момент его пересечения (фиг. 2 ) с уровнем квантования Yi, , преобразуется в аналогоцифровом преобразователе (АЦП) 2 в цифровой код Х. С выхода МЩ 2 в момент пересечения сигналом X(t) уровня квантования Y поступает управляющий сигнал на первый вход блока 9 управления, под действием которого вырабатываются необходимые сигналы для записи в первый 3 и второй 14 блоки памяти. При этом в первый блок 3 памяти записывается закодированное значение сигнала Х, , а во второй блок 14 памяти - соответствующий дискретный отсчет времени t. Однов эеменно с этим происходит сравнение рервой схемой 5 сравнения значения Х со значением (нулем), хранимом в первом регистре б. Так как коды различны, то под действием первой схемы 5 сравнения на адресный блок, поступает управлягаций сигнал, адрес (номер позиции памяти ) увеличивается на единицу после записи значений Х и t .Значение сигнала Х/( также записывается на первый регистр.б. В момент 1я(фиг, 2} пересечения сигналом X(t) уровня квантования У сигнал преобразуется в цифровой код Х, который запоминается в первый блок 3 памяти, а во второй блок 14 памяти запоминается отсчет времени tn.. Одновременно с этим сравниваются уровни квантования, пересекаемые сигналом X(t) в соседних зарегистрированных отсчетах времени tj. В предлагаемом устройстве это сравнение осуществляется по зарегистрированным значениям сигнала Х и .Х, соответствующих этим уровням квантования. Эту операцию выполняет первая схема 5 сравнения. На первый вход этой схемы с АЦП 2 поступает код Х,г, а на второй вход - код Х,, с выхода первого регистра 6 памяти. Так как коды разные, то в адресном блоке 10 на единицу увеличивается номер позиции памяти после записи значений /j и t,j. Значение сигнала Х,; также записывается в первый регистр б. . . В момент tj (фиг. 2) пересечееиц. сигналом X(t) уровня квантования Yj, сигнал преобразуется в цифровой код Xj,который запоминается в первый блок 3 памяти, а во второй блок 14 памяти запоминается дискретный отсче,т времени tj , Одновременно с этим сравниваются значения сигнала Xj и Xj первой схемой 5 сравнения. Так как коды разные, то после записи значений Xj и tj номер позиции памяти увеличивается на единицу.

Значение сигнала Xj записывается в первый регистр 6.

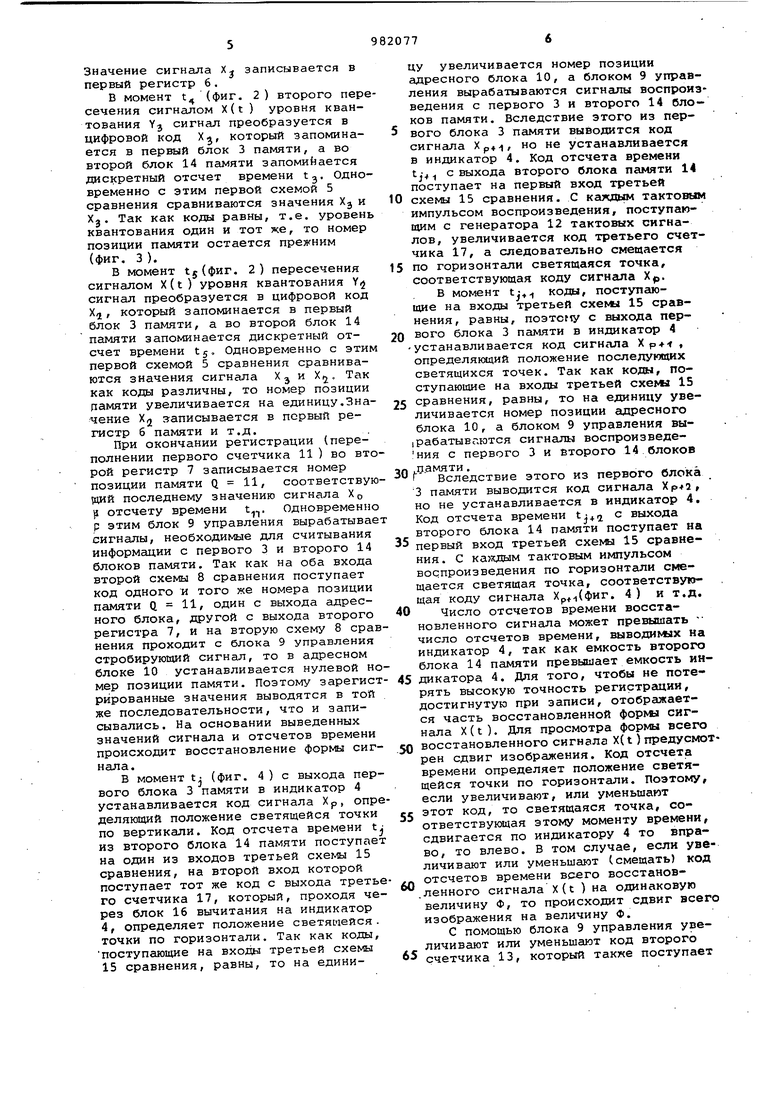

В момент t (фиг. 2 ) второго пересечения сигналом X(t ) уровня квантования Yj сигнал преобразуется в цифровой код Xj, который запоминается в первый блок 3 памяти, а во второй блок 14 памяти запомийается дискретный отсчет времени t. Одновременно с этим первой схемой 5 сравнения сравниваются значения Xj и Xj. Так как коды равны, т.е. уровень квантования один и тот же, то номер позиции памяти остается прежним (фиг. 3).

В момент 15(фиг. 2) пересечения сигналом X(t) уровня квантования Y сигнал преобразуется в цифровой код X,j, который запоминается в первый блок 3 памяти, а во второй блок 14 памяти запоминается дискретный отсчет времени t5 Одновременно с этим первой схемой 5 сравнения сравниваются значения сигнала Х и X,j,. Так как коды различны, то номер позиции памяти увеличивается на единицу.Значение Xj з аписывается в первый регистр б памяти и т.д.

При окончании регистрации (переполнении первого счетчика 11 ) во второй регистр 7 записывается номер позиции памяти Q 11, соответствующий последнему значению сигнала Хо J1 отсчету времени t. Одновременно р этим блок 9 управления вырабатывае сигналы, необходи1«ие для считывания информации с первого 3 и второго 14 блоков памяти. Так как на оба входа второй схемы 8 сравнения поступает код одного и того же номера позиции памяти Q 11, один с выхода адресного блока, другой с выхода второго регистра 7, и на вторую схему 8 сравнения проходит с блока 9 управления стробирующий сигнал, то в адресном блоке 10 устанавливается нулевой номер позиции памяти. Поэтому зарегистрированные значения выводятся в той же последовательности, что и записывались. На основании выведенных значений сигнала и отсчетов времени происходит восстановление формы сигнала.

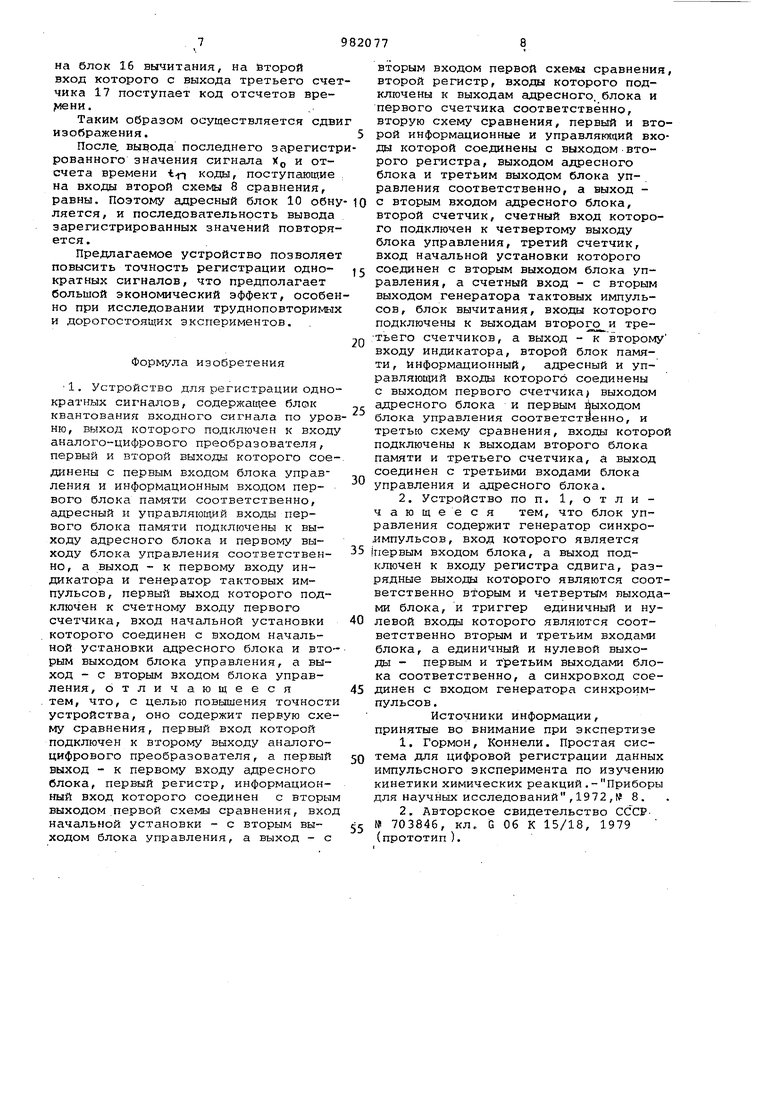

В момент t; (фиг. 4 ) с выхода первого блока 3 памяти в индикатор 4 устанавливается код сигнала Хр, определяющий положение светящейся точки по вертикали. Код отсчета времени tj из второго блока 14 памяти поступает на один из входов третьей схемы 15 сравнения, на второй вход которой поступает тот же код с выхода третьего счетчика 17, который, проходя через блок 16 вычитания на индикатор 4, определяет положение светящейся. точки по горизонтали. Так как коды, поступающие на входы третьей схемы 15 сравнения, равны, то на единицу увеличивается номер позиции адресного блока 10, а блоком 9 управления вырабатываются сигнгьпы воспроизведения с первого 3 и второго 14 блоков памяти. Вследствие этого из первого блока 3 памяти выводится код сигнала Хр+, но не устанавливается в индикатор 4. Код отсчета времени tj4i с выхода второго блока памяти 14 поступает на первый вход третьей

схемы 15 сравнения. С каждым тактовым импульсом воспроизведения, поступающим с генератора 12 тактовых сигналов, увеличивается код третьего счетчика 17, а следовательно смещается

по горизонтали светящаяся точка, соответствующая коду сигнала Х. в момент t: коды, поступающие на входы третьей схемы 15 сравнения, равны, поэтому с выхода первого блока 3 памяти в индикатор 4 устанавливается код сигнала X р , определяющий положение последующих светящихся точек. Так как коды, поступающие на входы третьей схемы 15

сравнения, равны, то на единицу увеличивается номер позиции адресного блока 10, а блоком 9 управления вырабатывг,ются сигналы воспроизведения с первого 3 и второго 14 блоков

памяти.

Вследствие этого из первого блока

3 памяти выводится код сигнала , о не устанавливается в индикатор 4, Код отсчета времени t.j + ,j с выхода второго блока 14 памяти поступает на

первый вход третьей схемы 15 сравнения. С каждым тактовым импульсом воспроизведения по горизонтали смеается светящая точка, соответствуюая коду сигнала Хр(фиг. 4) и т.д.

Число отсчетов времени восстановленного сигнсша может превышать исло отсчетов времени, выводимых на индикатор 4, так как емкость второго блока 14 памяти превышает емкость индикатора 4. Для того, чтобы не потерять высокую точность регистрации, достигнутую при записи, отображается часть восстановленной форкы сигнала X(t). Для просмотра формы всего

восстановленного сигнала Х( t) предусмотрен сдвиг изображения. Код отсчета времени определяет положение светящейся точки по горизонтали. Поэтому, если увеличивают, или уменьшают

этот код, то светящаяся точка, соответствующая этому моменту времени, сдвигается по индикатору 4 то вправо, то влево. В том случае, если увеличивают или уменьшают (смещать) код

отсчетов времени всего восстановленного сигнала X(t ) на одинаковую величину Ф, то происходит сдвиг всего изображения на величину Ф.

С помощью блока 9 управления увеличивают или уменьшают код второго

счетчика 13, который также поступает на блок 16 вычитания, на второй вход которого с выхода третьего сче чика 17 поступает кол отсчетов . Таким образом осуществляется сдв изображения. После, вывода последнего зарегист рованного значения сигнала Х(, и отсчета времени t коды, поступающие на входы второй схемы 8 сравнения, равны. Поэтому адресный блок 10 обн ляется, и последовательность вывода зарегистрированных значений повторя ется. Предлагаемое устройство позволяе повысить точность регистрации однократных сигналов, что предполагает большой экономический эффект, особе но при исследовании трудноповторимы и дорогостоящих экспериментов. Формула изобретения 1. Устройство для регистрации одно кратных сигналов, содержащее блок квантования вкодного сигнала по уро ню, выход которого подключен к вход аналого-цифрового преобразователя, первый и второй выходы которого сое динены с первым входом блока управления и информационным входом первого блока памяти соответственно, адресный и управляющий входы первого блока памяти подключены к выходу адресного блока и первому выходу блока управления соответственно, а выход - к первому входу индикатора и генератор тактовых импульсов , первый выход которого подключен к счетному входу первого счетчика, вход начальной установки которого соединен с входом начальной установки адресного блока и вто рым выходом блока управления, а выход - с вторым входом блока управления, отличающееся тем, что, с целью повышения точност устройства, оно содержит первую схе му сравнения, первый вход которой подключен к второму выходу аналогоцифрового преобразователя, а первый выход - к первому входу адресного блока, первый регистр, информационный вход которого соединен с вторы выходом первой схемы сравнения, вхо начальной установки - с вторым выходом блока управления, а выход - с вторым входом первой схемы сравнения, второй регистр, входы которого подключены к выходам адресного, блока и первого счетчика соответственно, вторую схему сравнения, первый и второй информационные и управляющий входы которой соединены с выходом-второго регистра, выходом адресного блока и третьим выходом блока управления соответственно, а выход с вторым входом адресного блока, второй счетчик, счетный вход которого подключен к четвертому выходу блока управления, третий счетчик, вход начальной установки которого соединен с вторым выходом блока управления, а счетный вход - с вторым выходом генератора тактовых импульсов, блок вычитания, входы которого подключены к выходам второго и третьего счетчиков, а выход - к второму входу индикатора, второй блок памяти, информационный, адресный и управляющий входы которого соединены с выходом первого счетчика) выходом адресного блока и первым йыходом блока управления соответственно, и третью схему сравнения, входы которой подключены к выходам второго блока памяти и третьего счетчика, а выход соединен с третьими входами блока управления и адресного блока. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит генератор синхроимпульсов , вход которого является 1Г1ервым входом блока, а выход подключен к входу регистра сдвига, разрядные выходы которого являются соответственно вторым и четвертом выходами блока, и триггер единичный и нулевой входы которого являются соответственно вторым и третьим входами блока, а единичный и нулевой выходы - первым и третьим выходами блока соответственно, а синхровход соединен с входом генератора синхроимпульсов . Источники информации, принятые во внимание при экспертизе 1.Гормон, Коннели. Простая система для цифровой регистрации данных импульсного эксперимента по изучению кинетики химических реакций .- Приборы для научных исследований ,1972 ,№ 8. 2.Авторское свидетельство СССР№ 703846, кл. G Об К 15/18, 1979 (прототип ).

+ --H

-if tg -Ц

Заг о/ инаютей и uffM /ffvafcfnfS

/I /. :-,...j 4 pY

.LJ,IJJJJXQJ X,

tgtfj in ifs

i

n

.2

Авторы

Даты

1982-12-15—Публикация

1980-11-06—Подача