(5) ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1681384A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Время-импульсный универсальный интегрирующий преобразователь напряжения с функцией широтно-импульсной модуляции | 2020 |

|

RU2731601C1 |

| Интегрирующий аналого-цифровой преобразователь | 1977 |

|

SU705672A2 |

| ВРЕМЯ-ИМПУЛЬСНЫЙ УНИВЕРСАЛЬНЫЙ ИНТЕГРИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 2018 |

|

RU2689805C1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1697265A1 |

| Интегрирующий аналого-цифровой преобразователь | 1981 |

|

SU982191A1 |

| Интегрирующий преобразователь постоянного напряжения в код | 1988 |

|

SU1672565A1 |

Изобретение относится к цифровой электроизмерительной технике. Известны интегрирующие АЦП с двух тактным интегрированием, осуществляю щие аналого-цифровое преобразование разнополярных напряжений с одним источником опорного напряжения и с запоминающей обратной связью для компенсации дрейфа усилителей устройства. Особенностью известных АЦП является запоминание на конденсаторах за поминающей обратной связи не только корректирующей поправки, но и всего опорного напряжения (или его части, соответствующей пределу измерения), которое в интервале двух тактов аналого-цифрового преобразования должно оставаться неизменным, так как его нестабильность вызывает нелинейную составляющую погрешности преобразова ния. Известны интегрирующие аналого-ци ровые преобразователи, в которых используется один источник опорного на пряжения, два запоминающих конденсатора , на одном из которых запоминается напряжение, компенсирующее дрейф усилителей устройства, а на другом напряжение UQ, близкое по абсолютному значению и обратное по полярности опорному напряжению, и результирующее напряжение дрейфа tl. Недостатком этих АЦП является большая погрешность, возникающая вследствие разряда запоминающего конденсатора через сопротивление изоляции между выводами конденсатора. Кроме того, в этих АЦП требуется дополнительное время для заряда второго запоминанмцего конденсатора, что снижает быстродействие АЦП. В них интегратор используется в биполярном режиме, которому свойственна нечувствительность в зоне нуля, вызываемая неопределенностью выходного напряжения нуль-органа, запаздыванием интегратора, нуль-органа и ключей, для устранения которой требуется дополнительное оборудование.

Наиболее близким к предлагаемому является аналого-цифровой преобразователь, содержащий коммутатор, первые входы которого соединены соответственно с входной шиной, с выходом источни ка опорного напряжения и с выходом де лителя опорного напряжения, а вторые входы - с входом интегратора, выполненного на операционном усилителе с конденсатором в цепи обратной связи, выход интегратора соединен с входом усилителя-компаратора, выход которог через ключ соединён с первым выводом запоминающего конденсатора 2. Недостатком известного АЦП являет ся большая погрешность, возникающая вследствие разряда запоминающего кон денсатора через сопротивление изоляции между выводами конденсатора, особенно ощутимая в широком диапазоне воздействия дестабилизирующих факторов. Кроме того, устройство содержит сложный узел - дифференциальный усилитель, предназначенный для выделения с высокой точностью разности между вспомогательным и опорным или между вспомогательным и входным напряжения1МИ, что усложняет схему. . Цель изобретения - повышение точности преобразования разнополярных напряжений с применением одного источника опорного напряжения и упрощений схемы. Для этого в интегрирующий аналогоцифровой преобразователь, содержащий коммутатор, первые входы которого соединены соответственно с входной шиной , с выходом делителя опорного напряжения, и с выходом делителя опорного напряжения, а вторые входы с входом интегратора, выполненного на операционном усилителе с конденсатором в цепи обратной связи, выход интегратора соединен с входом усилителя-компаратора, выход которого через ключ соединен с первым выводом запоминающего конденсатора, введены дополнительный делитель с-коэффициентом деления, равным коэффициенту, деления делителя опорного напряжения, повторитель и дополнительный резистор., причем дополнительный делитель включен между выходом источника опорного напряжения и общей шиной, выход дополнительного делителя подключен к второму выводу Запоминающего конденсатора, первый вывод.которого подключен к входу повторителя, выход которого через

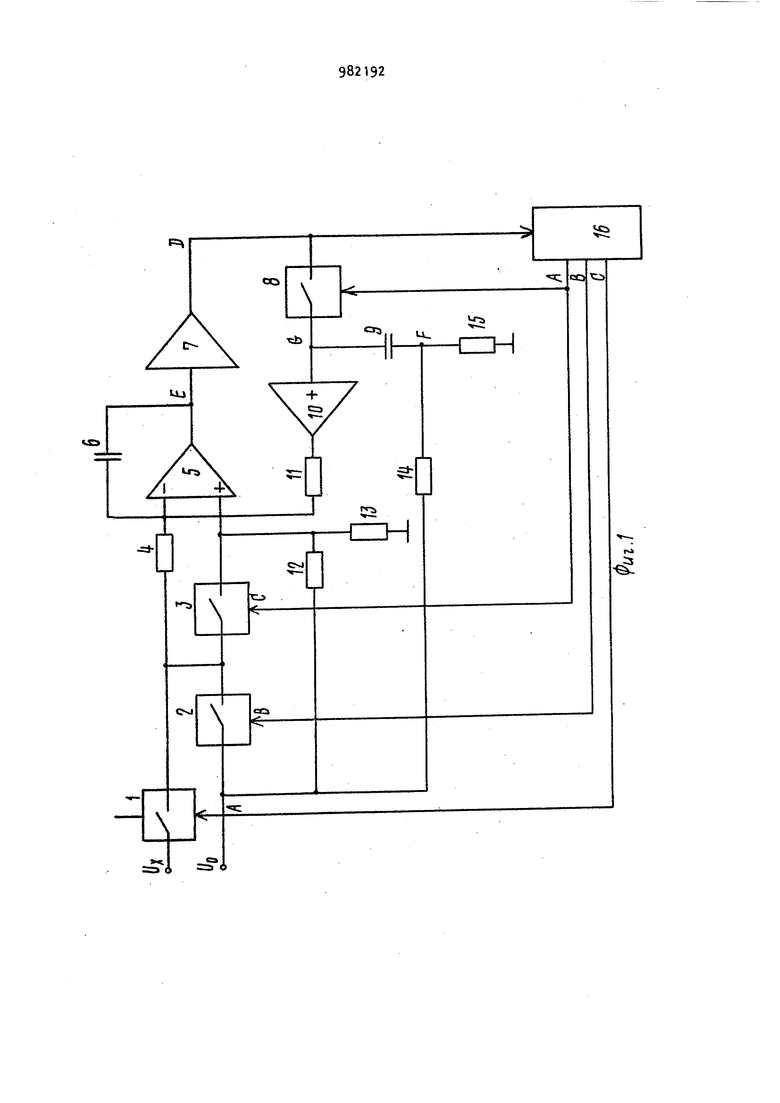

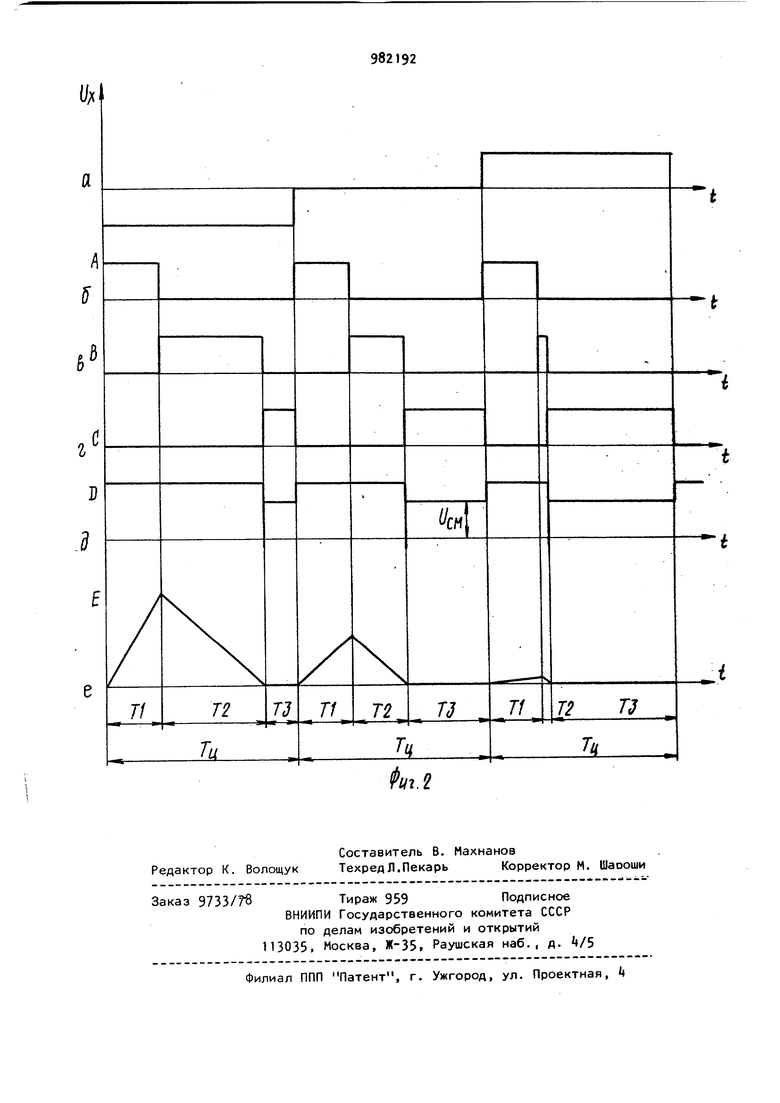

дополнительный резистор соединен с инвертирующим входом усилителя интегратора, неинвертирующий вход которого соединен с выходом делителя опорного напряжения. На фиг. 1 представлена структурная электрическая схема устройства; на фиг. 2 - временные диаграммы работы устройства Устройство содержит коммутатор, состоящий из ключей 1, 2 и 3, резистор k, операционный усилитель 5 и конденсатор 6, образующие интегратор, усилитель-компаратор 7, ключ 8, запоминающий конденсатор 9, повторитель 10, дополнительный резистор 11, резисторы 12 и 13, образующие делитель опорного напряжения, резисторы I и 15, образующие дополнительный делитель, устройство управления 16. Работает аналого-цифровой преобразователь следующим образом. Цикл работы преобразователя фиксированный, состоит 1ФИГ. 2) из интервалов интегрирования Т1, преобразования Т2 и коррекции ТЗ. В течение фиксированного интервала интегрирования Т1 сигналом устройства управления 16 (фиг. 2, б) ключ 1 замыкается, остальные ключи 2, 3 и 8 разомкнуты. Поскольку неинвертирующий вход операционного усилителя 5 находится под напряжением Uj., снимаемом с делителя, образованного резисторами 12 и 13, происходит интегрирование разности входного напряжения Lx и напряжения сгл (фиг. 2 е). После окончания интервала Т1 сигналом устройства 16 (фиг. 2 б) ключ 1 размыкается, а ключ 2 замыкается (фиг. 2 в), подключая к входу интегратора опорное напряжение UQ, ключи 3 и 8 разомкнуты. Происходит в течение интервала Т2 интегрирование разности напряжений и о и Uow, при котором напряжение на выходе интегратора стремится к нулю (фиг. 2е), при достижении которого срабатывает усилитель-компаратор 7- Интервал Т2 длится от окончания интервала интегрирования до срабатывания компаратора. В интервале ТЗ сигналами устройства 16 ключ 2 размыкается (фиг. 2 в) а ключи 3 и 8 замыкаются (фиг. 2 г), ключ 1 разомкнут. В таком состоянии стройство находится в течение интервала ТЗ от момента срабатывания нульргана до начала следующего цикла изерения. На конденсаторе 9 происходит апоминание напряжения дрейфа усили5f 7 и 10 и разности напряжени напряжения в точке F. Напряжеточке G близко к и, . Длительность интервала Т2 однозначно опреде ляет величину и полярность измеряемо го напряжения. Выходное напряжение интегратора в интервале Т1 равно Ux-UcM)--r-i % в интервале Т2 (UO-UCM)-, интегрирующие резистор и конденсатор (резистор k конденсатор 6 ). как , О (UCM-UX ) Ti Uo -UCM получаем (ПРИ ) Т2(0)Т1 Т2(0)1/2Т1 (при ) Включение эквивалентного сопротив ления дополнительного делителя после довательно с запоминающим конденсато ром практически исключает его влияни на устойчивость схемы при замыкании обратной связи. Формула изобретения Интегрирующий аналого-цифровой пре образователь, содержащий коммутатор, первые входы которого соединены COOT ветственно с входной шиной, с выходо источника опорного напряжения и с выходом делителя опорного напряжения, а вторые входы - с входом интегратора, выполненного на операционном усилителе с конденсатором в цепи обратной связи, выход интегратора соединен с входом усилителя-компаратора, выход которого через ключ соединен с первым выводом запоминающего конденсатора, отличающийся тем, что, с целью повышения точности преобразования разнополярных напряжений с приме нением одного источника опорного напряжения и упрощения схемы, введены дополнительный делитель с коэффициентом деления, равным коэффициенту деления делителя опорного напряжения, повторитель и дополнительный резистор, причем дополнительный делитель включен между выходом источника опорного напряжения и общей шиной, выход допол- нительного делителя подключен к второму выводу запоминающего конденсатора, первый вывод которого подключен к входу повторителя, выход которого через дополнительный резистор соединен с инвертирующим входом операционного усилителя интегратора, неинвертирующий вход которого соединен с выходом делителя опорного напряжения. Источники информации, принятые во внимание при экспертизе . Патент США № , кл. StOЗ, 1977. 2. Патент Англии № 139006, кл. G i Н, 1975 (прототип).

vjd

Авторы

Даты

1982-12-15—Публикация

1981-03-26—Подача