(54) САМОНАСТРАИВАЮЩАЯСЯ СИСТЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Самонастраивающаяся система | 1981 |

|

SU1004971A1 |

| УСТРОЙСТВО ДЛЯ КЛАССИФИКАЦИИ МНОГОПАРАМЕТРИЧЕСКИХ ОБЪЕКТОВ | 1991 |

|

RU2049355C1 |

| Адаптивная система управления | 1984 |

|

SU1257607A1 |

| Устройство для определения параметров динамического звена | 1983 |

|

SU1160372A1 |

| Устройство для измерения чистого запаздывания инерционного звена | 1984 |

|

SU1236430A1 |

| Устройство для вычисления оптимального распределения нагрузок на теплоэлектростанции | 1972 |

|

SU485491A1 |

| Ультразвуковое устройство для измерения контактных давлений | 1990 |

|

SU1746297A1 |

| Дискретный самонастраивающийся регулятор | 1973 |

|

SU544942A1 |

| Адаптивная система управления | 1985 |

|

SU1361502A1 |

| Устройство для регулирования многопараметрического объекта | 1975 |

|

SU1080115A1 |

Изобретение относится к дискретным беспоисковым самонастраивающимся системам автоматического управления для нейтральных объектов и может быть использовано, например, в самонастраивают щихся системах управления движением ле тательных аппаратов при неизвестных за ранее значениях коэффициента эффективности управления объекта и внешнего воз мущения. Наиболее близкой по технической сущности является дискретная самонастраивающая система, содержащая усилители, умножитель, делитель, блоки сравнения, блоки, памяти, последовательно соединенные первый блок памяти, второй блок памяти и первый блок сравнения и последовательно соединенные первый сумматор, третий блок памяти, объект управления, второй блок сравнения, первый ключ и четвертый блок памяти, выход которого соединен через первый и второй усилители с первыми входами соответственно вт рого и третьего сумматора, а вход соединен через третий и четвертый усилители с вторыми входами соответственно BTqporo и третьего сумматоров, выход первого сумматора через первый блок . памяти соединен с входами первого блока сравнения и первого сумматора Cll Недостатком этого устройства является необходимость наличия большого количества блоков памяти, суммирования, умножения и деления, аппаратурная реализуемость которых особенно затруднительна, и дополнительного корректирующего устройства, Кроме того, этот регулятор об- Ладает недостаточно высоким быстродействием, так как необходимые для идентификации неизвестных параметров объекта управления условия создаются только через время, равное трем периодам дискретности системы, малая точность и надежность системы. К тому же в состав устройства входят два блока деления, каждый из которых имеет по два входа: вход делимого и вход делителя. В реальных условиях работы системы не исключена

возможность TSKOffl комбинации параметроБ движения и входных управляющих и воэмушаюших Bogfleftcf ВИЙ, гфи которой сигшыш на входах дешггелей блоков деления будут кметь низкий уровень (близкий к аупввому или равный ему). Это приведет к тому, что блоки деления не смогут нормально 4 нкцион1фовать. При вьшолнении бпоков деления на элементах аналоговой вычислительной техники на выходе этих блоков появится нащ)яжение, соответствующее предельному, критическому для данного регулятора. В случае реализации указанных блоков деления на элементах вычислительной техники в данном случае будет иметь место переполнение разрядной сетки и вьщача на выходе неправильной информации.

Цель изобретения - повышение точност и надежности системы, обеспечение заданного оптимального угфавления движением объекта, независимого от заранее неизвесных значений коэффициента эффективности управления объекта и внешнего возмущения, повышение динамической надежности и быстродействия системы и повышение надежности идентификации коэффициента эффс-ктивности управления объекта при низких значениях уровня сигнала на входе делителя блока деления путем применения дискретного самонастраивающегося регулятора более гфостой структуры для идентификации коэффициента эффективности упрйвления объекта и внешнего возмущения и последующей настройки коэффициентов передачи регулятора без изменения его структуры для формирования сигнала управления.

Это достигается тем, что самонастраивающая система содержит последовательНО соединенные второй ключ, пятый блок памяти и пятый усилитель, последовательно соединенные шестой блок памяти, третий блок сравнения, третий ключ и реле с замыкающими и размыкающими контактами, последовательно соединенные первый замыкающий контакт реле, делитель и умножитель, последовательно соединенные первый размыкающий контакт реле, седьмой блок памяти и второй размыкающий контакт реле, соединенный через последовательно соединенные второй замыкающий контакт и седьмой блок памяти с выходом седьмого блока памяти и непосредственно с первым входом умножителя, выход третьего сумматора соединен с входом шестого блока памяти и с вторым входом третьего блока сравнения и через

последовательно соедине шые шестой усилитель, второй сумматор и умножитель с вторым входом первого сумматрра, выход пятого блока памяти через седьмой усилитель соединен с четвертым входом второго сумматора, выход пятого усилителя - с третьим входом третьего сумматора, выход третьего блока сравнения через трртий замыкающий контакт реле с вторым входом делителя.

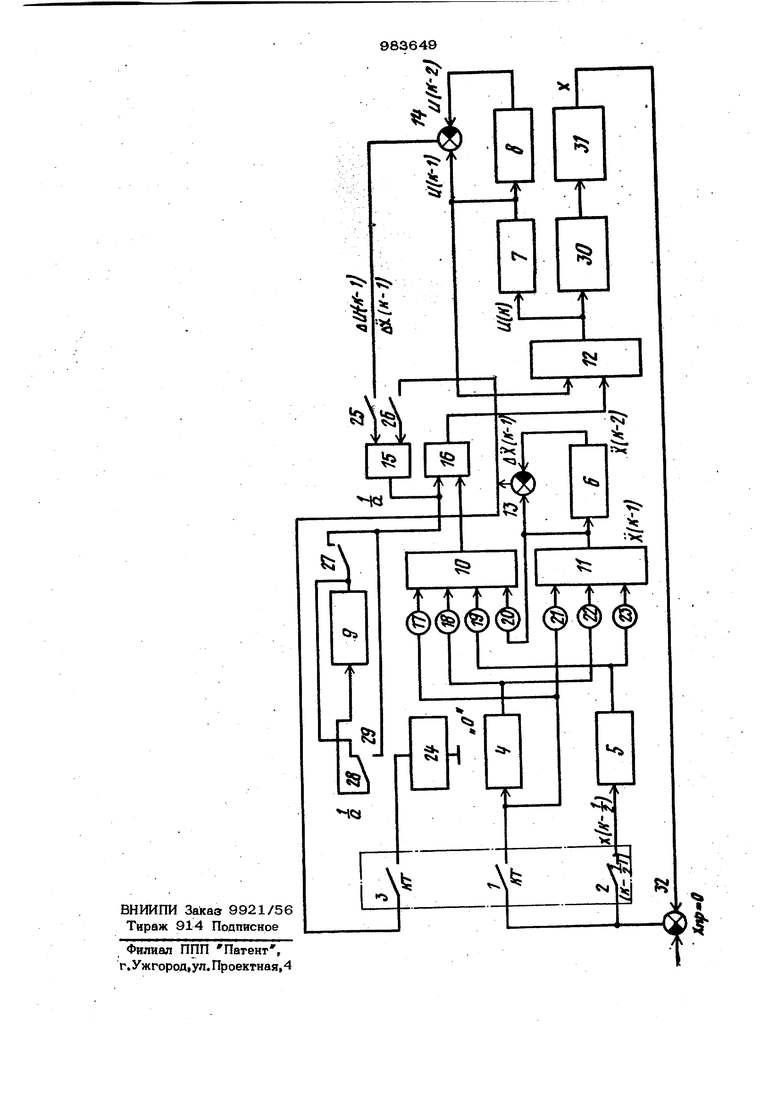

На чертеже представлена схема устройства.

Схема содержит первый ключ 1, второй ключ 2, третий ключ 3, четвертый блок 4 памяти, пятый блок 5 памяти, шестой блок

6памяти, первый блок 7 памяти, второй блок 8 памяти, седьмой блок 9 памяти, второй сумматор 10, третий сумматор .11, первый сумматор 12,- третий блок 13 сравнения, первый блок 14 сравнения, де.литель 15, умножитель 16, третий усилитель 17, первый усили.тель 18, седьмой усилитель 19, шестой усилитель 2О, четвертый усилитель 21, второй усилитель 22, пятый усилитель 23, реле 24, первый замыкающий контакт 25, третий замЕзТкающий контакт 26 .второй размыкающий контакт 27, первый раз мыкаю .ций контакт 28, второй замыкающий контакт 29, третий блок 30 памяти, объект 31 управления, второй блок 32 сравнения. Работа устройства состоит в запоминании дискретных значейий сигналов х(к-1) и х(к-i) с помощью блоков 4 и 5 памяти, суммировании сигналов хСк), х{к-) и х(к-1) с соответствующим их усилением усилителями 17-19, с пoмoш зю сумматоров 10 и 11, формировании сигналов к(к-1) и х(к-2) с помощью сумматора 11 и блока 6 памяти, подаче с выхода сумматора 11 усиленного усилителем 2О сигнала х{к-1) на вход сумматора 1О для учета при формировании управляющего воздействия внешнего возмущения , формировании с помощью блока 13 сравнения сигнала Лх(к -1) для определения значения коэффициента эффективности управления объекта, запоминании с помощью блоков

7и 8 памяти значений дискретных сигналов управляющих воздействий U (к - 1) и и(к-2), формировании с помощью блока 14 сравнения сигнала л U (к - 1), котор ый совместно с выходным сигналом дх(к-l) блока 13 сравнения через две замыкающие группы 25 и 26 контактов реле 24 контроля уровня сигнала лisCK l) на входе делителя 15 с помощью этого блока деления позволяет определить значение -i, гда

ц - фактическое значение коэффициента управления объекта, умножении выходного

59836496

сигнала блока сумматора 1О на получен- налыди(к-1) и4х(л-1) с выходов бпоный коэффициент с выхода делителя 15 с помощью умножителя 16 и формировании требуемого.управляющего воздействия U( к) с помощью сумматора 12, на входы которого поступают выходные сигнале с блока 7 памяти и умножителя 16. Управляющее воздействие и (к) с выхода сумматора 12 поступает на блок ЗО памяти (фиксируво- щее звено нулевого порядка) и через него на объект 31 управления. Для обеспечения работоспособности предлагаемого дискретного регулятора гфи условии наличия низкого (близкого или равногонул9вому)уровнясигнала лх(к-1) на входе делителя делителя 15, при котором он не может нормально функционировать, введено реле контроля уровня сигнала Л х( к- 1) с выхода блока 13 сравнения с четырьмя группами Контактов 25-29, которое гфедварительно настраивается на срабатывание при некотором заданном минимально допустимом значении сигнала 1Лх(к-1)|ц...й,и блок 9 памяти для запоминания предшествующего значе шя параметра с выхода делителя 15. Контролируемый сигнал Л х( к - 1) с выхода блока 13 сравнения поступает на реле 24 контроля уровня этого сигнала через ключ 3, замы кающийся одновременно с ключом 1. Рабо та этой части дискретного регулятора сос тоит в анализе уровня сигнала л х(к-1) с выхода .блока сравнения 13 с помощью ре ле 24 контроля уровня сигнала, которое TspK значении сигнала л х( к - 1;, превьш1ающем минимальное допустимое значение |Лх(к-l) (гфи этом делитель 15 нормально функционировать), при каждом замыкании ключа 3 срабат.1вает и сво. ими замыкающими контактами 25 и 26 подключает к входам делителя 15 сигналы Л1}(к-1) иЛхХк-l) с выходов блоков 14 и 13 сравнения, размыкающим контактом 27 отключает вьLx:oд блока 9 памяти от входа умножителя 16, размыкающим (пе--« реключающим) контактом 28 - вход блока 9 памяти от его выхода, а замыкающим (переключающим) контактом 29 подключает выход делителя 15 к входу блока 9 памяти для запоминания текущего факти- 5 ческого значения параметра . При значении уровня сигнала 4х(к-1), не превышающем минимальное допустимое значение | Дх(к- 1)1,(при этом делитель 15 не может нормально функционировать), реле контроля уровня 24 не срабатывает и своими замыкающими контактами 25 и 26 отключает от входов делителя 15 сигков 14 и 13 сравнения, разх4ыкающнх контактом 27 подключает выход блока 9 памяти, в котором запоминается ранее вычисленное, значение параметра i к выходу умножителя 16, размыкающим (переключающим) контактом 28 вход блока 9 памяти подключается к его выходу для регенерации (восстановления) значения параметра i, так как репе контроля уровня может не срабатывать в течение нескольких периодов дис1фетйости ввиду низкого уровня значения сигнала ДхСк-1), и замыкающим (переключающим) контактом 29 отключает вход блока 9 памяти от выхода блока 15 дедения. При работе системы, в условиях нормального функционирования через время t 2Т создаются условия для идентификации значений коэффициента эффективности управления объекта ш и внешнего возмущения f. На основе этих значений изменяются входной сигнал и коэффициент усиления регулятора, реализуемый с помощью умножителя 16 так, чтобы определить оптимальное управление и(к), которое обеспечит требуемую точность и надежность работы замкнутой . системы при отсутствии начальной информации о действительных значениях аир. При этом характер переходного процесса замкнутой системы будет независимо от значений d и f и определяется только гфедва:рительно заданными собственными значениями матрицы замкнутой системы Это приводит к повышению не тЧэлькр точности, но и надежности, как свойства системы сохранять свои характеристики в заданных гфеделах при изменении условий функцио- -нирования системы непредвиденным образом. I Предлагаемый дискретный самонастраи вающийся регулятор имеет простую структурную схему и выгодно отличается от известных аналоговых схем, так как для его реализации требуется минимальное количество типовых вычислительных устройств автоматики. Это позволяет не гфо. водить большие и дорогостоящие исследования при проектировании дискретной системы управления, так как регулятор способен быстро ( в течение двух периодов дискретности) определять реальные значения коэффициента эффективности угфавле- ния объекта и внешнегЪ возмущения, а затем настроить каэф4)ициенты закона управления заранее известной структуры с целью обеспечения задагшой цели управления. Формула изобретения С амонастраивающаяся система,содержащая усилители, умножитель, делитель, блоки сравнения, блоки памяти, последовательно соединенные первый блок памяти, второй блок памяти и первый блсж сравнения и последовательно соединенные первый сум- матер, третий блок памяти, объект управ- 5 ления, второй блок сравнения, первый ключ и четвертый блок памяти, выход которого соединен через первый и второй усилители с первыми входами соответственно второго и третьего сумматора, а вход через тре- ° тий и четвертый усилители - с вторыми влодами соответственно второго и третьего сумматоров, выход первого сумматора через первый блок памяти соединен с входами первого блока сравнения и первого 5 сумматора, отличающаяся тем, что, с целью повышения точности и надежности системы, она содержит последовательно соединенные второй ключ, пятый блок памяти и Пятый усилитель,последовагельно 20 соединенные шестой блок памяти, третий блок сравнения, третий ключ и реле с замыкающими и размыкающими контактами, последовательно соединенные первый замыкающий контакт реле, делитель и умножи- 25 тель, последовательно соединенные первый

размыкающий контакт реле, седьмой блок памяти и втсрой размыкающий контакт реле, соединенный через последовательно соединенные второй замыкающий контакт н. седьмой блок памяти с выходом седьмого блока памяти и непосредственно с первым входом умножителя, выход третьего сумматора соединен с входом шестого блока памяти и с вторым входом третьего блока сравнения и через последовательно соединенные шестой- усилитель, второй сумматор и умножитель - с вторым входом первого сумматора, выход пятого блока памяти через седьмой усилитель соединен с четвертым входом второго сумматора, выход пятого усилителя - с третьим входом третьего сумматора, выход третьего .;блока сравнения через третий замыкающий контакт реле - с вторым входом делителя.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-12-23—Публикация

1980-03-04—Подача