(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ .ДЬОИЧНОПЯТЕРИЧНОГО КОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двоично-пятеричного кода | 1985 |

|

SU1359912A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ И ПЕРЕДАЧИ СИГНАЛОВ КОДОВОЙ РЕЛЬСОВОЙ ЦЕПИ | 1991 |

|

RU2005639C1 |

| Устройство для управления обменом данными | 1989 |

|

SU1795466A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| УСТРОЙСТВО ТЕЛЕСИГНАЛИЗАЦИИ | 1991 |

|

RU2029378C1 |

| Двухразрядный сумматор в коде"M из | 1978 |

|

SU798828A1 |

| УСТРОЙСТВО СВЕРТКИ ПО ПЕРЕМЕННОМУ МОДУЛЮ | 1991 |

|

RU2051408C1 |

| Устройство для управления и имитации неисправностей | 1991 |

|

SU1833897A1 |

| Устройство для формирования тестов в многорегистровых кодах | 1980 |

|

SU888126A1 |

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

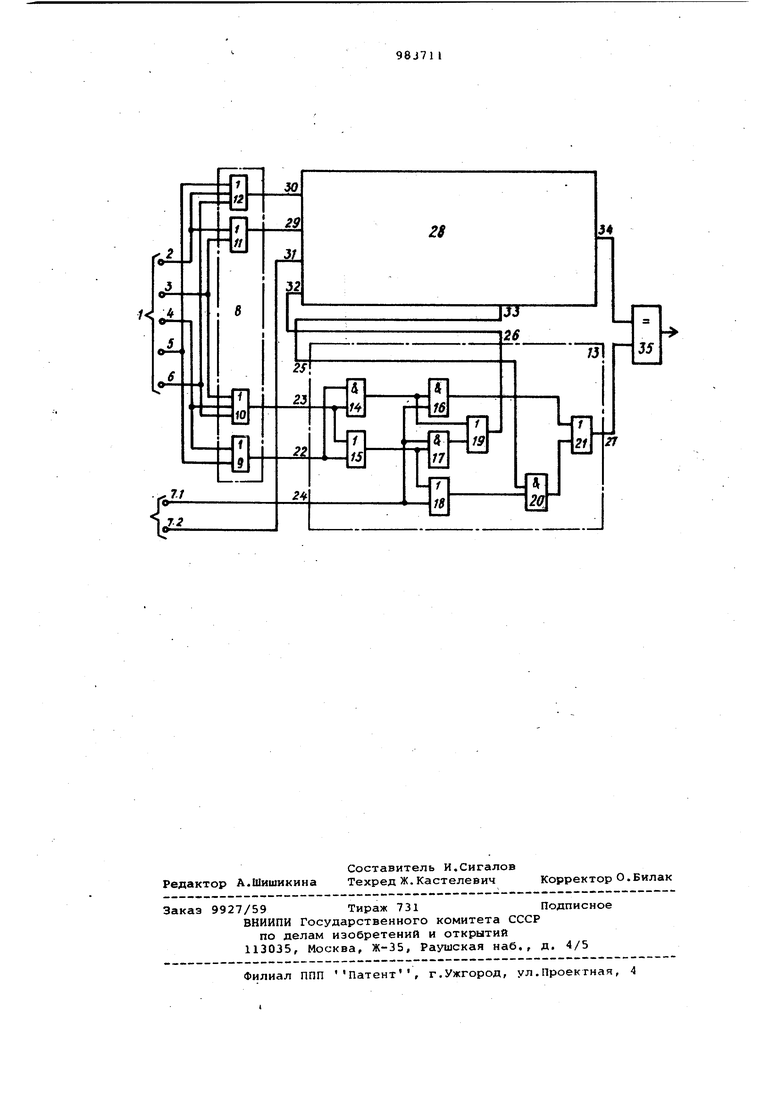

, Изобретение относится к вычислительной технике и может быть применено для обиаружения ошибок в работе .диокретных). блоков вычислительных машин. Известно устройство контроля правильности для двоично-пятеричного кода, содержащее группу двухвходовых элементов И/ группу злементрв ИЛИ и элемент И-ИБ. Выходы первого и второго элементов ИЛИ подключены к входам третьего элемента ИЛИ и к входа м одного элемента И группы. Входы остальных элементов И группы, первого, второго и четвертого элементов ИЛИ подключены к соответствукяцим входам устройства. Выходы элементов И группы соединены с входами пятого элемента ИЛИ, его выход подключен к одному из входов шестого элемента ИЛИ, другой вход которого соединен с выходом эле ;мента И-НЕ. Входы элемента И-НЕ подключены к выходам третьего и четвертого элементов ИЛИ 1. Недостатком устройства является низкая эффективность контроля. Указанный недостаток обуславливается сл Iдующим. Во внутренних узлах структуры уст ройства возможны неисправности, KQTO рые не проявляются при его нормгшьной работе. Так, из 24 возможных одиночных неисправностей, 10 неисправностей не проявляется при работе устройства. Поэтому для обеспечения заданной степени достоверности контроля необходимо периодически проводшть профилактические тестовые проверки устройства. Для организации тестовых проверок требуются аппаратурные и временные затраты, которые снижают эффективность контроля. Наиболее близким к изобретению техническим решением является устройство для контроля кода 2 из п , содержащее первый и второй пороговые блоки, элемент НЕ и элемент ИЛИ. Каждый пороговой блок содержит группу элементов И, группу элементов ИЛИ и элемент ИЛИ. Группа выходов первого порогового блока соединена с входами второ.го порогового блока, выход которого подключен.к первому входу элемента ИЛИ, второй вход элемента ИЛИ через элемент НЕ соединен с выходом первого порогового блока, а выход является выходом устройства 2. Недостатком устройства является низкая эффективность контроля. Причиной этого недостатка также служат неисправности во внутренних узлах стру туры устройства, которые не проявляются при его работе. Для их обнаруже ния требуются дополнительные тестовые проверки, затраты на организацию которых обуславливают низкую эффективность контроля. Цель изобретения - повышение эффективности контроля. Поставленная цель достигается тем что в устройство для контроля двоичн пятеричного кода, содержащее схему сравнения, выхйд которой является выходом устройства, введен шифратор и первый .и второй преобразователи кода три из шести в код один из двух, причем группа, информационных входов уст ройства соединена с группой входов шифратора, первый и второй выходы которого соединены соответственно с первым и вторым входами первого преобразователя кода три из шести в код один из двух, первый и второй выходы которого соединены соответственно с первым входом схемы сравнения и с третьим входом второго преобразователя кода три из шести в код один из двух, третий и четвертый выходы шифратора соединены соответственно с первым и вторым входами второго преобразователя кода три из шести в код один из двух, первый и второй выходы которого соединены соответственно с вторым входом схемы сравнения и с третьим входом первого преобразователя кода три из шести в код один из двух, первый и второй информационнее входы устройства соединены соответственно с четвертыми входами первого и второго преобразователя кодов три из шести в код один из двух. При этом шифратор содержит первый второй, третий и четвертый элементы ИЛИ, причем первый вход информационной группы входов шифратора соединен с первыми входами первого и второго элементов ИЛИ, второй вход информационной группы входов шифратора соединен с вторым входом второго элемента ИЛИ и первым входом третьего элемента ИЛИ, третий вход информационной группы входов шифратора соединен с третьим входом второго и третьего элементов ИЛИ/ четвертый вход информационной группы входов шифратора соединен с вторыми входами третьего и четвертого элементов ИЛИ, пятый вход информационной группы входов шифратора соединен с вторым входом первого элемента ИЛИ и с третьим входом четвертого элемента ИЛИ, выходы первого, второго и третьего-и четвертого элементов ИЛИ являются соответст венно первым, вторым, третьим и четвертым выходами шифратора. Кроме того, преобразователь кода три из шести в код один из двух содержит первый, второй, третий и чет-( вертый элементы ИЛИ, первый, второй, третий и четвертый элементы И, причем первый и второй входы преобразователя кода один из двух соединены соответственно с первыми входами первого и второго элементов И и ИЛИ, выход первого элемента И соединен с первыми входами второго элемента ИЛИ и второго эпеменга ТЛ, выход которого соединен с первым входом третьего элемента ИЛИ, выход первого.элемента ИЛИ соединен с первым входом третьего элемента И и первым входом четвертого элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, третий вход преобразователя кода три из шести в код один из двух соединен с вторым входом четвертого элемента И, выход которого сое-, динен с. вторым входом третьего элекента ИЛИ, четвертый вход преобразователя кода три из шести в код один из двух соединен с вторыми входами второго элемента И, четвертого элемента ИЛИ и третьего элемента И, выход которого соединен с вторым входом второго элемента ИЛИ/ выходы третьего и второго элементов ИЛИ являются соответственно первым и вторым выходами преобразователя koffat три из шести в код один из двух. На чертеже представлена конструкция устройства. Устройство содержит первую информационную группу 1 входов, которая включает в себя пять входов 2-6, и группу входов, состоящую из двух первого 7.1 и второго 7.2 информационных входов устройства, шифратор 8, состоящий из элементов ИЛИ 9-12. Устройство также содержит первый преобразователь 13 кода один из двух, который включает в себя первые элементы И 14 и ИЛИ 15, второй и третий элементы И 16 и 17, четвертый и второй элементы ИЛИ 18 и 19, четвертый элемент И 20 и четвертый элемент ИЛИ 21, первый, второй, четвертый и третий входы 22-25 соответственно, второй и первый выходы 26 и 27 соответственно. Устройство также содержит второй преобразователь кода три из шести в код один из двух, состав элементов которого идентичен ссэставу элементов первого преобразователя 13, входы и выходы обозначены 29-34 соответственно, и схему 35 сравнения. Устройство имеет следующие связи. Входы элементов ИЛИ 9-12 шифратора 8 подключены к входам 4, 5; 3,4,6; 2,3 и 2,5,6 соответственно, а их выходы - к первому vti второму входам 22 и 23 первого преобразова-. теля 13, к первому и второму входам 29 и 30 второго преобразователя 28 соответственно. Первый информационный вход 7.1 подключен к четвертому входу 24 преобразователя 13, а вход 7.2 - к третьему входу 31 второго преобразователя 28. Вторые входы 26 и 33 первого и второго преобразовате лей 13 и 28 подключены к третьим вхо дам 32 -и 25 второго и первого преобразователей 2.8 и 13. Выход схемы 35 сравнения является контрольным выходом устройства. Входы схемы сравнени соединены с первыми выходами 27 и 34 преобразователей 13 и 28. Элементы первого преобразователя 13 имеют связи входы первых элементов И 14,ИЛИ 15 подключены к входам 22 и 23 преобразователя. Выход перво го элемента И 14 соединен с первыми входами вторых элементов И и ИЛИ 16 и 19 соответственно. Выход первого элемента ИЛИ 15 соединен с первым вх дом третьего элемента И 17 и первым входом четвертого элемента ИЛИ 18. Вторые входы второго элемента И 16, третьего элемента И 17 и четвертого элемента ИЛИ 18 подключены к четвертому входу 24 преобразователя 13. Вы ход второго элемента И 16 подключен к одному из входов третьего элемента ИЛИ 21, соединенного с вторым выходом 27 преобразователя 13. Выход вто рого элемента ИЛИ 19 соединен с выходом преобразователя 13. Выход третьего элемента И 17 подключен к другому входу второго, элемента ИЛИ 19. Выход четвертого элемента ИЛИ 18 соединен с одним из входов четвертого элемента И 20. Другой вхо четвёртого элемента И 20 подключен к третьему входу 25 преобразователя 13. Выход четвертого элемента И 20 соединен с вторым входом третьего элемента ИЛИ 21. Связи элементов второго преобразо вателя 28 идентичны связям элементов первого преобразователя 13. Группа 1 информационных входов предназначена для подачи сигналов в унитарном коде 1 из 5 в устройство. Первый и второй информационные входы 7.1 и 7.2 служат для подачи кода 1 из 2. Шифратор 8 предназначен для преобразования унитарного кода 1 из в код 2 из 4, а также преобразования кодовых комбинаций, не принадлежащих коду 1 из 5, в кодовые комбинации, не принадлежащие коду 2 из 4. Первый и второй преобразователи 13 и 28 предназначены для преобразования кода 3 из 6 в код 1 из 2, а также преобразования кодовых слов, не принадлежащих коду 3 из 6, в кодо вые слова, не принадлежащие коду 1 из 2, т.е. 00 или 11. Схема 35 сравн-ания предназначена для формирования контрольного сигнала. Устройство работает следующим образом. При поступлении на входы устройства сигналов, соответствующих кодовому слову двоично-пятеричного кода, на выходах шифратора 8 формируются сигналы, соответствующие кодовому слову кода 2 из 4. На входы первого и второго преобразователей 13 и 28 поступают сигналы, описываемые кодовой комбинацией кода 3 из 6, на выходах 27 и 34 первого 13 и второго 28 преобразователей соответственно формируются 01 или 10. Контрольный сигнал на выходе схемы 35 сравнения v имеет нулевое значение. Если на .входы устройства поступают сигналы, кото.рые не соответствуют кодовой комбинации двоично-пятеричного кода, то на входы преобразователей 13 и 28 поступают сигналы, которые описываются кодовыми словами, не принадлежатдими коду 3 из 6. На выходах 27 и 34 преобразователей 13 и 28 формируются сигналы, соответствующие кодовым комбинациям 00 или 11. В этом случае схеjMa 35 сравнения формирует сигнал контроля об ошибке. I. Преимущество предлагаемого устройства заключается в том, что оно является самопроверяемым. Любая одиночная неисправность вида Константный О или Константная 1 во внутренних узлах структуры устройства проявляется при его работе. В реэультатё этого обеспечивается высокая эффективность контроля, так как отпадает необходимость в дополнительных затратах на профилактические тестовые проверки устройства. Формула изобретения 1.Устройство дпя контроля двоичнопятеричного кода, содержащее схему сравнения, выход которой является выходом устройства, отличающееся тем, что, с целью повышения эффективности контроля/ в него введен шифратор и первый и второй преобразователи кода три из шести .в код один из двух, причем группа информационных входов устройства соеди.нена с группой входов шифратора, первый и второй выходы которого соединены соответственно с первым и вторым входами первого преобразователя кода три из шести в код один из двух, первый и второй выходы которого соединены соответственно с первым входом схемы сравнения и с третьим входом второго преобразователи кода.три из шести в код один из двух,третий и четвертый выходы шифратора соединены соответстг венно с первым и вторым входами второго преобразователя кода три из шести в код один из двух,первый и второй выходы которого соединены соответственно с вторым входом схемы сравнения и с третьим входом первого преобразователя кода три из шести в код один из двух первый и второй информационные входы устройства соединены соответственно с четвертыми входами, первого и второго преобразователя кодов три из шести в код один из двух. 2.Устройство по П1 1г о т л и Чающееся тем, что шифратор содержит первый, второй, третий и четвертый элементы ИЛИ, причем первый вход информационной группы входов шиф ратора соединен с первыми входами пер вого и второго элементов ИЛИ, второй вход информационной группы входов шиф ратора соединен с вторым входом вто- рого элемента ИЛИ и первым входом третьего элемента ИЛИ, третий вход информационной группы входов шифратора соединен с третьим- входом второго и третьего элементов ИЛИ, четвертый вход информационной Группы входов шифратора соединен с вторыми входами третьего и четвертого элементов ИЛИ, пятый вход информационной груп- пы входов шифратора соединен с вторым входом первого элемента ИЛИ и с третьим входом четвертого элемента ИЛИ, выходы первого, второго, третьего и четвертого элементов ИЛИ являются соответственно первым, вторым, третьим и четвертым выходами шифратора. 3.Устройство по п. .1, о т л и чающееся тем, что преобразователь кода три из шести в код один из двух содержит первый, второй, трек тий и четвертый элементы ИЛИ, первый второй, третий и четвертый элементы И, причем первый и второй входы преобразователя кода один из двух соединены соответственно с первыми и вторыми входами первого и второго элементов И и ИЛИ, выход первого элемента И соединен с первыми : ходами втоporo элемента ИЛИ, и второго элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход первого элемента ИЛИ соединен с первым входом третьего - элемента И и первым входом четвертого элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, третий вход преобразователя кода три из шести в код один из двух соединен с вторым входом четвертого элемента И, выход которого соединен с вторым входом третьего элемента ИЛИ, четвертый вход преобразователя кода три из шести в код один из двух соединен с вторыми входами второго элемента И, четвертого элемента ИЛИ и третьего элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, выходы третьего и второго элементов ИЛИ являются соответственно первым и вторым выходами преобразователя кода три из шести в код один из двух. Источники информации, принятые во внимание при экспертизе 1.Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ. М., Мир, 1972/ с. 165, фиг. 9, 10. 2.Авторское свидетельство СССР № 622085, кл. G 06 F 11/12, 1978 (прототип).

Авторы

Даты

1982-12-23—Публикация

1980-12-24—Подача