Изобретение относится к устройствам ввода-вывода цифровых вычислительных машин и может быть использовано для ввода-вывода цифровой информации в многоканальных системах обработки данных.

Известно устройство для вывода информации, содержащее блок согласования, формирователь импульсов считывания, первый регистр, формирователь импульсов записи, блок сравнения, блок коммутации, блок управления, блоки сопряжения, фор- мирователь и м п у л ь с о в с и н- хронизации, второй и третий регистры.

Недостатком этого устройства является ограниченные функциональные возможности в части объема вводимой информации и низкая достоверность ее ввода.

Известно устройство для ввода-вывода информации, содержащее блок сопряжения, блок коммутации, регистр обмена, блок управления, формирователь импульсов считывания, арбитр, клавиатуру команд, шифратор команд, шифратор цифровой информации, блок элементов ИЛИ, формирователь признака конца слова, шифратор служебных слов, первый и второй мультиплексоры, пять мажоритарных блоков.

Недостатком такого устройства является возможность генерации ложных сигналов в кодовую линию связи при одной возможной неисправности в устройстве, а также невозможность ввода информации в источник цифровой информации клавиатуры и других накопителей информации с целью управления их работой (например при тестах),

Цель изобретения - повышение надежности устройства и расширение его функци- онэльныхвозможностей по взаимодействию с накопителем информации.

С этой целью в устройство для ввода-вывода, содержащее блок управления, блок

VI

ю ел

N о о

коммутации, блок сопряжения (блок приемопередатчиков), два мультиплексора, первый регистр, причем первый, второй информационные входы-выходы блока приемопередатчиковявляютсяинформационными входами-выходами устройства, группа информационных входов первого регистра и группа информационных выходов первого мультиплексора образуют группы информационных входов и выходов устройства, первый второй входы логического условия и первый и второй выход блока управления являются первым и вторым стробирующими входами и выходами устройства группа выходов первого регистра соединена с первыми группами информационных входов первого, второго мультиплексоров, с первой группой входов логического условия блока управления и образуют вторую группу информационных вы-. ходов устройства, вторая группа информационных входов мультиплексора образует вторую группу информационных входов устройства, первый и второй информационные выходы, первый и второй информационные входы блока приемопередатчиков соединены с первым, вторым информационными входами, с первым, вторым информационными выходами блока коммутации соответственно, группа управляющих входов которого соединена с первой группой выходов блока управления, третий, четвертый и пятый выходы которого соединены соответственно с входом записи первого регистра, с управляющим входом первого мультиплексора, с информационным входом второго мультиплексора, введены блок контроля времени выдачи данных, преобразователь последовательного кода. в параллельный и наоборот, второй регистр, блоксравйения адресов, причем первая группа информационных входов блока сравнения адресов образует первую группу адресных входов устройства, вторая группа информационных входов второго мультиплексора соединена с группой адресных входов преобразователи последовательного кода в параллельный и наоборот и образует вторую группу адресных входов устройства, информационный выход блока контроля времени выдачи данных соединен с третьим информационным входом блока коммутации, третий информационный выход которого соединен с информационным входом преобразователя последовательного кода в параллельный и наоборот, информационный выход которого соединен с информационным входом блока контроля времени выдачи данных, группа тактовых входов которого соединена со второй группой выходов блока управления, третий вход логического условия и шестой выход которо-- го соединены соответственно с выходом контроля адреса и с разрешающим входом преобразователя последовательного кода в п араллельный и наоборот, группа информационных входов-выходов которого соединена с группой информационных выходов второго мультиплексора, с группой инфор0

мационных входов второго регистра, со второй группой информационных входов блока сравнения адресов, выход которого соединен с четвертым входом логического условия блока управления, седьмой выход

5 которого соединен со вторым входом записи второго регистра, группа выходов которого соединена с третьей группой информационных входов первого мультиплексора и со второй группой входов логи0 ческого условия блока управления.

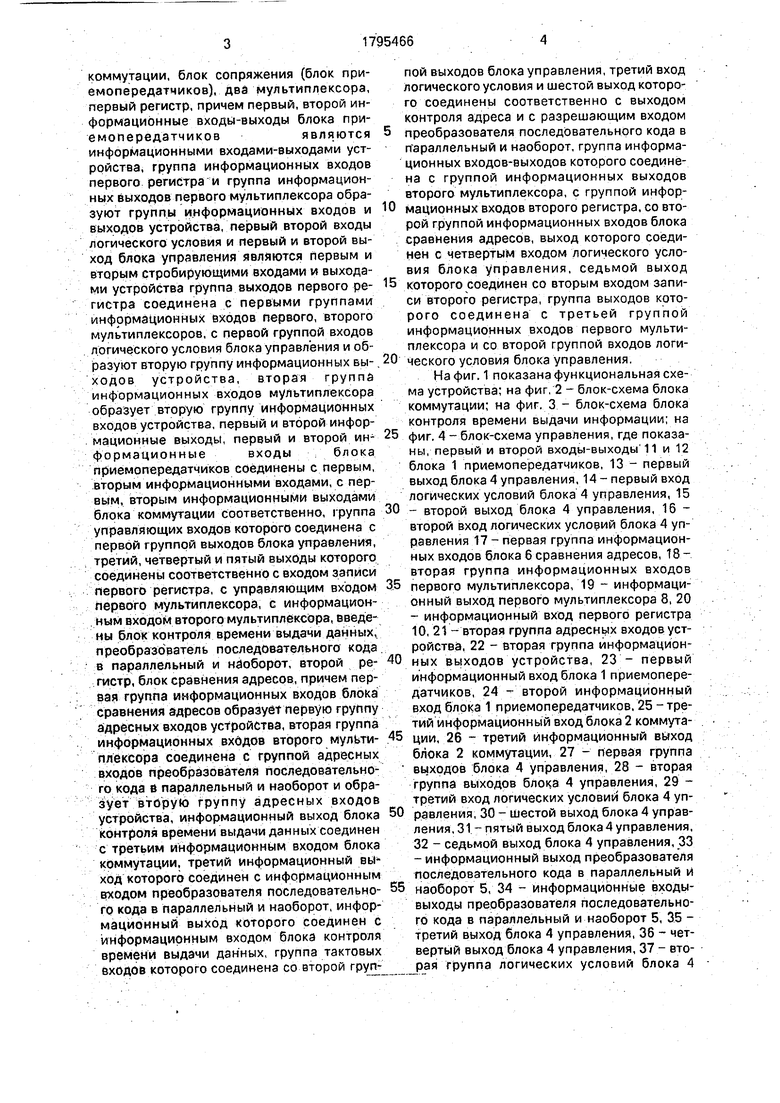

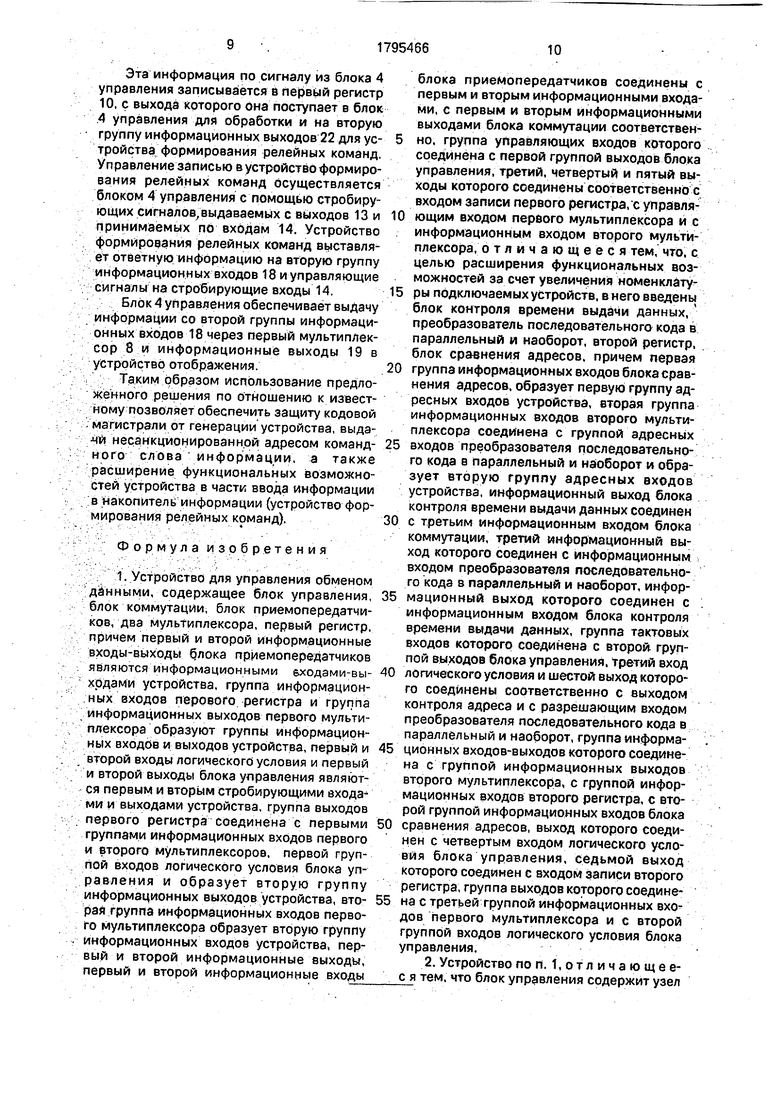

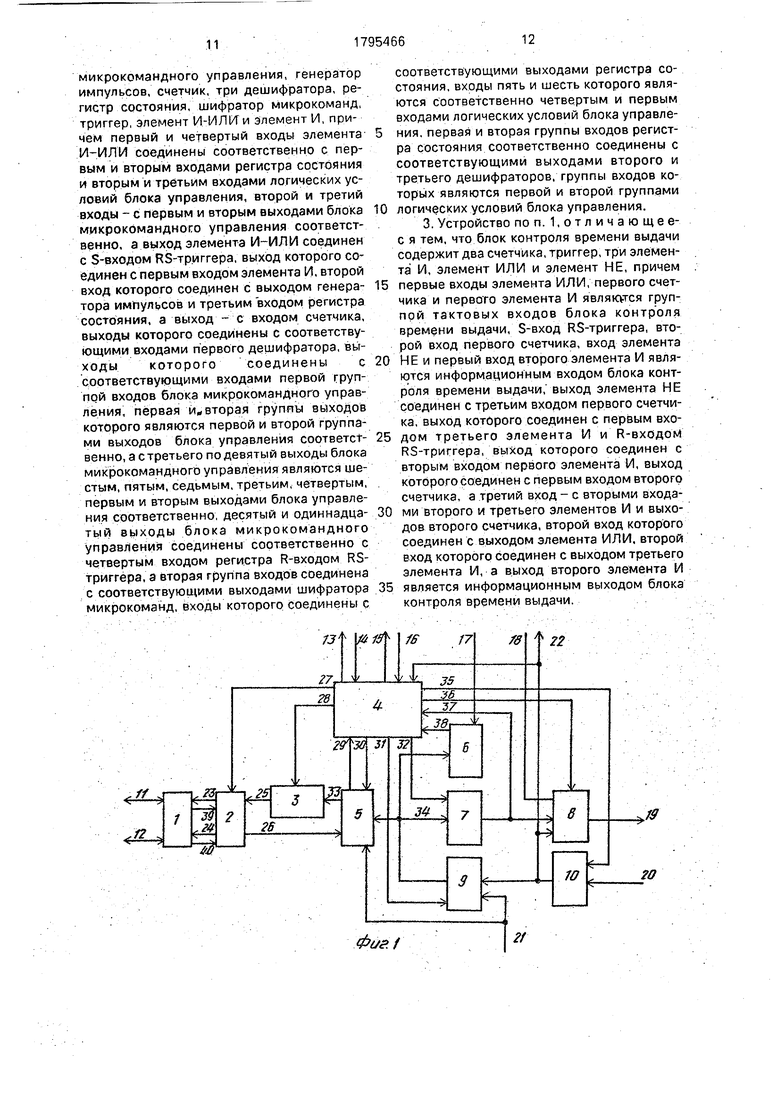

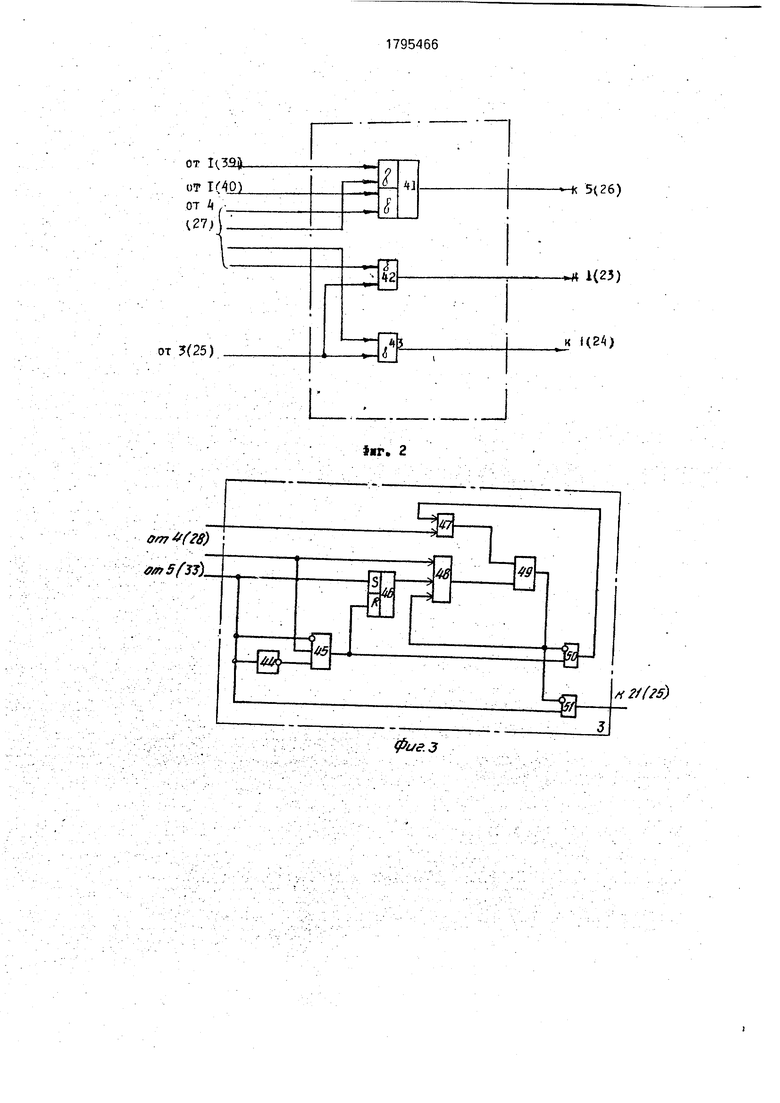

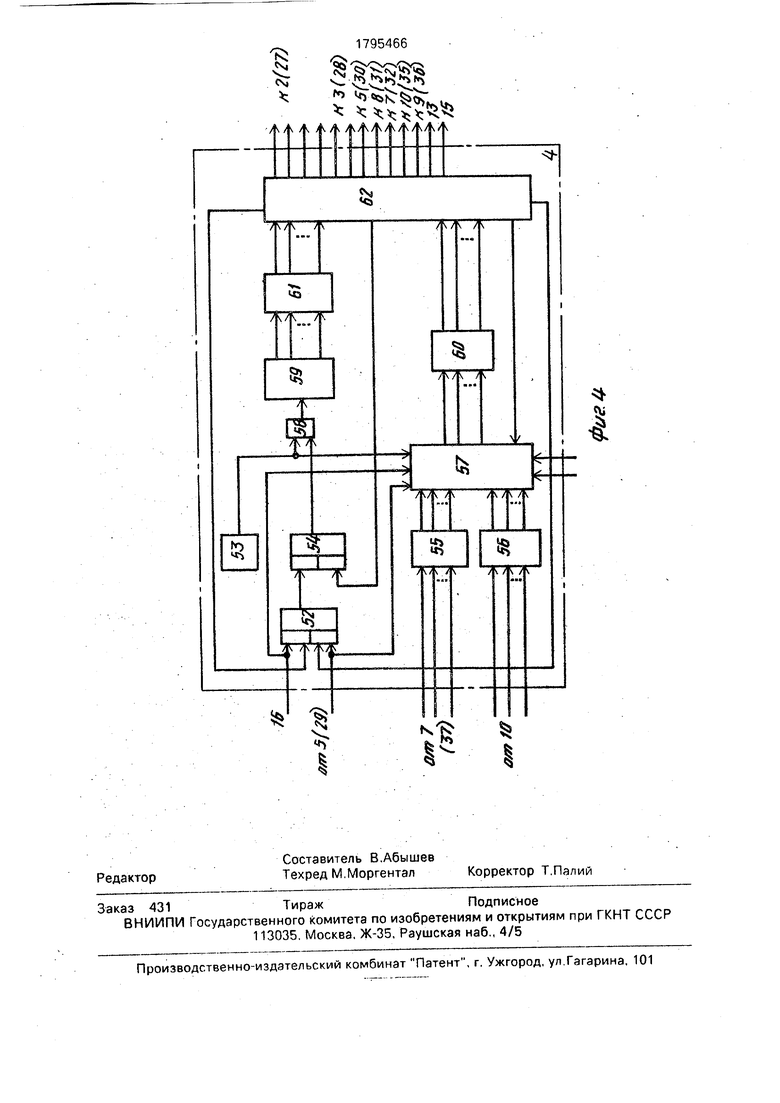

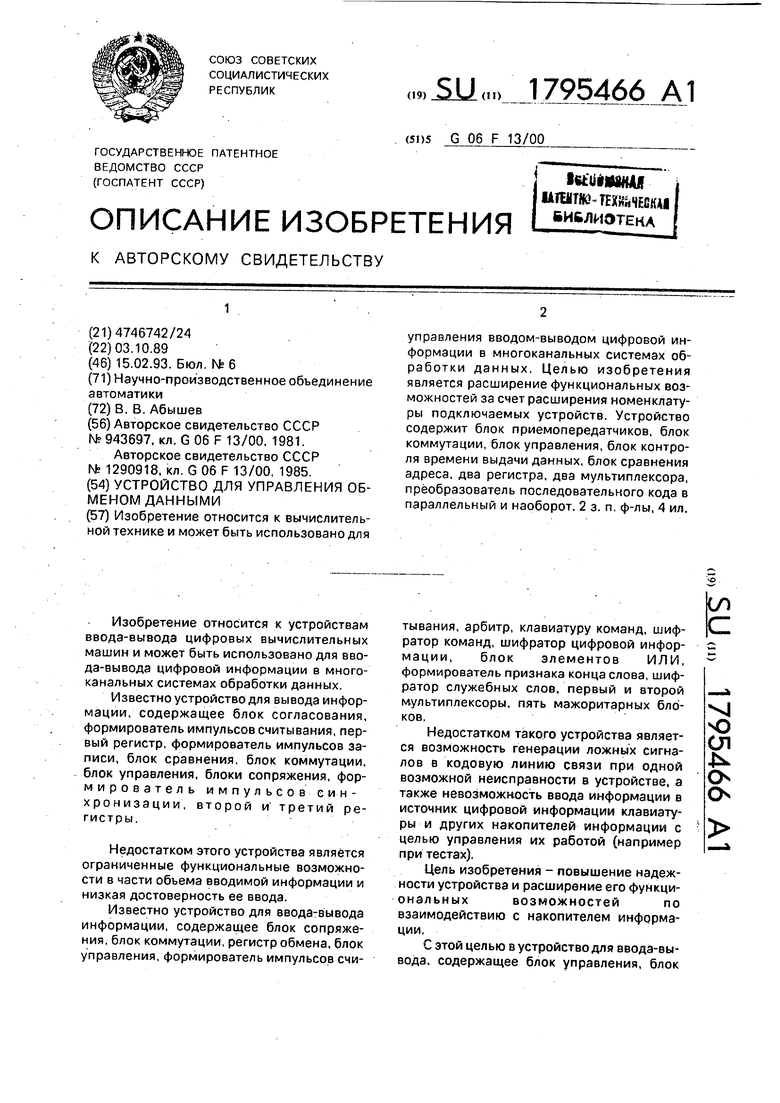

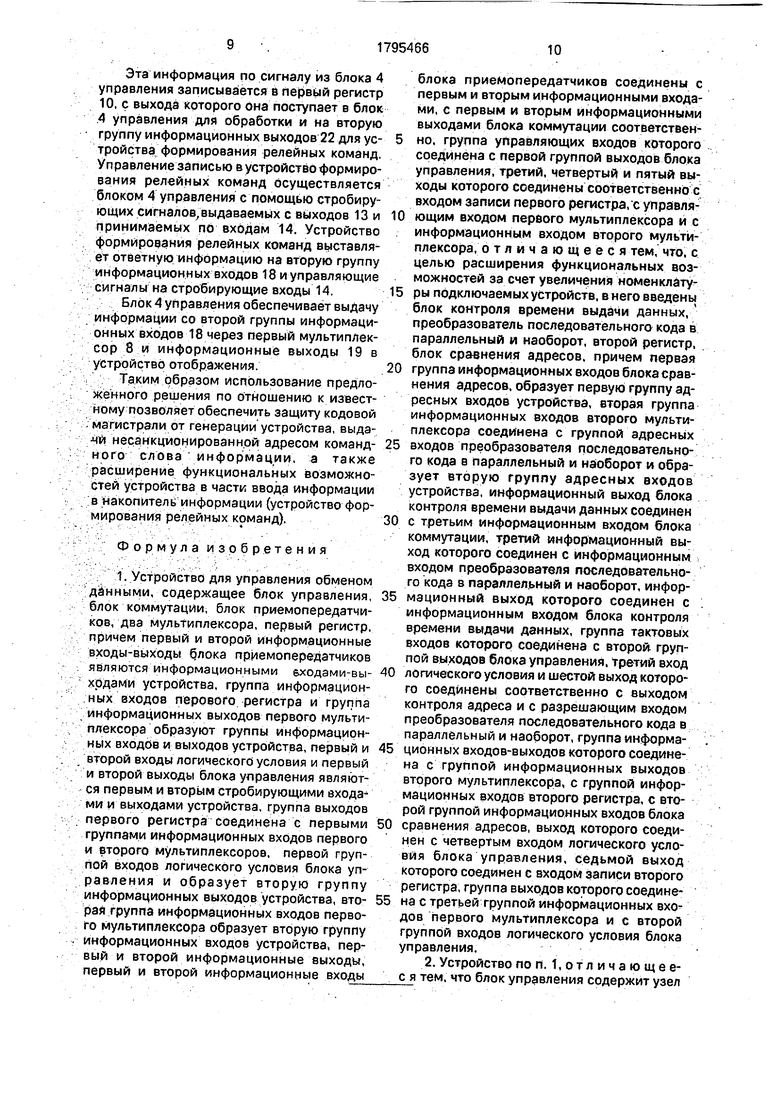

На фиг. 1 показана функциональная схема устройства; на фиг, 2 - блок-схема блока коммутации; на фиг, 3. - блок-схема блока контроля времени выдачи информации; на

5 фиг. 4 - блок-схема управления, где показаны, первый и второй входы-выходы 11 и 12 блока 1 приемопередатчиков, 13 - первый выход блока 4 управления, 14-первый вход логических условий блока 4 управления, 15

0 - второй выход блока 4 управления, 16 - второй вход логических условий блока 4 управления 17 - первая группа информационных входов блока 6 сравнения адресов, 18 - вторая группа информационных входов

:5 первого мультиплексора, 19 - информационный выход первого мультиплексора 8, 20

- информационный вход первого регистра 10, 21 - вторая группа адресных входов устройства, 22 - вторая группа йнформацион0 ных выходов устройства, 23 - первый информационный вход блока 1 приемопередатчиков, 24 - второй информационный вход блока 1 приемопередатчиков, 25 - третий информационный вход блока 2 коммута5 ции, 26 - третий информационный выход

блока 2 коммутации, 27 - первая группа

выходов блока 4 управления, 28 - вторая

группа выходов блока 4 управления, 29 третий вход логических условии блока 4 уп0 равления, 30 - шестой выход блока 4 управления, 31.- пятый выход блока 4 управления, 32 - седьмой выход блока 4 управления, 33

- информационный выход преобразователя последовательного кода в параллельный И 5 наоборот 5, 34 - информационные входы- выходы преобразователя последовательного кода в параллельный и наоборот 5, 3.5 - третий выход блока 4 управления, 36 - четвертый выход блока 4 управления, 37 - вторая группа логических условий блока 4

управления, 38 - четвертый вход логических условий блока 4 управления, 39 и 40 - первый и второй соответственно информационные входы блока 1 приемопередатчиков.

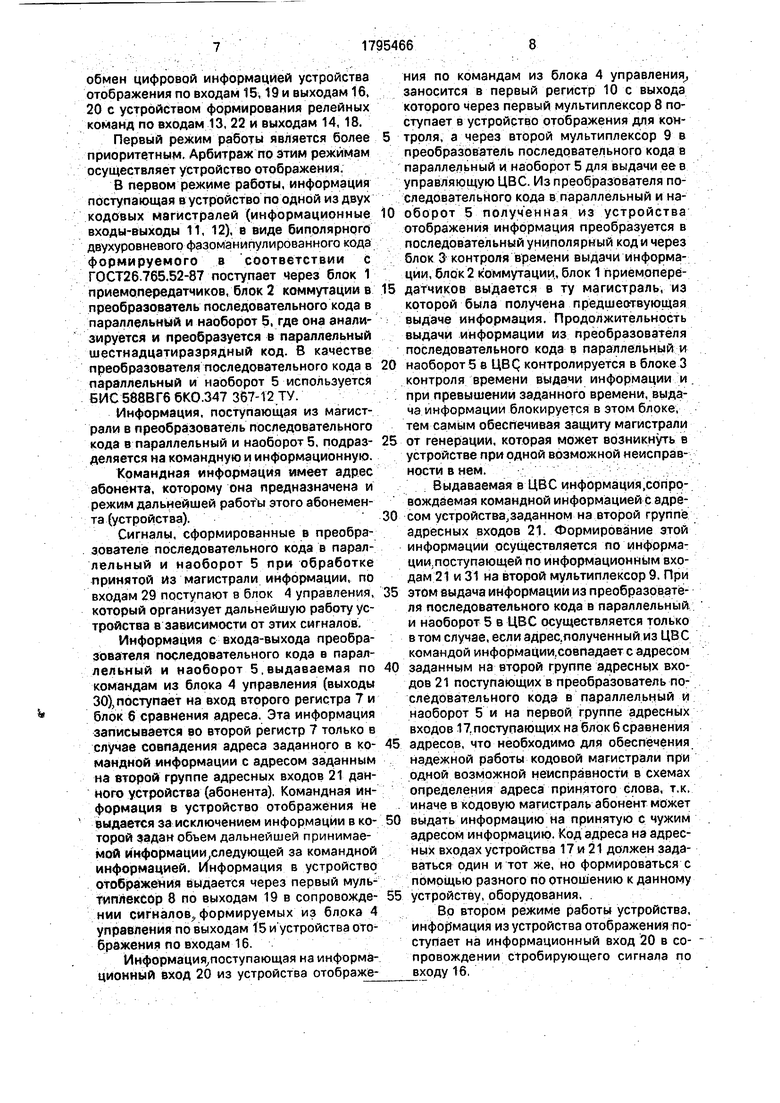

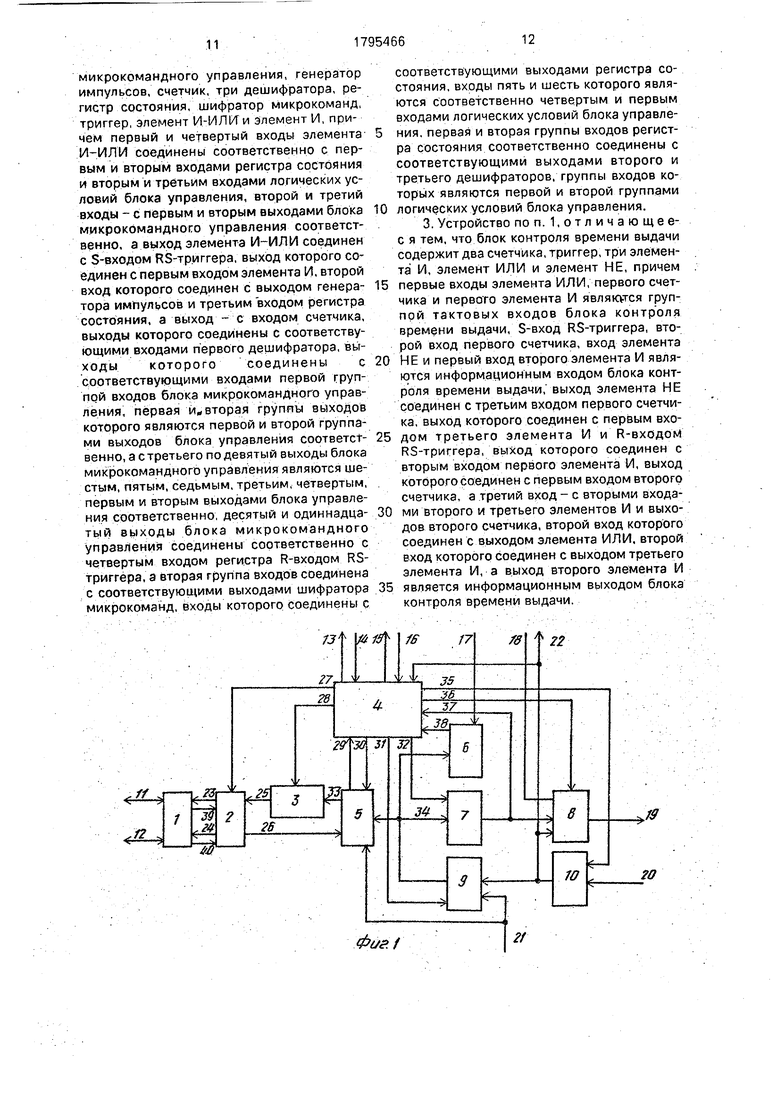

Блок 2 коммутации содержит элемент И-ИЛИ 41, элементы И 42 и 43. Первый и третий входы элемента И-ИЛИ 41 являются первым и вторым соответственно информационными входами блока 2 коммутации, второй и четвертый входы элемента И-ИЛИ 41 подключены к группе тактовых входов блока 2 коммутации, выход элементов И- ИЛИ 41 является третьим информационным выходом блока 2 коммутации, первые входы элементов И 42 и И 43 подключены к группе тактовых входов блока 2 коммутации, вторые входы элементов И 42 и И 43 являются третьим информационным входом блока 2 коммутации, выходы элементов И 42 и И 43 являются первым и вторым соответственно информационными выходами блока 2 коммутации.

Блок контроля .времени выдачи содержит элемент НЕ 44, первый счетчик 45, RS- триггер. 46, элемент ИЛИ 47, первый элемент И 48, второй счетчик 49, второй и третий элементы И 51 и И 50 соответственно, причем первые входы элемента ИЛИ 47, первого счетчика 45 и первого элемента И 48 являются группой тактовых входов блока контроля времени выдачи, S-вход RS-триггера 46, второй вход первого счетчика 45, вход элемента НЕ 44 и первый вход второго элемента И 5.1 являются информационным входом блока контроля врем ени выдачи 3. выход элемента НЕ 44 соединен с третьим входом первого счетчика 45, выход которого соединен с первым входом третьего элемента И 50 и R-входом RS-триггера 46, выход которого соединен со вторым входом первого элемента И 48, выход которого соединен с первым входом второго счетчика 49, а третий вход соединен со вторыми входами второго 51 и третьего 50 элементов И и выходом второго счетчика 49, второй вход которого соединен с выходом элемента ИЛИ 47, второй вход которого соединен с выходом третьего элемента И 50, а выход второго элемента И 51 является информационным выходом блока контроля времени выдачи 3,

Блок 4 управления содержит элемент И-ИЛИ 52 генератор импульсов 53, RS-триг- гер 54, первый и второй дешифраторы 61 и 56 соответственно, регистр состояния 57, элемент И 58, счетчик 59, шифратор 60 микрокоманд, третий дешифратор 55, блок 62 микрокомандного управления, причем первый и четвертый входы элемента И-ИЛИ 52, соединены соответственно с первым и вторым входами регистра 57 состояния и вторым и третьим входами логических условий 5 блока 4 управления, второй и третий входы - с первым и вторым соответственно выходами блока 62 микрокомандного управления, а выход элемента И-ИЛИ 52 соединен с S-входом RS-триггера 54, выход которого

0 соединен с первым входом элемента И 58, второй вход которого соединен с выходом генератора 53 импульсов и третьим входом регистра 57 состояния, а выход соединен с входом счетчика 59, выход которого соеди5 нены с соответствующими входами первого дешифратора 61, выходы которого соединены с соответствующими входами первой группой входов блока 62 микрокомандного управления, первая и вторая группы выхо0 дов которого являются первой и второй группами выходов блока 4 управления соответственно, а третий, четвертый, пятый, шестой,, седьмой, восьмой, девятый выходы блока 62 микрокомандного управления яв5 ляются шестым, пятым, седьмым, третьим, четвертым, первым и вторым выходами блока 4 управления соответственно, десятый и одиннадцатый выход блока 62 микрокомандного управления соединены соответствен0 но с четвертым входом регистра 57 состояния и R-входом RS-триггера 54, а вторая группа входов соединена с соответствующими выходами шифратора 60 микрокоманд, выходы которого соединены

5 с соответствующими выходами регистра 57 состояния, входы пять и шесть которого являются соответственно четвертым и первым входами логических условий блока 4 управления, первая и вторая группа входов реги0 стра 57 состояния соответственно соединена с соответствующими выходами второго 56 и третьего 55 дешифраторов, группы входов которых являются первой и второй группами логических условий блока

5 4 управления.

Устройство работает следующим образом.

Устройство связано с управляющей ЦВМ через две кодовые магистрали (после0 довательные биполярные информационные входы-выходы первой магистрали 11 и второй магистрали 12), устройством отображения (выходы 15, 19 и входы 16, 20) и устройством формирования релейных ко5 манд (выходы 13, 22 и входы 14, 18).

Устройство имеет два основных режима работы: первый - обмен цифровой информацией ЦВМ по информационным входам - выходам 11, 12 с устройством отображения по входам 15, 19 и выходам 16, 20, второй обмен цифровой информацией устройства отображения по входам 15,19 и выходам 16, 20 с устройством формирования релейных команд по входам 13, 22 и выходам 14, 18.

Первый режим работы является более приоритетным. Арбитраж по этим режимам осуществляет устройство отображения.

В первом режиме работы, информация поступающая в устройство по одной из двух кодовых магистралей (информационные входы-выходы 11, 12), в виде биполярного двухуровневого фазоманипулировэнного кода

формируемого в соответствии с ГОСТ26.765.52-87 поступает через блок 1 приемопередатчиков, блок 2 коммутации в преобразователь последовательного кода в параллельный и наоборот 5, где она анализируется и преобразуется в параллельный шестнадцатиразрядный код. В качестве преобразователя последовательного кода в параллельный и наоборот 5 используется БИС 588ВГ6 6К0.347 367-12 ТУ.

Информация, поступающая из магистрали в преобразователь последовательного кода в параллельный и наоборот 5, подразделяется на командную и информационную.

Командная информация имеет адрес абонента, которому она предназначена и режим дальнейшей работ ы этого абонемента (устройства).

Сигналы, сформированные в преобразователе последовательного кода в параллельный и наоборот В при обработке принятой из магистрали информации, по входам 29 поступают в блок 4 управления, который организует дальнейшую работу устройства в зависимости от этих сигналов.

Информация с входа-выхода преобразователя последовательного кода в параллельный и наоборот 5,выдаваемая по командам из блока 4 управления (выходы 30), поступает на вход второго регистра 7 и блок 6 сравнения адреса. Эта информация записывается во второй регистр 7 только в случае совпадения адреса заданного в командной информации с адресом заданным на второй группе адресных входов 21 данного устройства (абонента). Командная информация в устройство отображения не выдается за исключением информации в которой задан объем дальнейшей принимаемой информации.следующей за командной информацией. Информация в устройство отображения выдается через первый мультиплексор 8 по выходам 19 в сопровождении сигналов, формируемых из блока 4 управления по выходам 15 устройства отображения по входам 16.

Информация,поступающая на информационный вход 20 из устройства отображения по командам из блока 4 управления, заносится в первый регистр 10с выхода которого через первый мультиплексор 8 поступает в устройство отображения для контррля, а через второй мультиплексор 9 в преобразователь последовательного кода в параллельный и наоборот 5 для выдачи ее в управляющую ЦВС. Из преобразователя последовательного кода в параллельный и на0 оборот 5 полученная из устройства отображения информация преобразуется в последовательный униполярный код и через блок 3 контроля времени выдачи информации, блок 2 коммутации, блок 1 приемопере5 датчиков выдается в ту магистраль, из которой была получена предшествующая выдаче информация. Продолжительность выдачи информации из преобразователя последовательного кода в параллельный и

0 наоборот 5 в UBQ контролируется в блоке 3 контроля времени выдачи информации и, при превышении заданного времени, выдача информации блокируется в этом блоке, тем самым обеспечивая защиту магистрали

5 от генерации, которая может возникнуть в устройстве при одной возможной неисправности в нем.

: Выдаваемая в ЦВС информация,сопровождаемая командной информацией с адре0 сом устройства заданном на второй группе адресных входов 21. Формирование этой информации осуществляется по информа- ции.поступающей по информационным входам 21 и 31 на второй мультиплексор 9. При

5 этом выдача информации из преобразователя последовательного кода в параллельный, и наоборот 5 в ЦВС осуществляется только в том случае, если адрес.лолученный из ЦВС командой информации.совпадает с адресом

0 заданным на второй группе адресных входов 21 поступающих в преобразователь последовательного кода в параллельный и наоборот 5 и на первой группе адресных входов 17. поступающих на блок 6 сравнения

5 адресов, что необходимо для обеспечения

надежной работы кодовой магистрали при

одной возможной неисправности в схемах

определения адреса принятого слова, т,к,

. иначе в кодовую магистраль абонент может

0 выдать информацию на принятую с чужим адресом информацию. Код адреса на адресных входах устройства 17 и 21 должен задаваться один и тот же, но формироваться с помощью разного по отношению к данному

5 устройству, оборудования, .

Во втором режиме работы устройства, информация из устройства отображения поступает на информационный вход 20 в сопровождении стробирующего сигнала по входу 16,

Эта информация по сигналу из блока 4 управления записывается 8 первый регистр 10, с выхода которого она поступает в блок 4 управления для обработки и на вторую группу информационных выходов 22 для ус- 5 тройства формирования релейных команд. Управление записью в устройство формирования релейных команд осуществляется блоком 4 управления с помощью стробиру- ющих сигналов, выдаваемых с выходов 13 и 10 принимаемых по входам 14. Устройство . формирования релейных команд выставляет ответную информацию на вторую группу информационных входов 18 и управляющие сигналы на стробирующие входы 14.15

Блок 4 управления обеспечивает выдачу информации со второй группы информационных входов 18 через первый мультиплексор 8 и информационные выходы 19 в устройство отображения.20

Таким образом использование предложенного решения по отношению к известному позволяет обеспечить защиту кодовой магистрали от генерации устройства, выдачй несанкционированной адресом команд- 25 ного слова информации, а также расширение функциональных возможностей устройства в части ввода информации в накопитель информации (устройство формирования релейных команд).30

Формула изобретения

V 1. Устройство для управления обменом

анными, содержащее блок управления, 35 блок коммутации, блок приемопередатчиков, два мультиплексора, первый регистр, причем первый и второй информационные входы-выходы б.лока приемопередатчиков являются информационными &ходами-вы- 40 ходами устройства, группа информацион- ных входов перового регистра и группа информационных выходов первого мультиплексора образуют группы информационных входов и выходов устройства, первый и 45 второй входы логического условия и первый и второй выходы блока управления являются первым и вторым стробирующими входа ми и выходами устройства, группа выходов первого регистра соединена с первыми 50 группами информационных входов первого и второго мультиплексоров, первой группой входов логического условия блока управления и образует вторую группу информационных выходов устройства, вто- 55 рая группа информационных входов первого мультиплексора образует вторую группу информационных входов устройства, первый и второй информационные выходы, первый и второй информационные входы

блока приемопередатчиков соединены с первым и вторым информационными входами, с первым и вторым информационными выходами блока коммутации соответственно, группа управляющих входов которого соединена с первой группой выходов блока управления, третий, четвертый и пятый выходы которого соединены соответственно с входом записи первого регистра, с управляющим входом первого мультиплексора и с информационным входом второго мультиплексора, отличающееся тем, что, с целью расширения функциональных возможностей за счет увеличения номенклатуры подключаемых устройств, в него введены блок контроля времени выдачи данных, преобразователь последовательного кода в параллельный и наоборот, второй регистр, блок сравнения адресов, причем первая группа информационных входов блока сравнения адресов, образует первую группу адресных входов устройства, вторая группа информационных входов второго мультиплексора соединена с группой адресных входов преобразователя последовательного кода в параллельный и наоборот и образует вторую группу адресных входов устройства, информационный выход блока контроля времени выдачи данных соединен с третьим информационным входом блока коммутации, третий информационный выход которого соединен с информационным входом преобразователя последовательного кода в параллельный и наоборот, информационный выход которого соединен с информационным входом блока контроля времени выдачи данных, группа тактовых входов которого соединена с второй группой выходов блока управления, третий вход логического условия и шестой выход которого соединены соответственно с выходом контроля адреса и с разрешающим входом преобразователя последовательного кода в параллельный и наоборот, группа информационных входов-выходов которого соединена с группой информационных выходов второго мультиплексора, с группой информационных входов второго регистра, с второй группой информационных входов блока сравнения адресов, выход которого соединен с четвертым входом логического условия блока управления, седьмой выход которого соединен с входом записи второго регистра, группа выходов которого соединена с третьей группой информационных входов первого мультиплексора и с второй группой входов логического условия блока управления.

2. Устройство по п. 1, о т л и ч а ю щ е е- с я тем. что блок управления содержит узел

микрокомандного управления, генератор импульсов, счетчик, три дешифратора, ре- гистр состояния, шифратор микрокоманд, триггер, элемент И-И Л И и элемент И, причем первый и четвертый входы элемента И-ИЛИ соединены соответственно с первым и вторым входами регистра состояния и вторым и третьим входами логических условий блока управления, второй и третий входы - с первым и вторым выходами блока микрокбмандного управления соответственно, а выход элемента И-ИЛИ соединен с S-входом RS-триггера, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом генератора импульсов и третьим входом регистра состояния, а выход с входом счетчика, выходы которого соединены с соответствующими входами первого дешифратора, выходы которого соединены с соответствующими входами первой группой входов блока микрокомандного управления, первая и,вторая группы выходов которого являются первой и второй группами выходов блока управления соответственно, а с третьего по девятый выходы блока микрокомандного управления являются шестым, пятым, седьмым, третьим, четвертым, первым и вторым выходами блока управления соответственно, десятый и одиннадцатый выходы блока микрокомандного управления соединены соответственно с четвертым входом регистра R-входом RS- триггера, а вторая группа входов соединена с соответствующими выходами шифратора микрокоманд, входы которого соединены с

соответствующими выходами регистра состояния, входы пять и шесть которого являются соответственно четвертым и первым входами логических условий блока управле- ния, первая и вторая группы входов регистра состояния соответственно соединены с соответствующими выходами второго и третьего дешифраторов, группы входов которых являются первой и второй группами 0 логических условий блока управления.

3.Устройство поп. 1, отличаю щее- с я тем, что блок контроля времени выдачи содержит два счетчика, триггер, три элемента И, элемент ИЛИ и элемент НЕ, причем 5 первые входы элемента ИЛИ, первого счетчика и первого элемента И являются группой тактовых входов блока контроля времени выдачи, S-вход RS-триггера, второй вход первого счетчика, вход элемента 0 НЕ и первый вход второго элемента И являются информационным входом блока контроля времени выдачи, выход элемента НЕ соединен с третьим входом первого счетчика, выход которого соединен с первым вхо- 5 дом третьего элемента И и R-входоМ RS-триггера, выход которого соединен с вторым входом первого элемента И, выход которого соединен с первым входом второго счетчика, а третий вход - с вторыми входа- 0 ми второго и третьего элементов И и выходов второго счетчика, второй вход которого соединен с выходом элемента ИЛИ. второй вход которого соединен с выходом третьего элемента И, а выход второго элемента И 35 является информационным выходом блока контроля времени выдачи.

(stj/г

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Двухуровневое устройство для управления памятью микрокоманд | 1984 |

|

SU1247882A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1716512A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1278869A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления вводом-выводом цифровой информации в многоканальных системах обработки данных, Целью изобретения является расширение функциональных возможностей за счет расширения номенклатуры подключаемых устройств. Устройство содержит блок приемопередатчиков, блок коммутации, блок управления, блок контроля времени выдачи данных, блок сравнения адреса, два регистра, два мультиплексора, преобразователь последовательного кода в параллельный и наоборот. 2 з. п. ф-лы, 4 ил.

т

3tj

Г

г J«f

1795466

S&N sj Ън-jSN

t&

i

| Устройство для вывода информации | 1981 |

|

SU943697A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1290918,кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-15—Публикация

1989-10-03—Подача