:5) МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ ИНТЕРФЕЙС ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Резервированное многоканальное запоминающее устройство | 1980 |

|

SU942142A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1702434A1 |

| Устройство для обмена информацией | 1986 |

|

SU1322299A1 |

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

| Резервированное устройство | 1982 |

|

SU1102068A1 |

| Резервированная система | 1977 |

|

SU703818A1 |

| Устройство для управления реконфигурацией резервированной системы | 1982 |

|

SU1040632A1 |

1

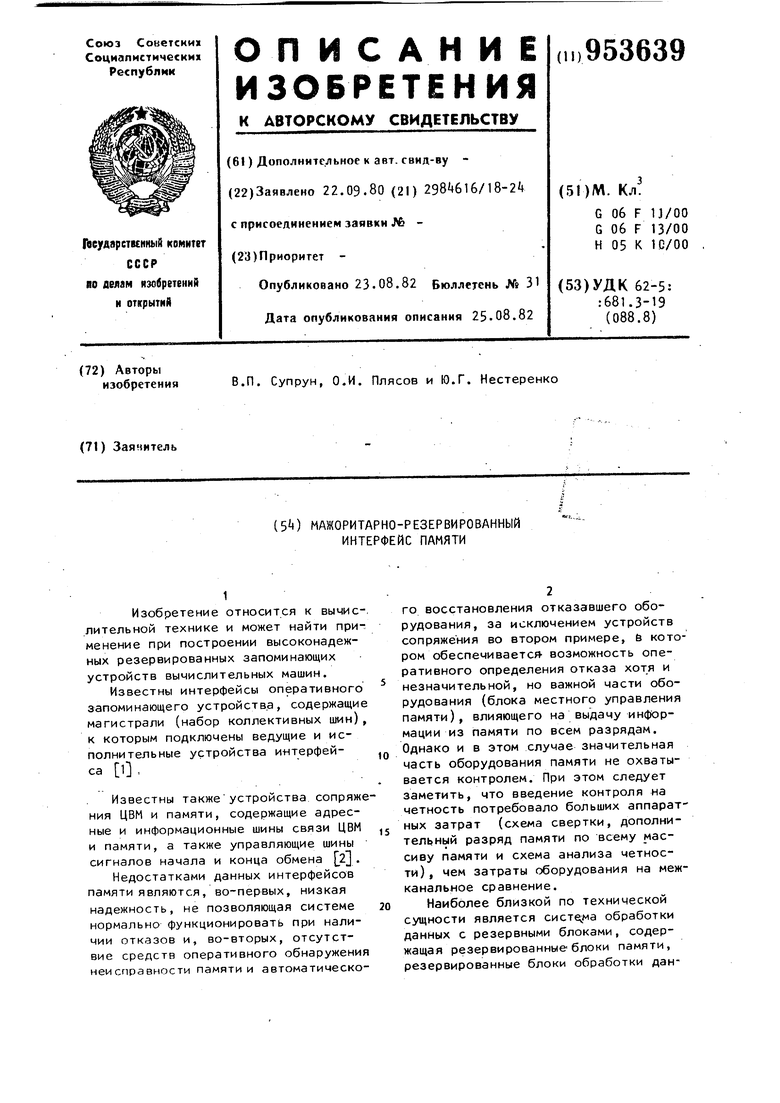

Изобретение относится к вычис-: лительной технике и может найти применение при построении высоконадежных резервированных запоминающих устройств вычислительных машин.

Известны интерфейсы оперативного запоминающего устройства, содержащие магистрали (набор коллективных шин), к которым подключены ведущие и исполнительные устройства и+нтерфейса 1,

Известны такжеустройства сопряжения ЦВМ и памяти, содержащие адресные и информационные шины связи ЦВМ и памяти, а также управляющие шины сигналов начала и конца обмена 2.

Недостатками данных интерфейсов памяти являются, во-первых, низкая надежность, не позволяющая системе нормально функционировать при наличии отказов и, во-вторых, отсутствие средств оперативного обнаружения неисправности памяти и автоматическоГО восстановления отказавшего оборудования, за исключением устройств сопряжения во втором примере, в котором обеспечивается- возможность оперативного определения отказа хотя и незначительной, но важной части оборудования (блока местного управления памяти), влияющего на выдачу информации из памяти по всем разрядам. Однако и в этом случае значительная часть оборудования памяти не охватывается контролем. При этом следует заметить, что введение контроля на четность потребовало больших аппаратных затрат (схема свертки, дополнительный разряд памяти по всему массиву памяти и схема анализа четности), чем затраты оборудования на межканальное сравнение.

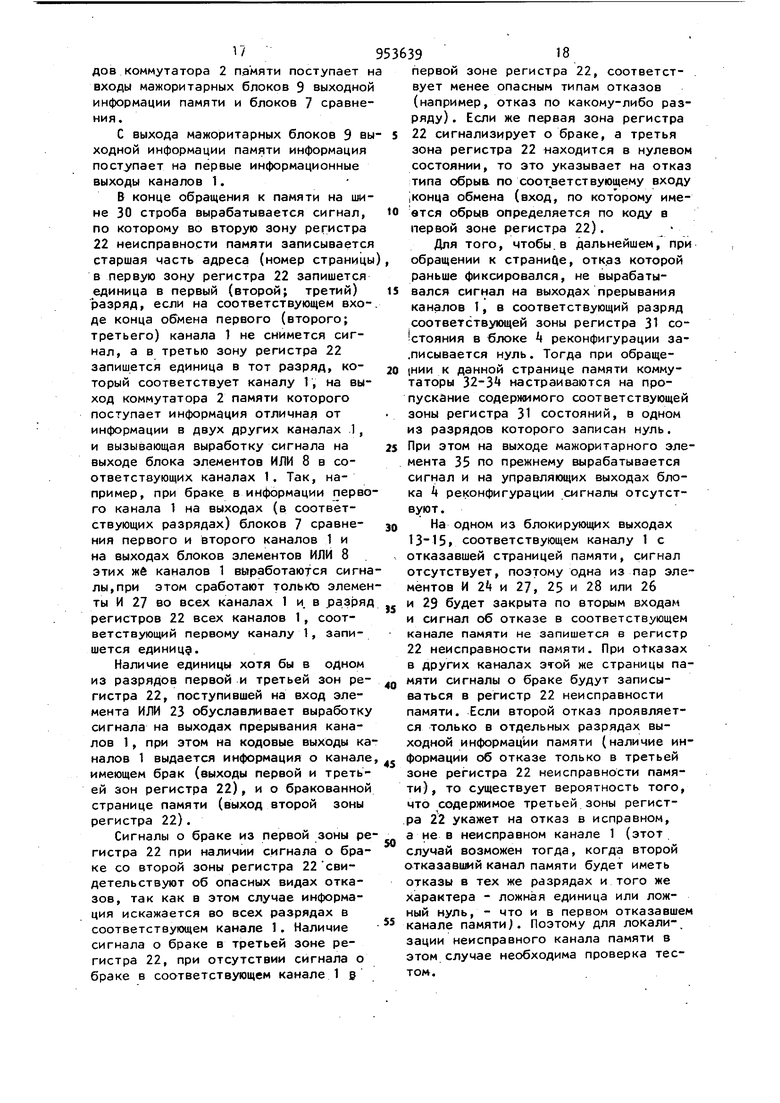

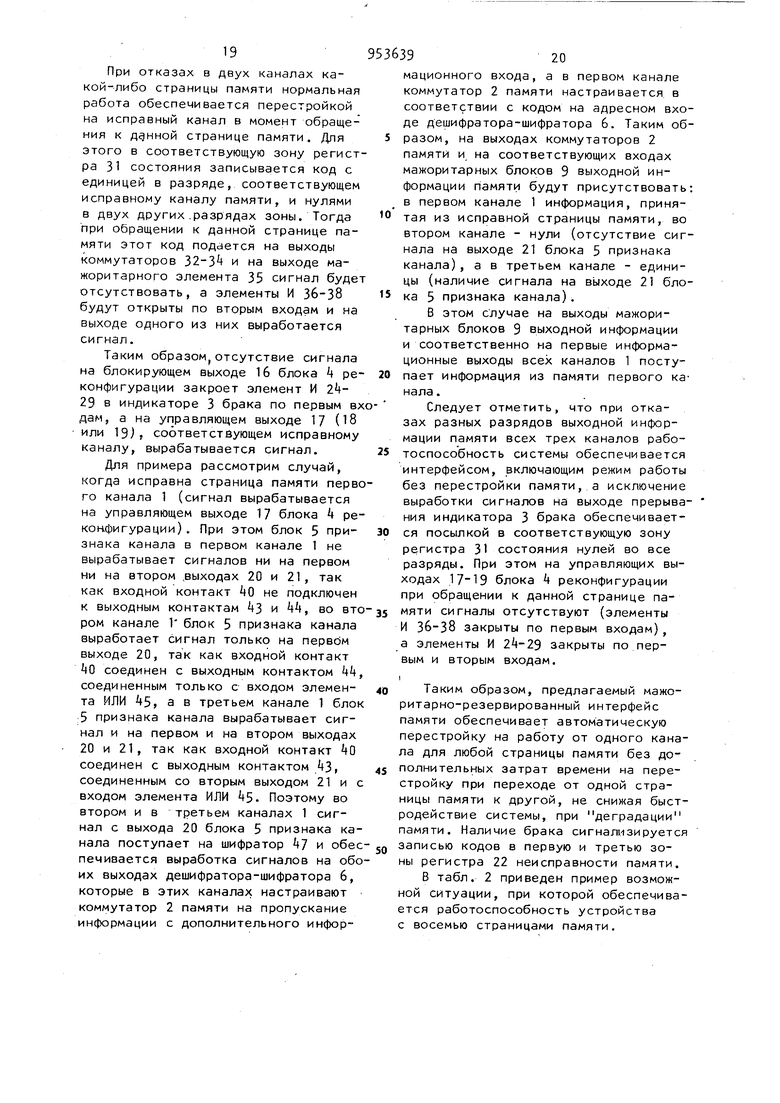

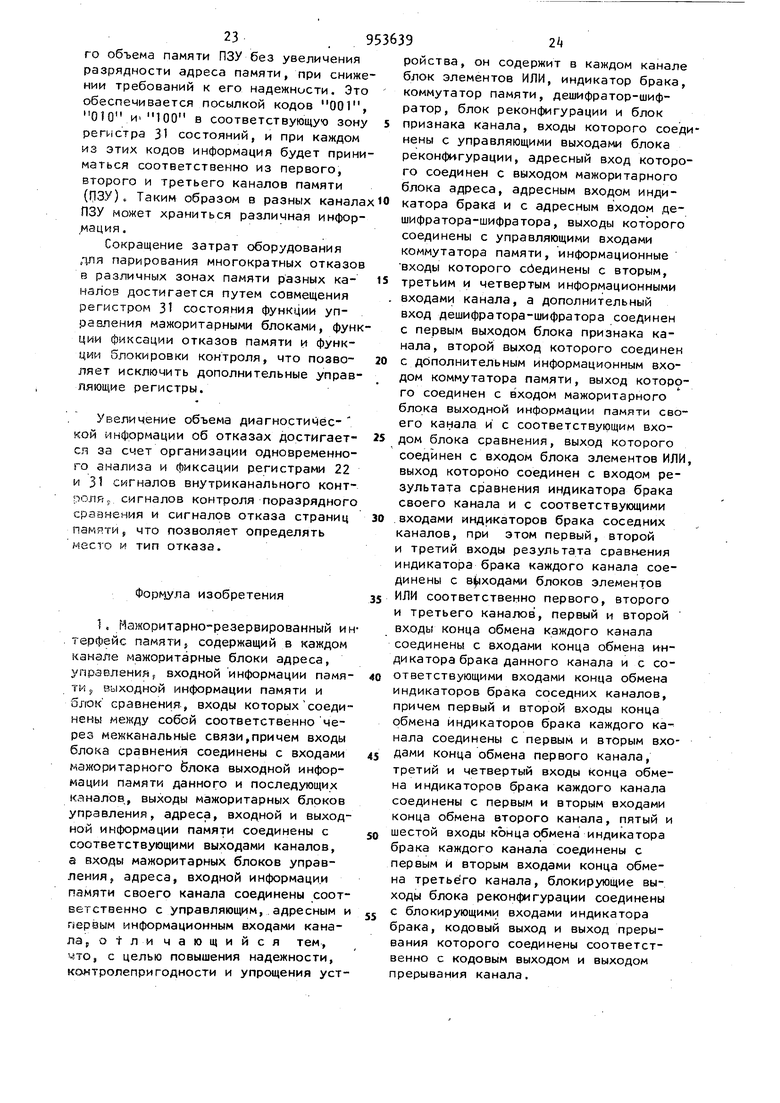

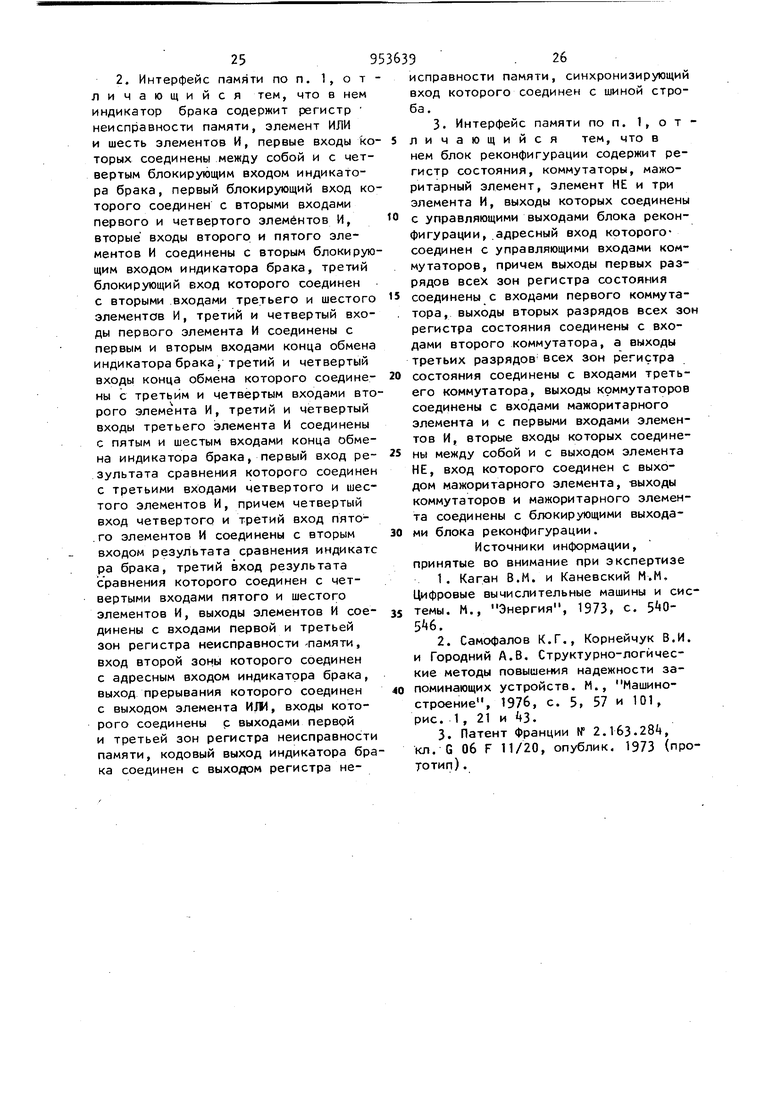

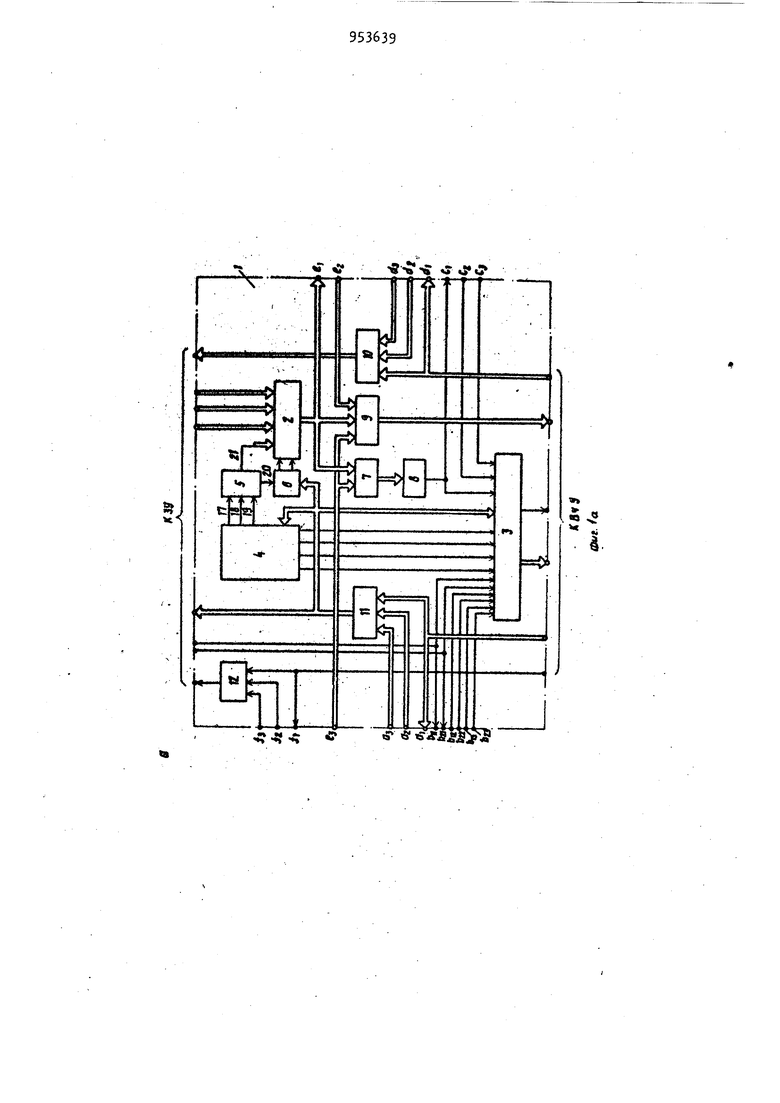

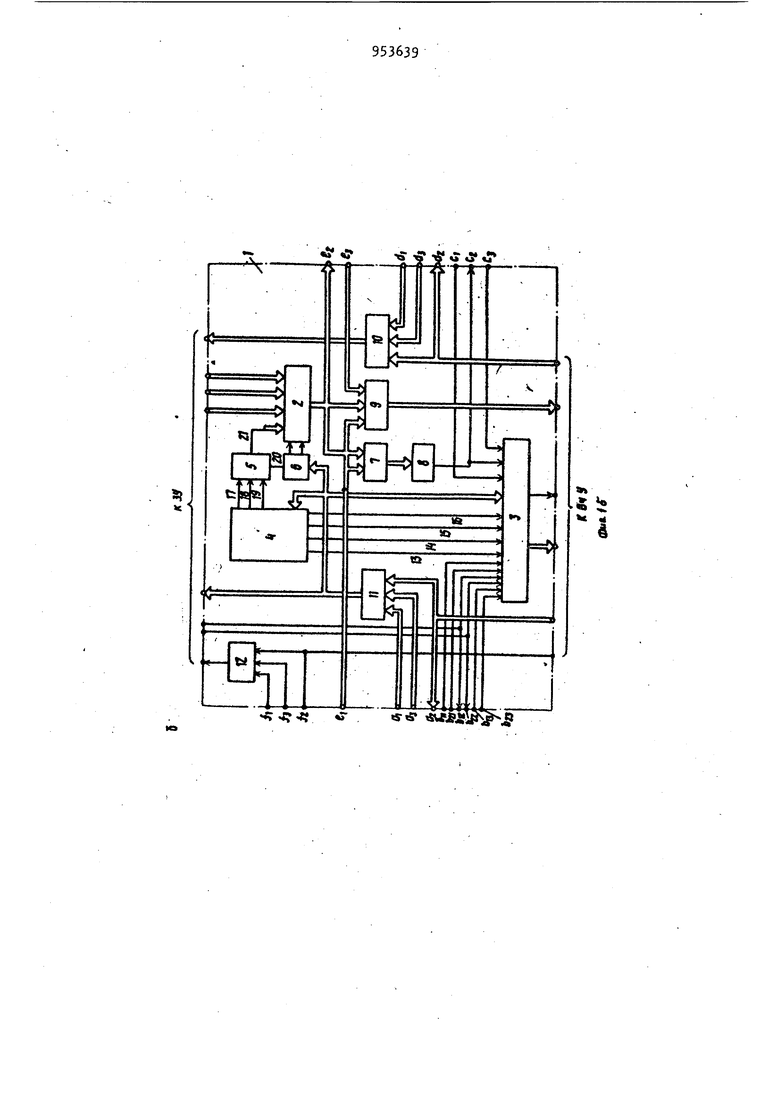

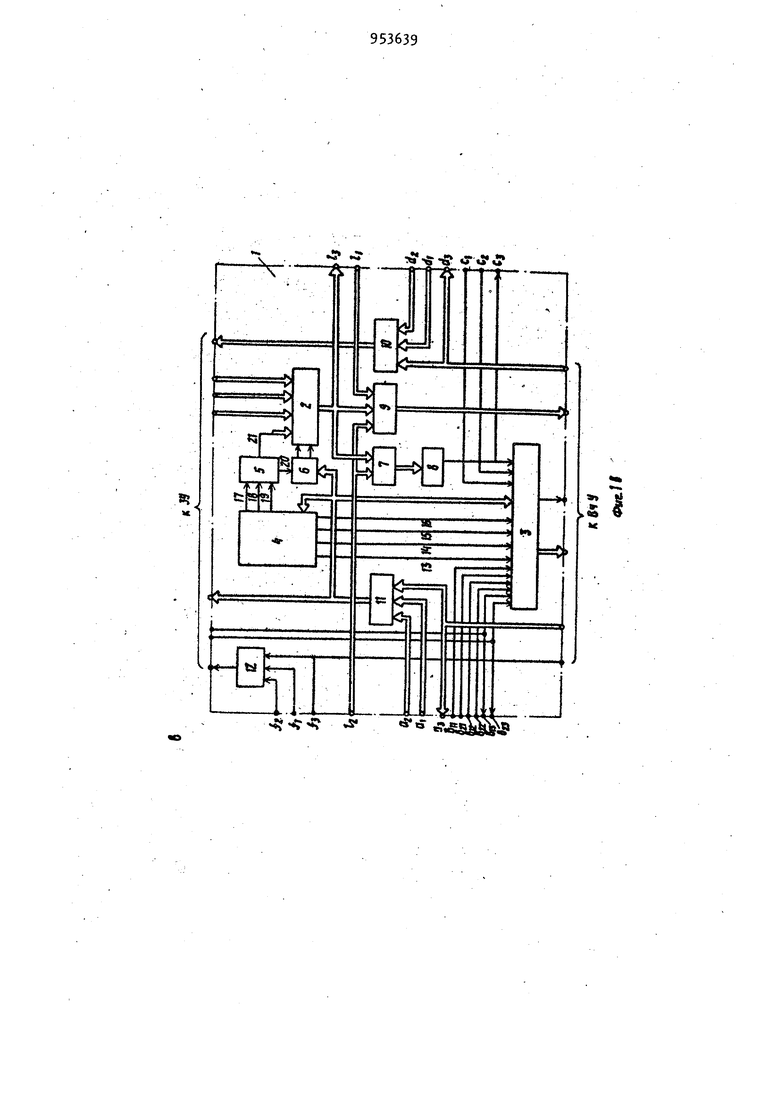

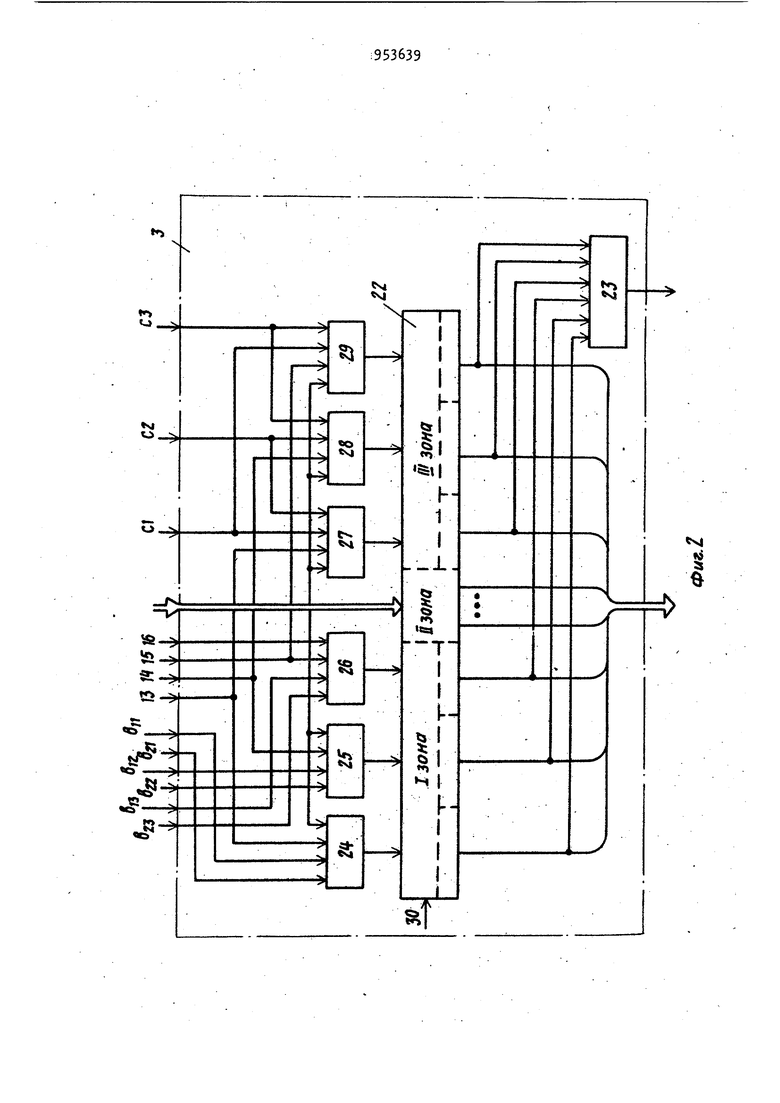

Наиболее близкой по технической сущности является систе;ма обработки данных с резервными блоками, содержащая резервированные блоки памяти, резервированные блоки обработки данных, соединенные между собой через мажоритарные элементы, между входами своего и соседнего каналов которы включены схемы сравнения З. Недостатками данного устройства являются не достаточно высокая надеж ность, так как не обеспечивается пра вильное функционирование системы при отказах в двух и некоторых отказах в трех каналах памяти и отсутствие информации о том, в какой части, оборудования памяти произошел отказ, при этом сигнал об отказе памяти поступает в блоки обработки данных только двух из трех каналов, что недостаточно. Общим недостатком известных устройств является то, что они требуют больших затрат оборудования на выпол нение функции управления- мажоритарны ми органами, функции фиксации отказо и функции блокировки контроля. Целью изобретения является повыше ние надежности, контролепригодности и упрощения устройства. Поставленная цель достигается тем что мажоритарно-резервированный интерфейс памяти, содержащий в каждом канале мажоритарные блоки адреса, уп равления, входной информации памяти, выходной информации памяти и блок сравнения, входы которых соединены между собой соответственно через меж канальные связи, причем входы блока сравнения соединены с входами мажоритарного блока выходной информации памяти данного и последующего каналов, выходы мажоритарных блоков управления, адреса, входной и выходной информации памяти соединены с соответствующими выходами каналов, а входы мажоритарных блоков управления адреса и входной информации памяти своего канала соединены соответственно с управляющим, адресным и пер вым информационным входами канала, содержит в каждом канале блок элементов ИЛИ, индикатор брака, коммутатор памяти, дешифратор-шифратор, блок реконфигурации и блок признака канала, входы которого соединены с управляющими выходами блока реконфигурации, адресный вход которого соединен с выходом мажоритарного блока адреса, адресным входом индикатора брака и с адресным входом дешифратора-шифратора, выходы которого соединены с управляющими входами коммутатора памяти, информационные вхрды которого соединены с вторым, третьим и четвертым информационными входами канала. Дополнительный вход дешифратора-шифратора соединен с первым выходом блока признака канала, второй выход которого соединен с дополнительным информационным входом коммутатора памяти, выход которого соединен с входом мажоритарного блока выходной информации памяти своего канала и с соответствующим входом блока сравнения, выход которого соединен с входом блока элементов ИЛИ, выход которого соединен с входом результата сравнения индикатора брака своего канала и с соответствующими входами индикаторов брака соседних каналов, при этом, первый, второй и третий входы результата сравнения индикатора брака каждого канала соединены с выходами блоков элементов ИЛИ соответственно первого, второго и третьего каналов. Первый и второй входы конца обмена каждого канала соединены с входами конца обмена индикатора брака данного канала и с соответствующими входами конца обмена индикаторов брака соседних каналов, причем первый и второй входы конца обмена индикаторов брака каждого канала соединены с первым и вторым входами конца обмена первого канала, третий и четвертый входы конца обмена индикатора брака каждого канала соединены с первым и вторым входами конца обмена второго канала, пятый и шестой входы конца обмена индикатора брака каждого канала соединены с первым и вторым входами конца обмена третьего канала,-блокирующие выходы блока реконфигурации соединены с блокирующими входами индикатора брака, кодовый выход.и выход прерывания которого соединены соответственно с кодовым выходом и выходом прерывания канала, при этом индикатор брака содержит регистр неисправности памяти, элемент ИЛИ и шесть элементов И, первые входы которых соединены между собой и с четвертым блокирующим входом индикатора брака, первый блокирующий вход которого соединен с вторыми входами первого и четвёртого элементов И, вторые входы второго и пятого элементов И соединены с вторым блокирующим входом индикатора брака, третий блокирующий вход которого соединен с вторыми входами третьего и шестого элементов И, третий и четвертый входы первого элемента И соединены с первым и вторым входами конца обмена индикатора брака, третий и четвертый входы конца обмена которого соединены с третьим и четвертым входом второго элемента И, третий и четвертый входы третьего элемента И соединены с пятым и шестым входами конца обмен индикатора брака, первый вход резуль тата сравнения которого соединен с третьими входами четвертого и шестого элементов И, причем четвертый вхо четвертого и третьий вход пятого эле ментов И соединены с вторым входом результата сравнения индикатора брака, третий вход результата сравнения которого соединен с четвертыми входа ми пятого и шестого элементов W, выходы элементов И соединены с входами первой и третьей зон регистра неисправности памяти, вход второй зоны которого соединен с адресным входом индикатора брака, выход прерывания которого соединен с выходом элемента ИЛИ, входы которого соединены с выходами первой и третьей зон регист,ра неисправности памяти, кодовый выход индикатора брака соединен с выходом регистра неисправности памяти, синхронизирующий вход которого соединен с шиной строба. Блок реконфигурации содержит регистр состояния, коммутаторы, мажоритарный элемент, элемент НЕ и три элемента И, выходы которых соединены с управляющими выходами блока реконфигурации, адресный вход которого соединен с управляющими входами коммутаторов, причем, выходы первых раз рядов всех зон регистра состояния |соединены с входами первого коммутатора, выходы ёторых разрядов всех :зон регистра состояния соединены с входами второго коммутатора, а выходы третьих разрядов всех зон регистра состояния соединены с входами третьего коммутатора, выходы комму таторов соединены с входами мажоритарного элемента и с первыми входами элементов И, вторые входы которых соединены между собой и с выходом эле мента НЕ, вход которого соединен с выходом мажоритарного элемента, выходы коммутаторов и мажоритарного элемента соединены с блокирующими выходами блока реконфигурации. Это позволило сохранить работоспособность вычислительных средств,, использующих предложенное устройство при одновременных отказах в двух каналах памяти в стольких страницах памяти сколько трехразрядных зон имеет регистр состояния в блоке реконфигурации. При этом перестройка на исправный канал при переходе от одной страницы памяти к другой производится без снижения быстродействия работы устройства, с учетом того, что в разных страницахпамяти исправными могут оказаться разные каналы. Кроме того, сигнал об отказе какоголибо канала памяти при обращении к любой зоне памяти поступает в три канала, однозначно указывая на канал (первая и третья зоны регистра неисправности памяти) и на зону памяти, при работе с которой получен брак (вторая зона регистра неисправности памяти). При этом наличие сигналов о браке в первой и третьей зонах регистра неисправности памяти указывает на отказ в устройстве управления памяти; если на отказ указывает только третья зона регистра неисправности памяти то это значит, что устройство управления памяти исправно. Если на отказ указывает только первая зона регистра неисправности памяти, то это указывает на обрыв связи между памятью и интерфейсом по входу конца обмена соответствующего канала интерфейса. На фиг. 1а, 1Ь дана блок-схема трёх каналов мажоритарне-резервированного интерфейса памяти; на фиг. 2 - структурная схема индикатора брака; на фиг. 3 - структурная схема блока реконфигурации; на фиг. - структурная схема блока признака канала для каждого канала; на фиг. 5 - структурная схема дешифратора-шифратора; на фиг. 6 .- структурная схема регистра нeиcпpaвнodти памяти. Предлагаемый мажоритарно-резервированный интерфейс памяти (фиг. 1аТЬ) содержит три канала 1. Каждый канал 1 содержит коммутатор 2 памяти, индикатор 3 брака, блок 4 реконфигурации, блок 5 признака канала, дешифратор-шифратор 6, блок 7 сравнения, блок элементов ИЛИ 8, мажо- ритарный блок 9 выходной информации памяти, мажоритарный блок 10 входной информации памяти, мажоритарный блок П адреса и мажоритарный блок 12 управления, выход которого соединен с управляющим выходом канала 1. Блок элементов ИЛИ 8 представляет собой элемент ИЛИ, число входов которого равно разрядности информации. Названия мажоритарный блок и блок сравнения обозначают многоразрядные блоки, в каждом разряде которых задействован мажоритарный элемент и .элемент сравнения, соотретственно. Адресный вход канала 1 соединен г межканальным адресным выходом , о) и с входом мажоритарного блока 11 адреса, д|эугие входы кот рого соединены с межканальными адресными входами а и Оа ( 01 и Oi ; i)f а выход мажоритарного блок 11 адреса соединен с адресными входами индикатора 3 брака, блока k реконфигурации и дешифратора-шифратора бис адресным выходом канала 1. Пер вый и второй входы конца обмена соединены с первым и вторым (третьим и четвертым; пятым и шестым) входами конца обмена индикатора 3 брака и с межканальными выходами конца обмена Ь и Ь2 первая цифра двухзначного индекса при Ъ обозначает номер выхода (входа), а вторая цифра индекса обозначает номер канала 1, являющего ся источником сигнала (Ь иЬ22; иЪло) канала 1, межканальные входы конца обмена Ъ 2 22 Ь |з и Ъи nbji Ъ t bji ) и Ъ/22 ) которого соединены с трет им, четвертым, пятым и шестым (пятым шестым, первым и вторым; первым, вто рым, третьим и четвёртым) входами конца обмена индикатора 3 брака. При обозначениях используются межканаль- ные выходы и входы для первого канала 1, для второго и третьего каналов 1 обозначения указываются в скобках. Входы конца обмена - это входы устройства, на которые из памяти выдает ся сигнал об окончании цикла работы памяти, т.е. о готовности информации Выход блока 7 сравнения соединен с входом блока элементов ИЛИ 8, выход которого соединен с первым (вторым; третьим) входом результата сравнения индикатора 3 брака и с межканальным .выходом 0(0 Cj) результата сравнения канала 1, межканальные входы C,jC(C и С;,; С и С2) результата сравнения которого соединены со вторым и третьим (третьим и первым; первым и вторым) входами результата сравнения индикатора 3 брака, кодовой выход и выход прерывания которого соединены соответственно с кодовым выходом и выходом прерывания канала 1. Первый лнформационный вход канала 1 соединен с межканальным информационным выходом d ((3 2 3, первым входом мажоритарного блока 10 входной информации памяти, другие входы которого соединены с межканальными информационными входами d-t исЗ,(/4. 1 1 1 - З и иd/2) канал 1, первый информационный выход которого соединен с выходом мажоритарного блока 9 вьг ходной информации памяти, первый вход которого .соединен с первым входом блока 7 сравнения, с выходом коммутаTiopa 2 памяти и с межканальным информационным выходом е ( Sjj 63 канала 1, межканальЯый-информационный входйзСе,,; е) которого соединен с вторым входом мажоритарного блока 9 выходной информации памяти, третий вход которого соединен с вторым входом блока 7 сравнения и с межканальным информационным входом 6( 63) канала 1. Управляющий вход канала 1 соединен межканальнымвыходом (2 3 управления и с первым входом мажоритарного блока 12 управления, другие входы которого соединены с межканальными входами 2 и{({ и , , { и f2) управления. Первый, второй, третий и четвертый блокирующие выходы 13-16 блока t (фиг. 2) реконфигурации соединены с первым, вторым, третьим и четвертым блокирующими входами индикатора 3 брака. Первый, второй и третий управляющие выходы 17-19 блока k реконфигурации соединёйы с первым, вторым и третьим входами блока 5 признака канала, первый выход 20 которого соединен с дополнит-ельным входом дешифратора-шифратора 6, выходы которого соединены с управляющими входами коммутатора 2 памяти. Второй выход 21 блока 5 признака канала соединен с дополнительным нформационным входом коммутатора 2 памяти, первый, второй и третий информационные входы которого соединены с вторым, третьим и четвертым инфор-. мационными входами канала 1, второй информационный выход которого соединен с выходом мажоритарного блока 10 входной информации памяти. Каналы 1 соединяются таким образом межканальными связями, что одна и та же межка нальная связь указана одинаково, например, межканальный адресный выход а первого канала соединен с межканальными адресными входами а второго и третьего каналов 1, Буквенные обозначения межканальных входов и выходов с одними и теми же индексами означают одни и те .же межканальные связи, которые на чертеже не проложены, чтобы не затемнять чертеж. Индикатор 3 брака (фиг. 2) содержит регистр 22 неисправности памяти элемент ИЛИ 23 и шесть элементов И . Регистр 22 неисправности памяти запоминает и выдает информацию о странице памяти с неисправностью (вторая зона регистра 22) и об отказавших каналах в данной странице,, причем первая зона фиксирует отказы, приводящие к выдаче неверной информации по всем разрядам, а третья зона фиксирует отказы от схем поразрядного сравнения. Элемент ЛИ 23 сигнализирует о наличии брака,а элементы И 24-29 выделяют канал в котором отказала память. Выходы элементов И соединены с входами первой зоны регистра 22 неисправности памяти, входы третьей зоны которого соединены с выходами элементов И 27-29. Адресный вход индикатора 3 брака соединен с входом второй зоны регистра 22 неисправности памяти, синхронизирующий вход которого соединен с шиной 30 строба. Выходы всех трех зон регистра 22 неисправности памяти соединены с кодовым выходом индикато ра 3 брака, выход прерывания которого соединен с выходом элемента ИЛИ 23 входы которого соединены с выходами первой и третьей зон регистра 22 не.исправности памяти. Первые входы эле ментов И 24-29 соединены с четвертым блокирующим входом индикатора 3 брака, первый блокирующий вход которого соединен со вторыми входами элемен- , тов И 24 и 27. Вторые входы элементов И 25 и 28 соединены с вторым бло кирующим входом индикатора 3 брака, третий блокирующий вход которого соединен с вторыми входами элементов И 2б и 29. Третий и четвертый входы элемента И 24 соединены с первым и вторым входами конца обмена индикато ра 3 брака, третий и четвертый входы конца обмена которого соединены с третьим и четвертым входами элемента И 25. Третий и четвертый входы элемента И 26 соединены с пятым и шестым входами обмена индикатора 3 брака, первый вход результата сравнения которого соединен с третьими входами элементов И 27 и 29. Четвертый вход элемента И 27 соединен с третьим входом элемента И 28 и с вторым входом результата сравнения индикатора 3 брака, третий вход результата сравнения которого соединен с четвертыми входами элементов И 28 и 29. Блок 4 реконфигурации (фиг. 3) содержит регистр 31 состояния, коммутаторы 32-34, мажоритарный элемент 35, элементы И 36-38 и элемент НЕ 39, выход которого соединен со вторыми входами элементов И 36-38, выходы которых соединены соответственно с первым, вторым и третьим управлящими выходами 17-19 блока 4 реконфигурации, Первый, второй и третий блокирующие выходы 13-15 которого соединены соответственно с выходами коммутаторов 32-34, с первыми входами элементов И 36-38 и с входами мажоритарного элемента 35, выход которого соединен с входом .элемента НЕ 39 и с четвертым блокирующим выходом 16 блока 4 реконфигурации, адресный вход которо-. го соединен с управляющими входами коммутаторов 32-34. Регистр 31 состояния разбит на зоны по три разряда в каждой. Каждая зона регистра 31 состояния приводится в соответствие группе адресов памяти (назовем страницей памяти). Выходы первых разрядов всех зон регистра 31 состояния соединены с входами первого коммутатора 32, который приводится в соответствие к работе от памяти первого канала 1 интерфейса. Выходы вторых разрядов всех зон регистра 31 состояния соединены с входами второго коммутатора 33, который приводится -в соответствие к работе от памяти второго канала 1 интерфейса. Выходы третьих разрядов всех зон регистра 31 состояния соединены с входами третьего коммутатора 34, который приработе от водится в соответствие к памяти третьего канала 1 интерфейса, Соответствие регистра 31 состояния . адресуемомуполю памяти показано в табл. 1.

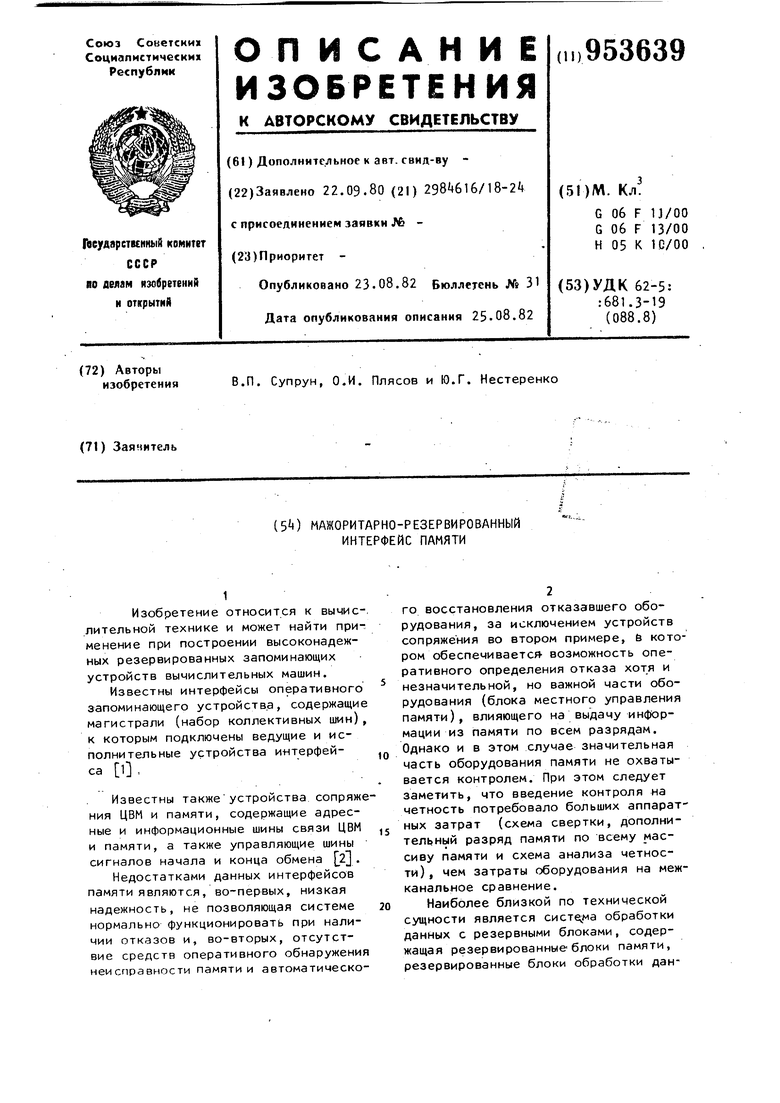

Разряды каждой зоны регистра

..I......L...

1-я зона

1-я страница 1-го канала

п-я зона

п-я страница 1-го канала

Блок k реконфигурации служит для запоминания состояния об отказах в страницах памяти, для блокировки запоминания отказов существующих и уже известных, а также для) управления перестройкой памяти на один канал, при необходимости.

Каждый блок 5 признака канала {фиг, k) содержит входные контакты tO- 2Jсоединенные соответственно с первыми, вторым и третьим входами блока 5 признака канала, выходные контакты 3 и f и элемент ИЛИ 5 выход которого соединен с первым выходом 20 блока 5 признака канала, второй выход 21 которого соединен с выходным контактом 3 и первым входом элемента ИЛИ j второй вход которого соединен с выходным контактом kk. Соединение входных контактов и выходных контактов «З и производится таким образом, что в первом канале 1 входной контакт О не задействован, входной контакт Ц} соединен с выходным контактом 3, входной контакт k2 соединен с выходным контактом . Во втором канале входной контакт 0 соединен с выходным контактом kk, входной контакт 1(1 не задействован,, а входной контакт А соединен с выходным контактом 43. В третьем канале 1 входной контакт соединен с выходным контактом 3, входной контакт 1 соединен с выходным контактом j, а входной контакт 2 не задействован.

I

страница1-я страница канала 3-го канала

то

(U

о

,Ш

о

0)

и

а а 4

страница

п-я страница канала 3-го канала

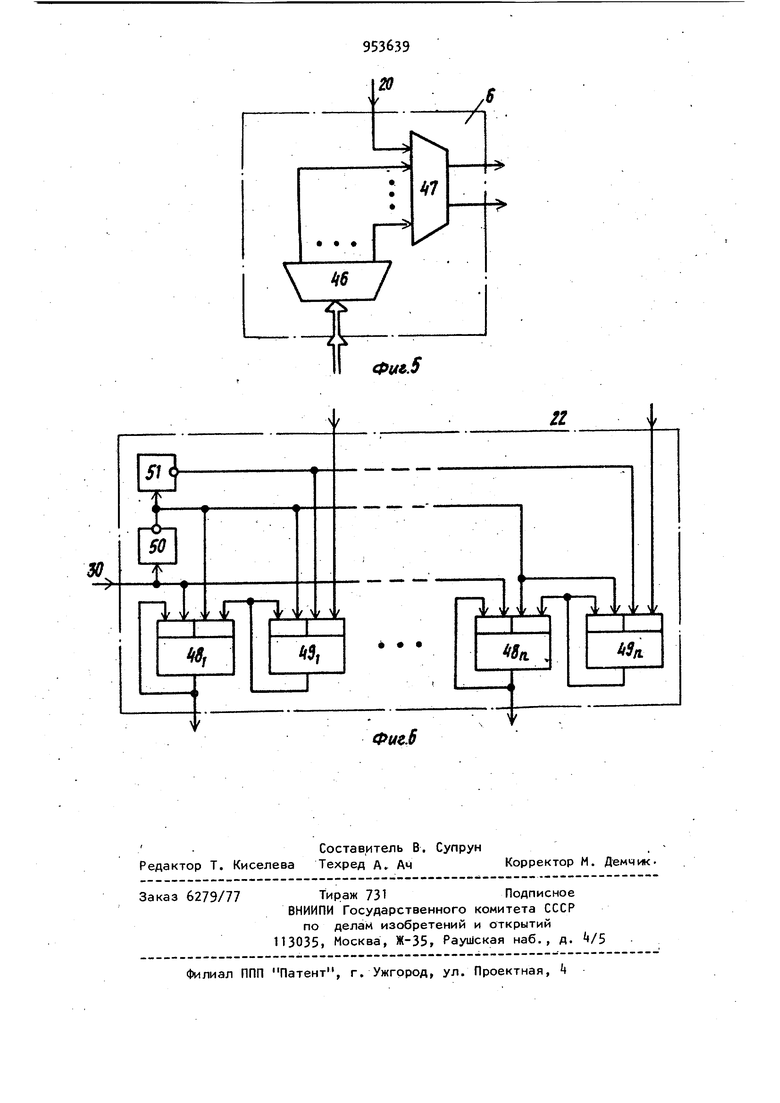

Дешифратор-шифратор 6 (фиг. 5) содержит дешифратор. 46 и шифратор ,. два выходакоторого соединены с выходами дешифратора-шифратора 6, адресный вход которого соединен с входом дешифратора «6, выходы которого соединены с входами шифратора 7, дополнительный вход которого соединен с дополнительным входом дешифраторашифратора 6. Дешифратор t6 распознает номер страницы памяти, с которой происходит обмен, а шифратор Ц производит настройку соответствующим образом коммутатора 2 памяти.

Регистр 22 неисправности памяти (фиг. 6) содержит п элементов И-ИЛИ 8, п элементов И-ИЛИ Ц и элементы НЕ 50 и 51 где п разрядность регистра 22 неисправности памяти. Выходы элементов И-ИЛИ соединены с первыми своими входами и образуют выходы регистра 22 неисправности памяти. Вторые входы элементов И-ИЛИ соединены между собой, с синхронизирующим входом регистра 22 неисправности памяти и с входом элемента НЕ 50, выход которого соединен с четвертыми входами элементов И-ИЛИ ,, с вторыми входами элементов И-ИЛИ kЭf(Э и с входом элемента НЕ 51, выход которого соединен с четвертыми входами элементов И-ИЛИ 49 -А9пВыходы элементов И-ИЛИ соединены с первыми своими входами и третьими входами одноименных эле1.3 -V ментов И-ИЛИ . Входы регистра 22 неисправнос.т-и памяти соединен с третьими входами элементов . И-ИЛИ 49 -49„. Перед описанием работы устройства вцелом опишем принцип работы регист ра 22 неисправности памяти (фиг.6). Запись информации в регистр 22 неисправности памяти производится по заднему фронту строба, поступающего с шины 30 на синхронизирующий вход регистра 22 неисправности памяти. При поступлении сигнала с шины 30 строба на вторые входы элементов И-ИЛИ ( (фиг. 6) на их выходах удерживается предшествующее состояние, так как наличие сигнала на вторых элементов И-ИЛИ замыкает обратную связь с их первых ходов на выходы. На выходе элемента НЕ 50 сигнал пропадает и тем самым снимается сигнал со вторых входов элементов И-ИЛИ 9;|- 9f,, что разрывает обратную связь с первых входов элементов И-ИЛИ (1 на их выходы. На выходе элемента НЕ 51 появляется сигнал, который поступает на четвертые входы элементов И-ИЛИ разрешая тем самым прохождению сигналов с входов регистра 22 неисправности памяти на выходы соответствующих элементов И-ИЛИ По окончании сигнала на шине 30 строба появляется сигнал на выходе элемента НЕ 50, а затем пропадает сигнал на выходе элемента НЕ 51. При этом на элементах И-ИЛИ Э, удерживается состояние их выходов на момент окончания сигнала на шине 30 строба, а на выходе элементов И-ИЛИ , (выходы регистра 22 не исправности памяти) подается состояние выходов элементов И-ИЛИ цТаким образом в регистре 22 неисправ ности памяти запоминается состояние его выходов в момент наступления зад него фронта сигнала на шине 30 стробов. Следовательно,элементы памяти регистра 22 неисправности памяти переключаются, аналогично JK-триггерам, по заднему фронту синхросигнала однако, не требует для правильного их срабатывания появления истинного сигнала на их информационных входах до поступления синхросигнала, как по казано ниже. С другой строны, затраты логических элементов оборудования на реализацию элементов памяти 39 регистра 22 неисправности памяти меньше, чем на реализацию ЗК-тригге.ров. Временная диаграмма работыЗК-триггера, где f - время переходных процессов в триггере: Синхронизирующий сигнал Входная информация Временная диаграмма работы триггеров, на.которых построен регистр 22 неисправности памяти: Синхронизирующий сигнал Входная информация Принцип работы предложенного устройствй заключается в том, что оно, кроме передачи сигналов между памятью и вычислительными блоками, обеспечивает фиксацию информации об отказах с выделением отказавших каналов и отказавших страниц памяти в этих каналах. При этом отказы классифицируются на два типа и фиксируются в соответствующих зонах регистра 22 неисправности памяти. В первую зону регистра 22 неисправности памяти записывается информация об отказе оборудования памяти, которое влияет на выдачу информац ии по всем разрядам памяти, а в третью зону регистра 22 неисправности памяти записывается информация от схем поразрядного сравнения. Таким образом, наличие информации о браке в первой и третьей зонах регистра 22 неисправности памяти говорит об отказе оборудова ЛГния памяти, влияющего на выдачу информации по всем разрядам, наличие информации о браке только в третьей зоне регистра 22 неисправности памяти гов.орит от отказе только в одномили в нескольких разрядах, а наличие информации о браке только в первой зоне регистра 22 неисправности памяти говорит от отказе типа обрьш по входам конца обмена с памятью. Кроме того, данный интерфейс памяти позволяет производить блокировку записи в регистр 22 неисправности 15 памяти информации о браке уже известном и зафиксированном в регистре 31 состояния (нуль в соответствующем разряде соответствующей зоны регистра 31состояния), чтобы исключить выработку сигнала прерывания от уже известных браков в памяти. Предлагаемое устройство также позволяет осуществить оперативное переключение с одного канала на другой при переходе от одной страницы памятИ, исправной только в одном канале к другой странице памяти, исправной только в одном (другом по отношению к предыдущей странице памяти) канале Этим самым обеспечивается перестройка на один исправный канал памяти при двух других отказавших. Мажоритарно-резервированный интерфейх; памяти работает следующим образом. Исходное состояние регистра 22 не исправности памяти перед началом работы нулевое, а регистра 31 состоя ния в блоке k реконфигурации - единичное, при этом на выходе прерывания каждого канала 1 сигнал отсутствует, сигналы отсутствуют и на управ ляющих выходах блока k реконфигурации. Сигналы с выходов регист ра 31 состояния поступают через ком мутаторы на выход мажоритарного элемента 35. При этом сигнал на выходе элемен та НЕ 39 отсутствует., что определяет отсутствие сигналов на управляющих выходах блока k реконфигу рации. На блокирующих выходах блока реконфигурации присутствуют сигналыукоторые по первым и вторым входам открывают элементы И 2k-2Э в индикаторах 3 брака. Отсутствие сигналов на входах бл ка 5 признака канала определяет отсутствие сигнала на первом ее выход 20 и соответственно на дополнительном входе дешифратора-шифратора 6, который при этом работает следующим образом. На адресный вход дешифрато ра-шифратора 6 поступает старшая часть адреса, в которой закодированы номера страниц памяти. Память в общем случае состоит из ОЗУ, ПЗУ, и памяти пульта управления, разбитых на страницы и составляющих полное поле памяти. Дешифратор 6 деши рирует номера страниц. Примем кодировку выходов шифратора 7, управ:ля1бщего коммутаторов 2 памяти для 9 . .пропуска соответствующей информации следующим образом: отсутствие сигналов соответствует обращению к ОЗУ, наличие сигнала на одном выходе соответствует обращению к ПЗУ; наличие сигнала на другом выходе соответствует обращению к памяти пульта, а наличие сигнала на двух выходах шифратора 7 соответствует настройке коммутатора 2 памяти на пропускание информации с дополнительного информационного входа. При такой кодировке выходов шифратора 47 дешифратор 46 не вырабатывает сигналов на выходах при обращении к ОЗУ, а выработка сигналов на- двух выходах шифратора 47 происходит только при наличии сигнала на дополнительном входе дешифратора-шифратора 6. На входах конца обмена канала 1 присутствуют сигналы, при этом при обращении к ОЗУготовность ОЗУ сигнализируется снятием сигнала по одним входам конца обмена канала 1, а при обращении к ПЗУ готовность ПЗУ сигнализируется снятием сигнала по другим входам конца обмена каналов 1. Если в каком-либо канале 1 сигнал конца обмена по соответствующему входу канала, 1 не снимется, это соответствует отказу устройства управления соответствующего вида памяти. Необходимость введения аналогичного сигнала для памяти пульта управления отсутствует по двум причинам, во-первых, пульт управления является технологической сервисной аппаратурой, К которой не предъявляются жесткие требования по надежности и, во-вторых, в пульт управления можно встроить средства контроля его оборудования, не затрагивая основное оборудование вычислительных средств. Таким .образом, при работе с памятью управляющие сигналы (обращение ЗУ, запись ОЗУ) с управляющих входов каналов Г через мажоритарные блоки 12 управления поступают на управляющие выходы каналов 1, коды адресов с адресных входов каналов 1, через мажоритарные блоки 11 адреса поступают на адресные выходы каналов 1, а информация, в случае записи в ОЗУ, с первых информационных входов каналов 1 через мажоритарные блоки 10 входной информации памяти подается на вторые информационные выходы каналов. При чтении информации из памяти данная информация через один из входов коммутатора 2 памяти поступает н входы мажоритарных блоков 9 выходной информации памяти и блоков 7 сравнения. С выхода мажоритарных блоков 9 вы ходной информации памяти информация поступает на первые информационные выходы каналов 1. В конце обращения к памяти на шине 30 строба вырабатывается сигнал, по которому во вторую зону регистра 22 неисправности памяти записывается старшая часть адреса (номер страницы в первую зону регистра 22 запишется единица в первый (второй; третий) разряд, если на соответствующем входе конца обмена первого (второго; третьего) канала 1 не снимется сигнал, а в третью зону регистра 22 запишется единица в тот разряд, который соответствует каналу 1, на выход коммутатора 2 памяти которого поступает информация отличная от информации в двух других каналах 1, и вызывающая выработку сигнала на выходе блока элементов ИЛИ 8 в соответствующих каналах 1. Так, например, при браке в информации перво го канала 1 на выходах (в соответствующих разрядах) блоков 7 сравнения первого и второго каналов 1 и на выходах блоков элементов ИЛИ 8 этих же каналов 1 выработаются сигна лы, при этом сработают толыЛ элемен ты И 27 во всех каналах 1 и. в регистров 22 всех каналов 1, соответствующий первому каналу 1, запишется едини ц. Наличие единицы хотя бы в одном из разрядов первой и третьей зон регистра 22, поступившей на вход элемента ИЛИ 23 обуславливает выработку сигнала на выходах прерывания каналов 1, при этом на кодовые выходы ка налов 1 выдается информация о канале имеющем брак (выходы первой и третьей зон регистра 22), и о бракованной странице памяти (выход второй зоны регистра 22). Сигналы о браке из первой зоны ре гистра 22 при наличии сигнала о браке со второй зоны регистра 22 свидетельствуют об опасных видах отказов, так как в этом случае информация искажается во всех разрядах в соответствующем канале 1. Наличие сигнала о браке в третьей зоне регистра 22, при отсутствии сигнала о браке в соответствующем канале 1 § первой зоне регистра 22, соответствует менее опасным типам отказов (например, отказ по какому-либо разряду) . Если же первая зона регистра 22 сигнализирует о браке, а третья зона регистра 22 находится в нулевом состоянии, то это указывает на отказ типа обрыБ по соответствующему входу |конца обмена (вход, по которому имеется обрыв определяется по коду в первой зоне регистра 22). Для того, чтобы.в дальнейшем, при обращении к странице, отказ которой раньше фиксировался, не вырабатывался сигнал на выходах прерывания каналов I, в соответствующий разряд соответствующей зоны регистра 31 со стояния в блоке реконфигурации за.писывается нуль. Тогда при обраще(нии к данной странице памяти коммутаторы 32-3 настраиваются на пропускание содержимого соответствующей зоны регистра 31 состояний, в одном из разрядов которого записан нуль. При этом на выходе мажоритарного элемента 35 по прежнему вырабатывается сигнал и на управляющих выходах блока 4 реконфигурации сигналы отсутствуют . На одном из блокирующих выходах 13-15 соответствующем каналу 1 с отказавшей страницей памяти, сигнал отсутствует, поэтому одна из пар элементов И 2 и 27, 25 и 28 или 26 и 29 будет закрыта по вторым входам и сигнал об отказе в соответствующем канале памяти не запишется в регистр 22 неисправности памяти. При отказах в других каналах этой же страницы памяти сигналы о браке будут записываться в регистр 22 неисправности памяти. Если второй отказ проявляется только в отдельных разрядах выходной информации памяти (наличие информации об отказе только в третьей зоне регистра 22 неисправности памяти), то существует вероятность того, что содержимое третьей зоны регистра 22 укажет на отказ в исправном, а не в неисправном канале 1 (этот случай возможен тогда, когда второй отказавимй канал памяти будет иметь отказы в тех же разрядах и того же характера - ложная единица или ложный нуль, - что и в первом отказавшем канале памятиJ. Поэтому для локали-, зации неисправного канала памяти в этом случае необходима проверка тестом.

При отказах в двух каналах какой-либо страницы памяти нормальная работа обеспечивается перестройкой на исправный канал в момент обращения к данной странице памяти. Для этого в соответствующую зону регистра 31 состояния записывается код с единицей в разряде, соответствующем исправному каналу памяти, и нулями в двух других .разрядах зоны. Тогда при обращении к данной странице памяти этот код подается на выходы коммутаторов 32-3 и на выходе мажоритарного элемента 35 сигнал будет отсутствовать, а элементы И 36-38 будут открыты по вторым входам и на выходе одного из них выработается сигнал.

Таким образом отсутствие сигнала на блокирующем выходе 16 блока k реконфигурации закроет элемент И в индикаторе 3 брака по первым вхдам, а на управляющем выходе 17 (18 или 19), соответствующем исправному каналу, вырабатывается сигнал.

Для примера рассмотрим случай, когда исправна страница памяти первого канала 1 (сигнал вырабатывается на управляющем выходе 17 блока t реконфигурации) . При этом блок 5 признака канала в первом канале 1 не вырабатывает сигналов ни на первом ни на втором .выходах 20 и 21, так как входной контакт 40 не подключен к выходным контактам 43 и kk, во вто ром канале 1 блок 5 признака канала выработает сигнал только на первом выходе 20, так как входной контакт 0 соединен с выходным контактом kk, соединенным только с входом элемента ИЛИ 45, а в третьем канале 1 блок 5 признака канала вырабатывает си|- нал и на первом и на втором выходах 20 и 21, так как входной контакт 0 соединен с выходным контактом 43, соединенным со вторым выходом 21 и с входом элемента ИЛИ 45. Поэтому во втором и в третьем каналах 1 сигнал с выхода 20 блока 5 признака канала поступает на шифратор 47 и обес печивается выработка сигналов на обоих выходах дешифратора-шифратора 6, которые в этих каналах настраивают коммутатор 2 памяти на пропускание информации с дополнительного информационного входа, а в первом канале коммутатор 2 памяти настраивается в соответствии с кодом на адресном входе дешифратора-шифратора 6. Таким образом, на выходах коммутаторов 2 памяти и на соответствующих входах мажоритарных блоков 9 выходной информации памяти будут присутствовать в первом канале 1 информация, принятая из исправной страницы памяти, во втором канале - нули (отсутствие сигнала на выходе 21 блока 5 признака канала), а в третьем канале - единицы (наличие сигнала на выходе 21 блока 5 признака канала).

В этом случае на выходы мажоритарных блоков 9 выходной информации и соответственно на первые информационные выходы всех каналов 1 поступает информация из памяти первого канала .

Следует отметить, что при отказах разных разрядов выходной информации памяти всех трех каналов работоспособность системы обеспечивается интерфейсом, включающим режим работы без перестройки памяти, а исключение выработки сигналов на выходе прерывания индикатора 3 брака обеспечивается посылкой в соответствующую зону регистра 31 состояния нулей во все разряды. При этом на управляющих выходах блока 4 реконфигурации при обращении к данной странице памяти сигналы отсутствуют (элементы И Зб-38 закрыты по первым входам), а элементы И 24-29 закрыты по первым и вторым входам.

Таким образом, предлагаемый мажоритарно-резервированный интерфейс памяти обеспечивает автоматическую перестройку на работу от одного канала для любой страницы памяти без дополнительных затрат времени на перестройку при переходе от одной страницы памяти к другой, не снижая быстродействие системы, при деградации памяти. Наличие брака сигнализируется записью кодов в первую и третью зоны регистра 22 неисправности памяти.

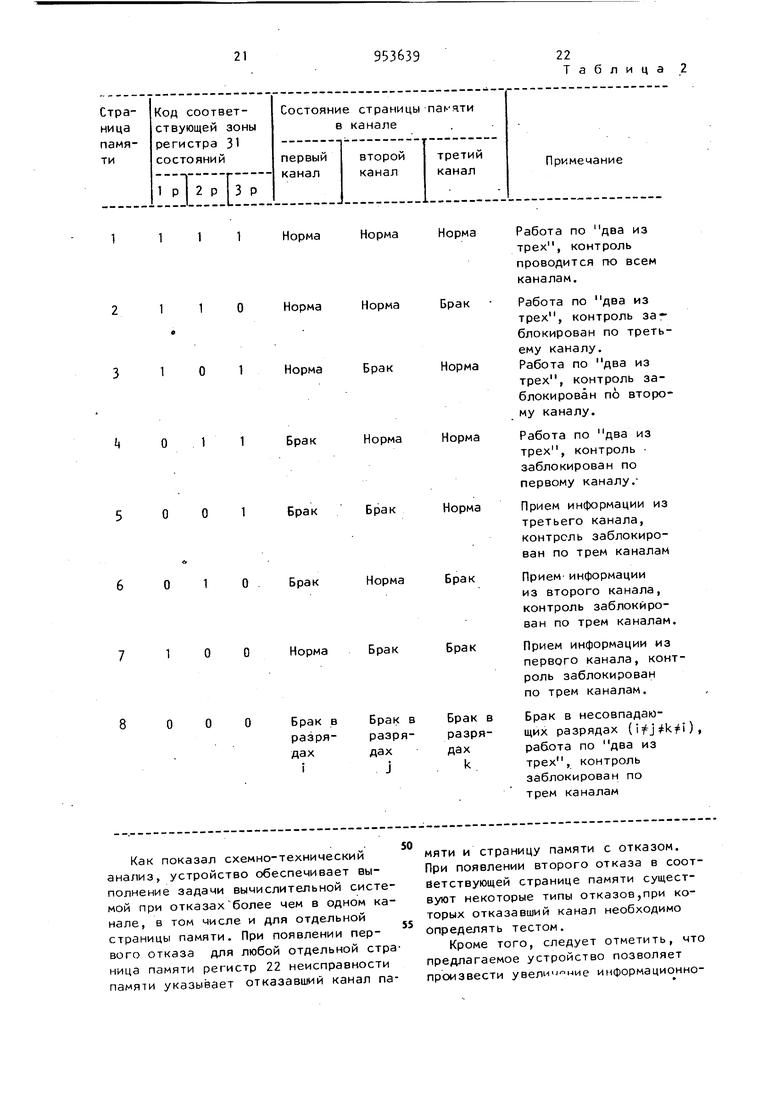

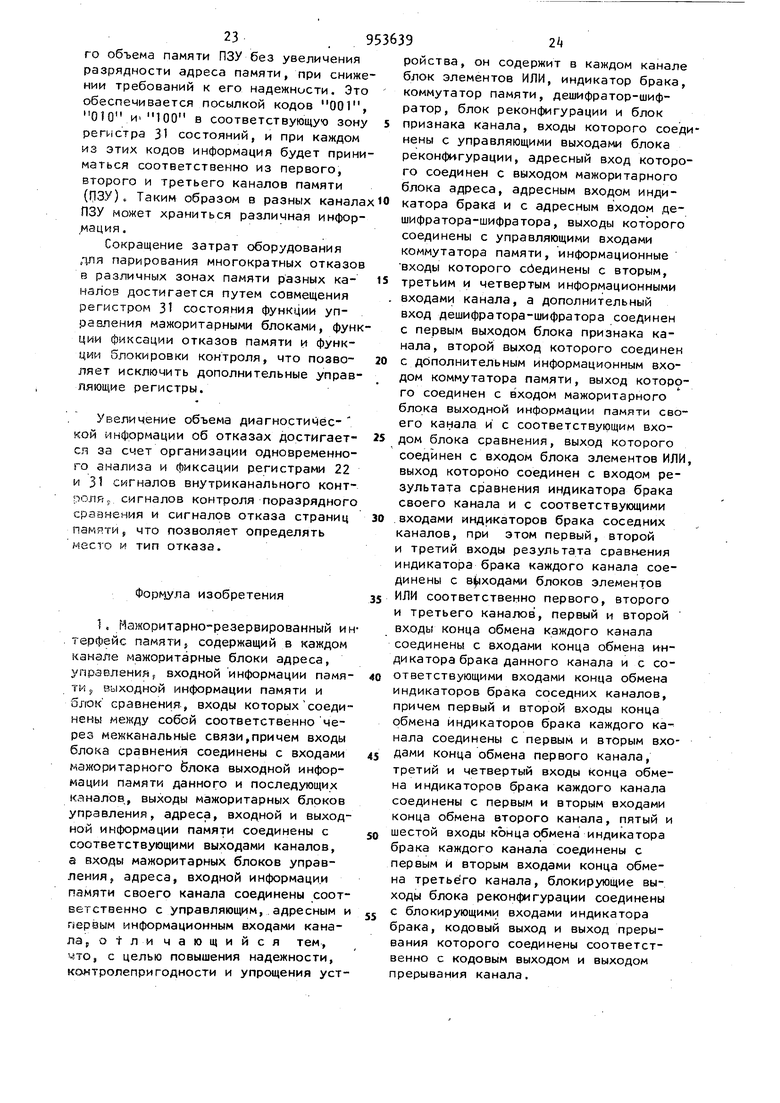

В табл. 2 приведен пример возможной ситуации, при которой обеспечивается работоспособность устройства с восемью страницами памяти. 1 111 Норма Норма Но 2 1 1 О Норма Норма Бр 31 01НормаБрак 4011Брак 5001Брак 601 ОБрак 7 100 Норма Брак 000 Брак в разрядах i Как показал схемно-технический анализ, устройство обеспечивает выполнение задачи вычислительной системой при отказах более чем в одном канале, в том числе и для отдельной страницы памяти. При появлении первого отказа для любой отдельной стра ница памяти регистр 22 неисправности памяти указывает отказавший канал паНорма Но Норма Бр Бр Брак в ра разрядадах j Работа по два из трех, контроль проводится по всем каналам. Работа по два из трех, контроль заблокирован по третьему каналу. Работа по два из трех, контроль заблокирован по второму каналу. Работа по два из трех, контроль заблокирован по первому каналу .Прием информации из третьего канала, контроль заблокирован по трем каналам Прием- информации из второго канала, контроль заблокирован по трем каналам. Прием информации из первого канала, контроль заблокирован по трем каналам. Брак в несовпадающих разрядах (), работа по два из трех, контроль заблокирован по трем каналам мяти и страницу памяти с отказом. При появлении второго отказа в соответствующей странице памяти существуют некоторые типы отказов,при которых отказавший канал необходимо определять тестом. Кроме того, следует отметить, что предлагаемое устройство позволяет произвести увелн мие информационного объема памяти ПЗУ без увеличения разрядности адреса памяти, при сниж нии требований к его надежности. Это обеспечивается посылкой кодов 001 010 в соответствующую зону регистра 31 состояний, и при каждом из этих кодов информация будет прини маться соответственно из первого, второго и третьего каналов памяти (ПЗУ). Таким образом в разных канала ПЗУ может храниться различная информация. Сокращение затрат оборудования .тля парирования многократных отказов в различных зонах памяти разных каналов достигается путем совмещения регистром 31 состояния фунК|4ии упраапения мажоритарными блоками, функ ции фиксации отказов памяти и функции блокировки контроля, что позволяет исключить дополнительные управляющие регистры. Увеличение объема диагностичёской информации об отказах достигается за счет организации одновременного анализа и фиксации регистрами 22 и 31 сигналов внутриканального контроля; сигналов контроля поразрядного сравнения и сигналов отказа страниц памяти что позволяет определять место и тип отказа. изобретения 1. Мажоритарно-резервированный ин терфейс памяти 5 содержащий в каждом канале мажоритарные блоки адреса, управленияf входной информации памятм,, выходной информации памяти и блок сравнения, входы которыхсоединены между собой соответственно через межканальнУе связи,причем входы блока сравнения соединены с входами мажоритарного блока выходной информации памяти данного и последующих каналов, выходы мажоритарных блоков управления, адреса, входной и выходной информации памяти соединены с соответствующими выходами каналов, а входы мажоритарных блоков управления, адреса, входной информации памяти своего канала соединены соответственно с управляющим, адресным и первым информационным входами канала otли чающийся тем, что, с целью повышения надежности, контролепригодности и упрощения устройства, он содержит в каждом канале блок элементов ИЛИ, индикатор брака, коммутатор памяти, дешифратор-шифратор, блок реконфигурации и блок признака канала, входы которого соединены с управляющими выходами блока реконфигурации, адресный вход которого соединен с выходом мажоритарного блока адреса, адресным входом индикатора браки и с адресным входом дешифратора-шифратора, выходы которого соединены с управляющими входами коммутатора памяти, информационные входы которого соединены с вторым, третьим и четвертым информационными входами канала, а дополнительный вход дешифратора-шифратора соединен с первым выходом блока признака канала, второй выход которого соединен с дополнительным информационным входом коммутатора памяти, выход которого соединен с входом мажоритарного блока выходной информации памяти своего канала и с соответствующим входом блока сравнения, выход которого соединен с входом блока элементов ИЛИ, выход котороно соединен с входом результата сравнения индикатора брака своего канала и с соответствующими входами индикаторов брака соседних каналов, при этом первый, второй и третий входы результата сравнения индикатора брака каждого канала соединены с выходами блоков элементов ИЛИ соответственно первого, второго и третьего каналов, первый и второй входы конца обмена каждого канала соединены с входами конца обмена индикатора брака данного канала и с соответствующими входами конца обмена индикаторов брака соседних каналов, причем первый и второй входы конца обмена индикаторов брака каждого канала соединены с первым и вторым входами конца обмена первого канала, третий и четвертый входы конца обмена индикаторов брака каждого канала соединены с первым и вторым входами конца обмена второго канала, пятый и шестой входы конца обмена индикатора брака каждого канала соединены с первым И вторым входами конца обмена третьего канала, блокирующие выходы блока реконфигурации соединены с блокирующими входами индикатора брака, кодовый выход и выход прерывания которого соединены соответственно с кодовым выходом и выходом прерывания канала.

0 с управляющими выходами блока реконфигурации, .адресный вход которого соединен с управляющими входами коммутаторов, причем выходы первых разрядов всех зон регистра состояния

5 соединены с входами первого коммута. тора, выходы вторых разрядов всех зон регистра состояния соединены с входами второго коммутатора, а выходы третьих разрядов всех зон регистра

0 состояния соединены с входами третьего коммутатора, выходы коммутаторов соединены с входами мажоритарного элемента и с первыми входами элементов И, вторые входы которых соединены между собой и с выходом элемента НЕ, вход которого соединен с выходом мажоритарного элемента, выходы коммутаторов и мажоритарного элемента соединены с блокирующими выходами блока реконфигурации.

Источники информации, принятые во внимание при экспертизе

кл. G Об F 11/20, опублик. 1973 (прототип) .

ejjj; С« « eVrJjaSXS

-ff С J

«k

.

«k-

Ч

« S

«ГчУ.

u«

kC

tN|

&

/ IfiV

Фи9.3

Фиг.6

Авторы

Даты

1982-08-23—Публикация

1980-09-22—Подача