1

Изобретение относится к вычислительной технике и предназначено для сложения чисел, представленных в коде М из N.

Известен сумматор, работающий в пятерично-двоичном коде, содержащий первую и вторую группы взсодов для подачи первой и второй грулп параллельных сигналов, представляющих десятичные цифры, в соответствии с нормальной числовой формой записи. Преобразующее устройство состоит из большого числа элементов И, ИЛИ и осуществляет преобразование сигналов с первой и второй групп входов из двоично-десятичной, системы в пятеричнолвричную. Матрица сумматора, содержащая емкостные элементы для селективной связи выходов элементов И и ИЛИ, предназначена для получения сигналов суммы 1.

Недостатком данного устройства является большое количество оборудования.

Наиболее близким по технической сущности к предлагаемому является десятичный двухразрядный сумматор в коде 2 из 5 , содержащий мес ного управления, преобразователи кодов операндов младшего и старшего

разрядов, матрицы сложения младшего и старшего разрядов , блок коррекции млсщшего и старшего разрядов, блоки переноса младшего и старшего разрядов соответственно, шифратор младшего разряда, блоки выдачи старшего разряда суммы 2.

Недостатком .такого сумматора является малое быстродействие.

0

Цель изобретения - повышение быстродействия двухразрядного сумматора.

Поставленная цель достигается тем, что в двухразрядный сумматор, содержащий две матрицы сложения младших

5 и старших разрядов, блоки переносов младших и старших разрядов, входы которых подключены к первым группам выходов соответственно матрицы сложения младших разрядов и мат0рицы сложения старших разрядов, шифратор младших разрядов суммы и блок выдачи старших разрядов суммы, первые входы которых подключены к выходам блока переноса младших разрядов,

5 а выходы являются первой группой выходов устройства, введены блок выдачи младших разрядов суммы, первая группа входов которого подключены к группе выходов шифратора младших

0 разрядов суммы, входы которого подключены к второй группе выходов матрицы сложения млали.1их разрядов, шифраторы старших разрядов, группы входов которых подключены к группе выходов матрицы сложения старших разрясов, а выходы соединены с вторыми группами входов соответствующих блоков выдачи старших разрядов суммы, блоки контроля старших и младших разрядов, причем две группы входов блока контроля младших разрядов являются первой и второй группами входов устройства, а первый и второй выходы подключены соответственно к второму и третьему входам блока выдачи младшего разряда суммы, выходы которого являются второй группой выходов устройства, первая и вторая группы входов блока контроля старших разрядов являются соответственно третьей и четвертой группами входов устройства, а первый и второй выходы подключены соответственно к третьим и четвертым входам блоков выдачи старших разрядов суммы, первые и вторые группы входов матрицы сложения младших разрядов являются соответственно пятой и шестой группами входов устройсва, а первая и вторая группы входов матриизы сложения старших разрядов являются соответственно седьмой и восьмой группами входов устройства, первый и второй выходы блока переноса старших разрядов являются соответственно третьим и-четвертым выходами устройства.

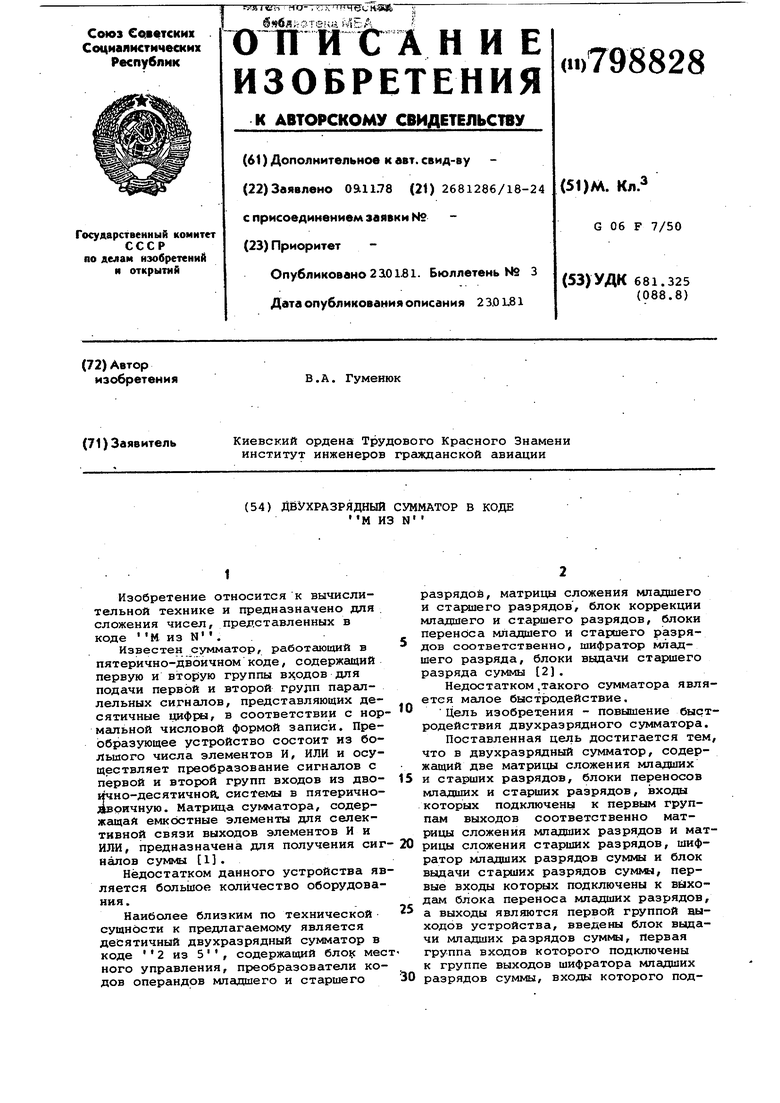

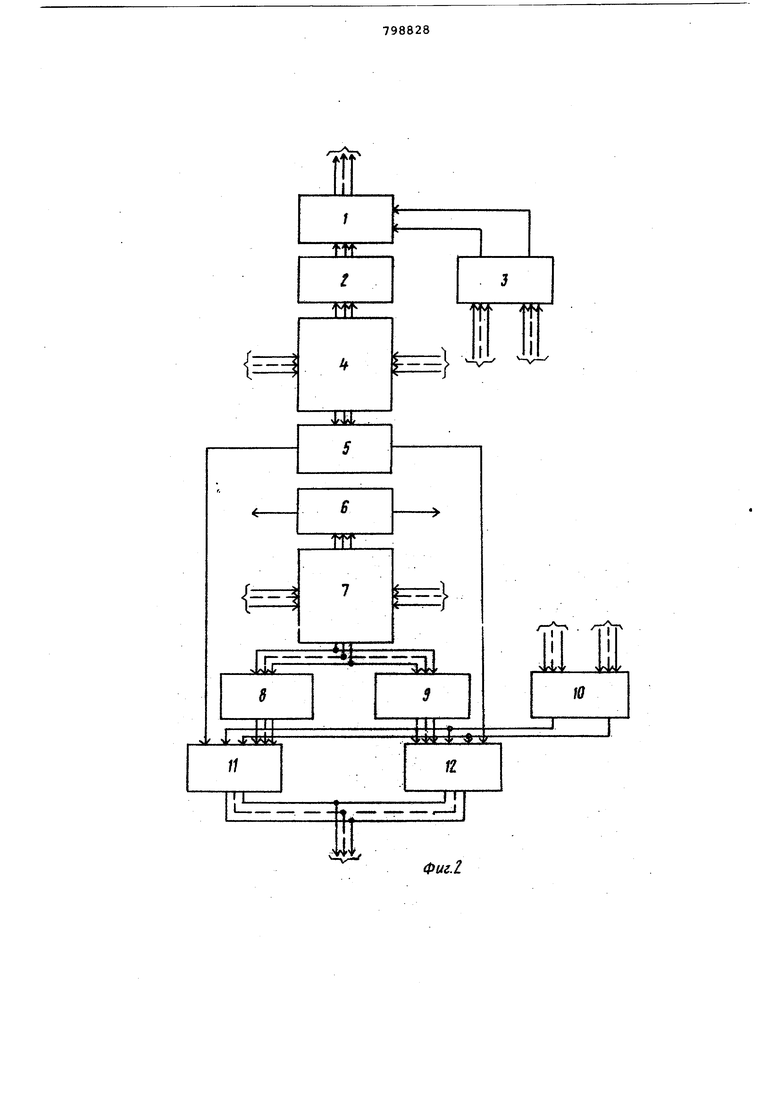

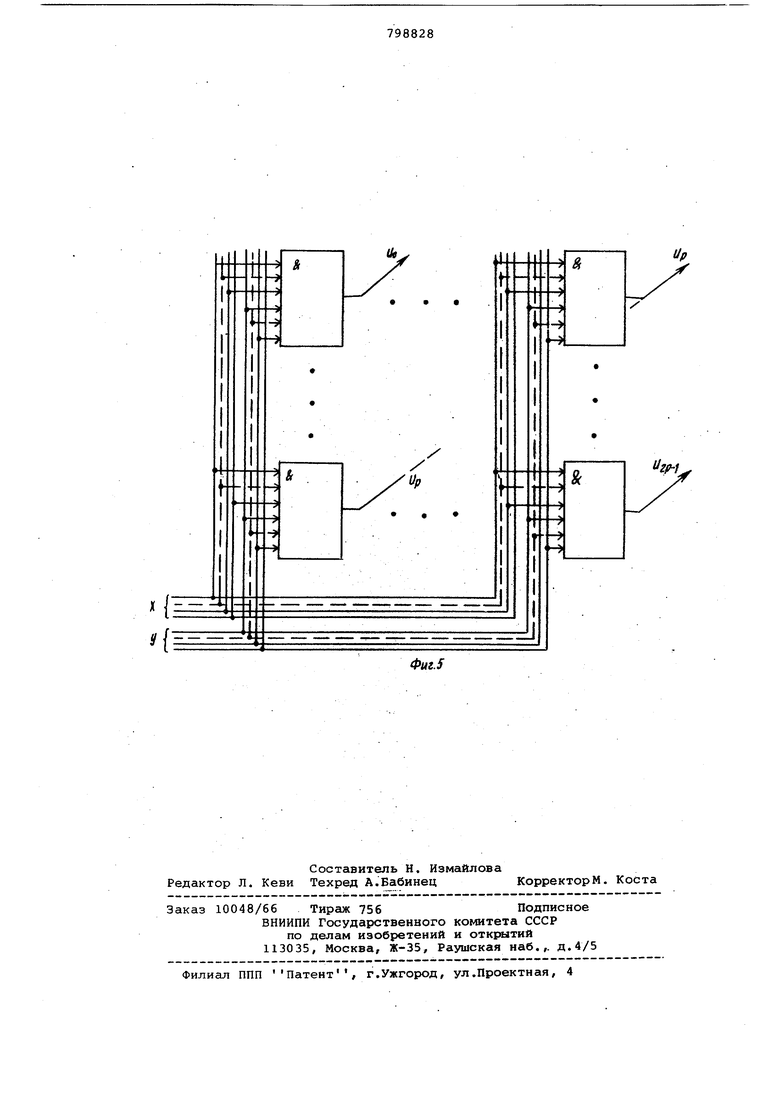

На фиг.1 представлена блок-схема предлагаемого двухразрядного сумматора в коде М из N; на фиг.2 схема блока выдачи младшего разряда cyivD-ttj; на фиг.З - схема шифратора; на фиг.4 - схема матрицы сложения; на фиг.З - схема блока выдачи старшего разряда суммы.

Сумматор содержит блок 1 выдачи младшего разряда суммы, шифратор 2 младшего разряда, блок 3 контроля йпадаиего разряда, матрицу 4 сложения мпадииего разряда, блок 5 переноса младшего разряда, блок б переноса старшего разряда, матрицу 7 сложения старшего разряда, шифратор 8 и 9 старшего разряда, блок 10 контроля старшего разряда, блоки Ни 12 выдачу старшего разряда суммы.

Блок 1 выдачи млс1дшего разряда суммы представляет собой группу из N трехвходовых элементов И (фиг.2), где N - количество позиций кодового слова. Входы каждого элемента И соединены с соответствующим входом блока 1. Выходы элементов И являются выходами блока 1.

Шифраторы 2, 8 и 9 представляют собой группы из N многовходовых элементов ИЛИ (фиг.З). Входы элементов или соединены с определенными входами шифраторов 8 и 9, согласно выбранному алфавиту. Причем, результат сложения в шифраторах 2 и 8 шифруется в коде М из N, а в шифраторе 9 в коде М из N с добавлением единицы . Количество входов элементов ИЛИ определяется по формулам

..МР М(р-1)

If

N {Г

где 1 и 12 - количества входов элементов ИЛИ шифраторов 2,8 и 9 соответственно; М - количество единиц

в кодовом слове Р - основание системы счисления.

Выходы элементов ИЛИ являются выходами соответствующих шифраторов

5 2,8 и 9.

Матрицы 4 и 7 представляют собой матрицы многовходовых элементов И (фиг.2). Количество входов элемента И равно 2М. Входы элементов И матриц

0 5 и 7 соединены с определенными шинами кодов операндов, согласно выбранному алфавиту. Шины кодов операндов соединены с входами матриц 4 и 7. Диагональные шины, объединяющие выf ходы элементов И, соответствующих одинаковым результатам (учитывая перенос) сложения, соединены с группами матриц 4 и 7.

Блоки 5 и б переноса представляют собой группы из двух элементов ИЛИ.

0 р входов одних элементов ИЛИ соединены с i-ми входами блоков, где . Эти элементы соответствуют переносам О в старшие разряды. Р-1 входов других элементов ИЛИ

5 соединены с j-ми входами блоков,

где Р i j Р-2. Эти элементы соответствуют переносам в старшие разряды. Выходы элементов ИЛИ соединены с выходами соответствующих

Q блоков 5 и 6.

Блоки 3 и 10 контроля представляют собой схемы контроля для кода М из N (полные дешифраторы или пороговые схемы), на входы которых подаются кодовые слова, противоположные операндам.

Блоки 11 и 12 выдачи представляют собой группы из N четырехвходовых элементов И (фиг.5). Входы каждого элемента И соединены с одним из входов блока, соединенных с шифраторами 8 или 9, а также - с входами блока, соединенными с блоками 5 и 10 переноса. Выходы элементов И являются выходами блоков 11 и 12.

5 Устройство работает следующим образ ом.

Операнды в коде М из N поступают на матрицы 4 и 7 сложения, соответственно разрядам. Одновременно сигналы, противоположные кодам операндов, поступают на блоки контроля 3 и 10, соответственно разрядам. Появление нескомпенсированной ошибки приводит или к появлению сигналов на

выходах сразу нескольких элементов И матрицы (матриц 4 и 7 сложения), или к отсутствию сигналов на их выходах. В первом случае отсутствует разрешающий сигнал на выходе соответствующей схемы контроля. В обоих случаях на выходах разряда (разрядов) сумматора сигналы результата отсутствуют. Если в кодовых словах операндов длиной N будет точно М единиц , с выходов матриц 4 и 7 сложения сигналы поступают в соответствующие шифраторы 2, 8 и 9 и блоки 5 и 6 переносов. С блока б переноса сигнал поступает в выходную шину устройства, а с блока 5 переноса - на один из блоков 11 или 12 выдачи старшего разряда суммы. С выходов шифратора 2 сигнсшы поступают на входы блока 1 выдачи младшего разряда суммы, с выходов шифраторов 8 и 9 сигналы поступают на входы блоков 11 и 12 выдачи старшего разряда суммы соотве т-ственно. Причем, шифраторы 2 и 8 зашифровывают результат сложения в коде М из N, а шифратор 9 - в коде М из N с добавлением единицы . Одновременно на блок 1 поступают разрешающие сигналы с блока 3, а на блоки. 11 и 12 - с блока 10. При наличии всех разрешающих сигналов на входах блоки 1 выдачи младшего разряда суммы и одном из блоков 11 или 12 выдачи старшего разрядасуммы, сигналы с этих блоков поступают в выходные шины устройства.

Положительный эффект от внедрения предлагаемого устройства заключается в повьаиении быстродействия не менее, чем на 25%, так как в предлагаемом устройстве сигналы до сформирования результата сложения проходят через три блока, а в известном устройстве - через четыре блока.

Формула изобретения

Двухразрядный сумматор в коде М из N, содержащий две матрицы сложения младших и старших разрядов, блрки переносов младших и старших разрядов , входы которых подключены к первым группам выходов соответственно матрицы сложения младших разрядов

и матрицы сложения старших разрядов, шифратор младших разрядов суммы и блок выдачи стариих разрядов суммы, первые входы которых подключены к выходам блока переноса младших разрядов , а выходы являются первой группой выходов устройства, отличающийся тем, что, с целью повышения быстродействия, в устройство введены блок выдачи младших разрядов суммы, первая группа входов которого

0 подключены к группе выходов шифратора младших разрядов суммы, входы которого подключены к второй группе выходов матрицы сложения младших разрядов , шифраторы старших разрядов,

5 гРУПпы входов которых подключены к группе выходов матрицы сложения старших разрядов, а выходы соединены с вторыми группами входов соответствующих блоков выдачи старших разрядов

Q суммы, блоки контроля старших и младших разрядов, причем две группы входов блока контроля младших разрядов являются первой и второй группами входов устройства, а первый и второй выходы подключены соответственно к

5 второму и третьему входам блока выдачи младшего разряда суммы, выходы которого являются второй группой выходов устройства, первая и вторая группы входов блока контроля старших

0 разрядов являются соответственно третьей и четвертой группами входов устройства, а первый и второй выходы подключены соответственно к третьим и четвертым входам блоков выдачи

5 старших разрядов суммы, первые и вторые группы входов матрицы сложения младших разрядов являются соответственно пятой и шестой группами входов устройства, а первая и вторая

n входов матрицы сложения старших разрядов являются соответственно седьмой и восьмой группами входов устройства, первый и второй выходы блока переноса: старших разрядов являются соответственно третьим и четвертым выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Патент США 3308284, кл. 235-174, 1971.

0 2. Авторское свидетельство СССР № 259480,кл. G 06 F 7/50, 25.04.68 (прототип).

oii

i t

«as

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухразрядный сумматор в коде "М из N | 1981 |

|

SU980092A1 |

| Сумматор в коде "М из N | 1981 |

|

SU985781A1 |

| Сумматор в коде "м из N | 1979 |

|

SU873238A1 |

| Сумматор в коде "М из N | 1981 |

|

SU981992A1 |

| Сумматор в коде М из N | 1980 |

|

SU955037A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| Сумматор в коде "М" из "N | 1981 |

|

SU983706A1 |

| Матричное устройство для возведения в квадрат | 1988 |

|

SU1608653A1 |

| ДЕСЯТИЧНЫЙ ДВУХРАЗРЯДНЫЙ СУММАТОР В КОДЕ «2 из 5^ | 1970 |

|

SU259480A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2003 |

|

RU2251144C1 |

I

5

V k i

Авторы

Даты

1981-01-23—Публикация

1978-11-09—Подача