информационные выходы которого соединены соответственно с четвертыми входами регистров адреса неисправной ячейки второй группы, кроме первого, и счетным входом счетчика выход каждого регистра адреса неисправной ячейки второй группы подключен к пятому входу последующего регистра,адреса неисправной ячейки второй группы, соответствующему входу блока индикации, второму входу одноименного регистра адреса неисправной ячейки первой группы и одному из информационных входов блока сортировки, другой информационный вход которого соединен с выходом первого элемента И, третьи входы регистров адреса неисправной ячейки первой группы объединены и являются управляющим входом блока памяти, адресные, инфомационные и управляющие входы блоко памяти соответственно объединены и являются входами устройства, управляющими выходами которого являются выходы счетчиков.

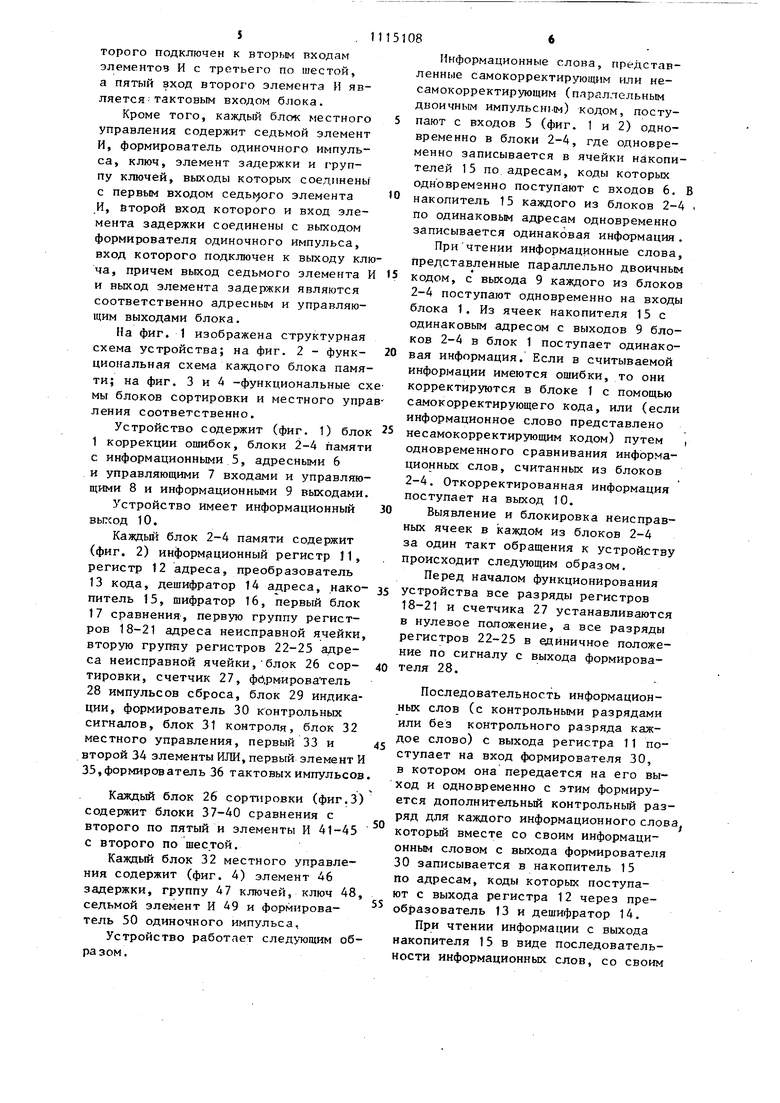

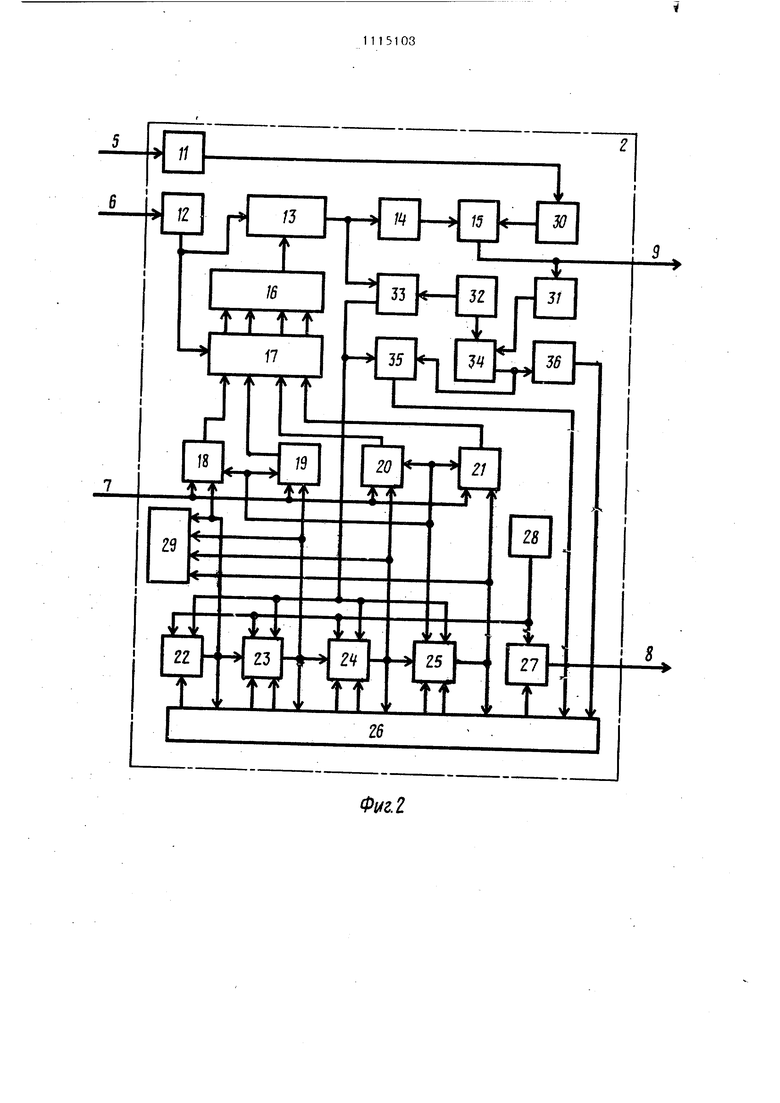

2, Устройство по п. 1, отличающее ся тем, что каждый блок сортировки содержит элементы И с второго по шестой и блоки сравнения с второго по пятый, первые входы которых являются информационными входами блока с пер вого по четвертый, вторые входы пятым информационным входом блока, а первые вьосоды являются информационными выходами блока и подключены к первым входам элементов И с третьего по шестой, выходы которых являются тактовыми выходами блока, причем вторые выходы блоков сравнения с второго по пятый соединены с входами с первого по четвертый второго элемента И, выход которого подключен к вторым входам элементов И с третьего по шестой, а пятый вход второго элемента И является тактовым входом блока.

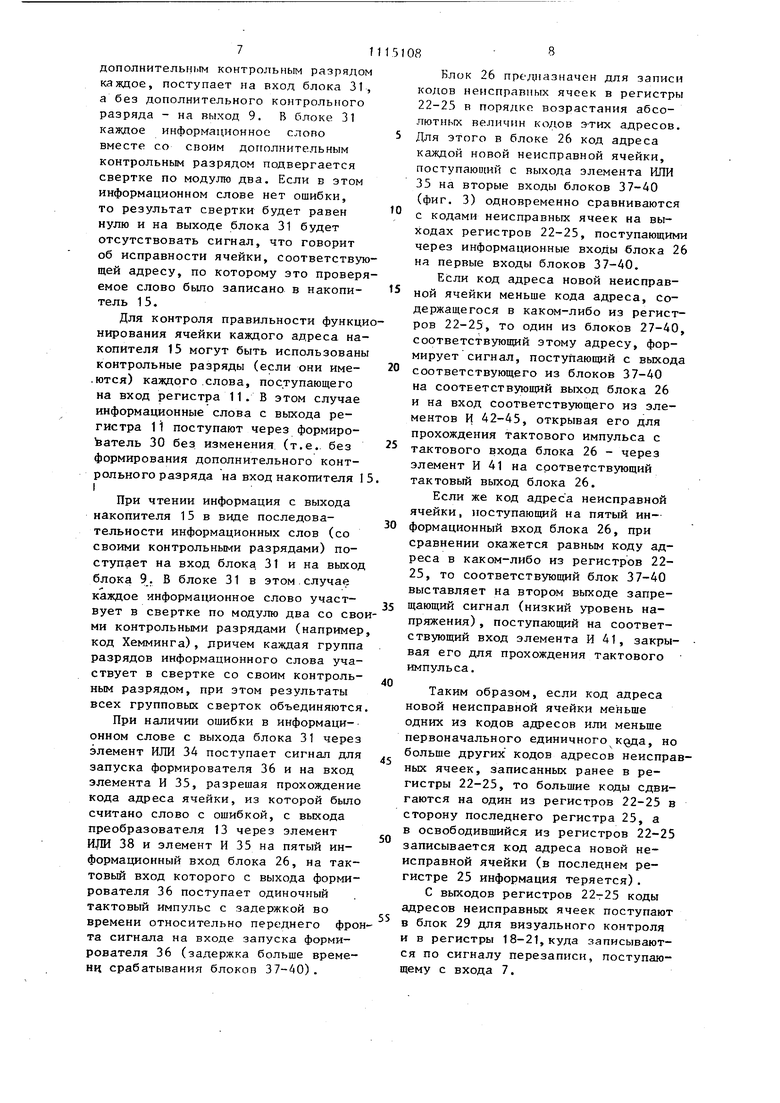

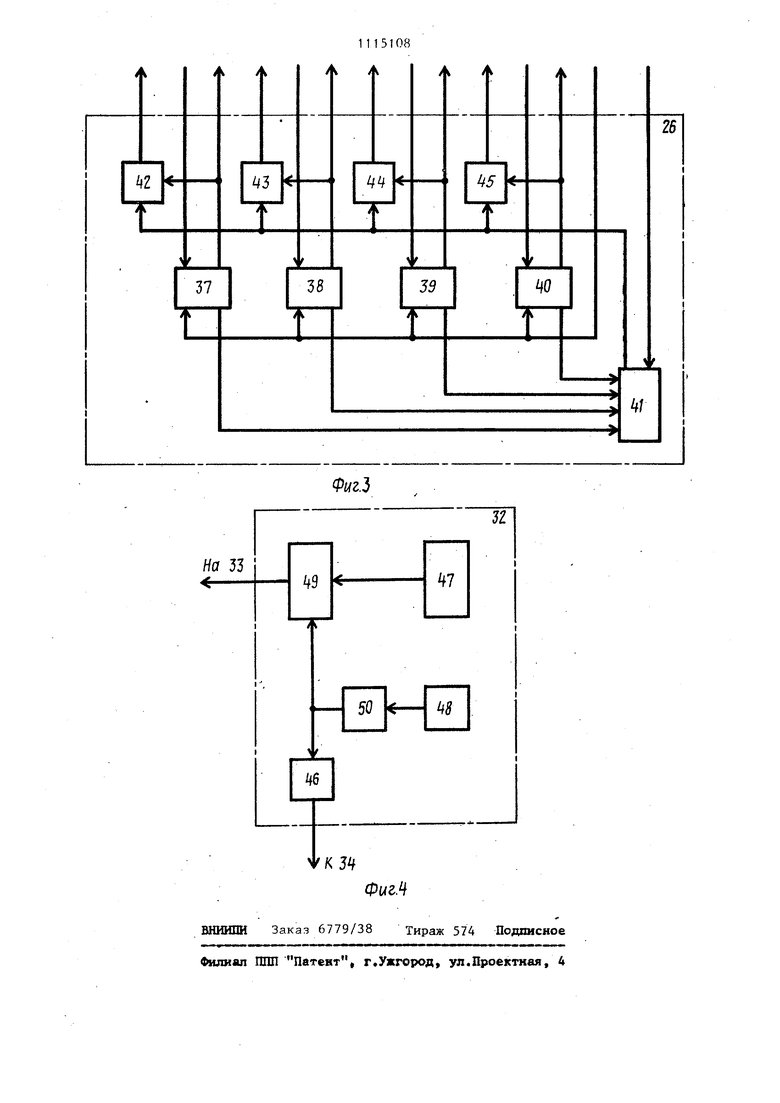

3. Устройство по пп. 1 и 2, отличающееся тем, что каждый блок местного управления содержит седьмой элемент И, формирователь одиночного импульса, ключ, элемент задержки и группу ключей, выходы которых соединены с первым входом седьмого элемента И, второй вход которого и вход элемента задерки соединен с выходом формирователя одиночного импульса, вход которого подключен к вькоду ключа, причем выход седьмого элемента И и выход элемента задержки являются соответственно адресным и управляющим выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1305772A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Устройство для контроля блоков полупроводниковой памяти | 1979 |

|

SU875469A2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1108511A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1981 |

|

SU972599A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

| Буферное запоминающее устройство с самоконтролем | 1982 |

|

SU1019492A1 |

1. ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С БЛОКИРОВКОЙ НЕИСПРАВНЫХ ЯЧЕЕК, содержащее блок коррекции ошибок, выход которого является информационным входом устройства, и блоки памяти, каяздый из которых содержит накопитель, дешифратор адреса, преобразователь кода и информационный регистр, входы которого являются информационными входами блока памяти, причем выходы преобразователя кода соединены с входами дешифратора адреса, выходы которого подключены к адресным входам накопителя, выходы которого соединены с соответствующими входами блока коррекции ошибок отличающееся тем, что, с целью повышения быстродействия устройства, в каждый блок памяти введены шифратор, первый блок сравнения, группы регистров адреса неисправной ячейки, блок сортировки, формирователь импульсов сброса, блок индикации, формирователь контрольных сигналов, блок контроля, блок местного управления, элементы ИЛИ, формирователь тактовых импульсов, первый элемент И, счетчик и регистр адреса, входы которого являются адресными входами блока памяти, причем выходы информационного регист1 а соединены с входами формирователя контрольных сигналов, выходы которого подключены к информационным входам накопителя, выходы которого соединены с входами блока контроля, выходы регистра адреса подключены к одним из входов преобразователя кода и одним из входов первого блока сравнения, выходы которого соединены с входами шифратора, выходы которого подключены к другим входам преобразователя кода, вьрсоды которого соединены с первым входом первого элемента ИЛИ, другие входы первого блока сравнения подключены к (Л выходам регистров адреса неисправной ячейки первой группы, первые входы которых и первые входы регист- S с ров адреса неисправной ячейки второй группы соединены с выходом формирователя импульсов сброса и входом сброса счетчика, выход блока контроля подключен к первому входу второго элемента ИЛИ, выход которого соединен :п с первьм входом первого элемента И и входом формирователя тактовых импульо сов, выход которого подключен к так00 товому входу блока сортировки, вторые входы первого и второго элементов ИЛИ подключены соответственно к адресному и управляющему выходам блока местного управления, выход первого элемента ИЛИ соединен с вторым входом первого элемента И и вторыми входами регистров адреса неисправной ячейки второй группы, третьи входы которых подключены к тактовым выходам блока сортировки.

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Известны запоминающие устройства с блокировкой неисправных ячеек СП и .

Одно из известных устройство содержит накопитель, состоящий из основных и дополнительных элементов памяти, регистры адреса, и счетчик СП.

Недостатком этого устройства является низкое быстродействие.

Наиболее б;1изким техническим решением к предлагаемому является запоминающее устройство с блокировкой неисправных ячеек, содержащее неCKOinbKo одинаковых накопителей, подключенньвс к соответствующим входам

блока коррекции ошибок и соединенных своими адресными входами через соответствующий дешифратор адреса с выходом соответствующего преобразователя кода адреса, один из входов которого соединен с соответствующим регистром числа, а другой вход - с кодовыми шинами адреса С2Д, . Недостатками этого устройства

являются невозможность устранения нескольких дефектов за один такт обращения к нему, поскольку для корректировки нескольких дефектов наqo подбирать другие корректирующие

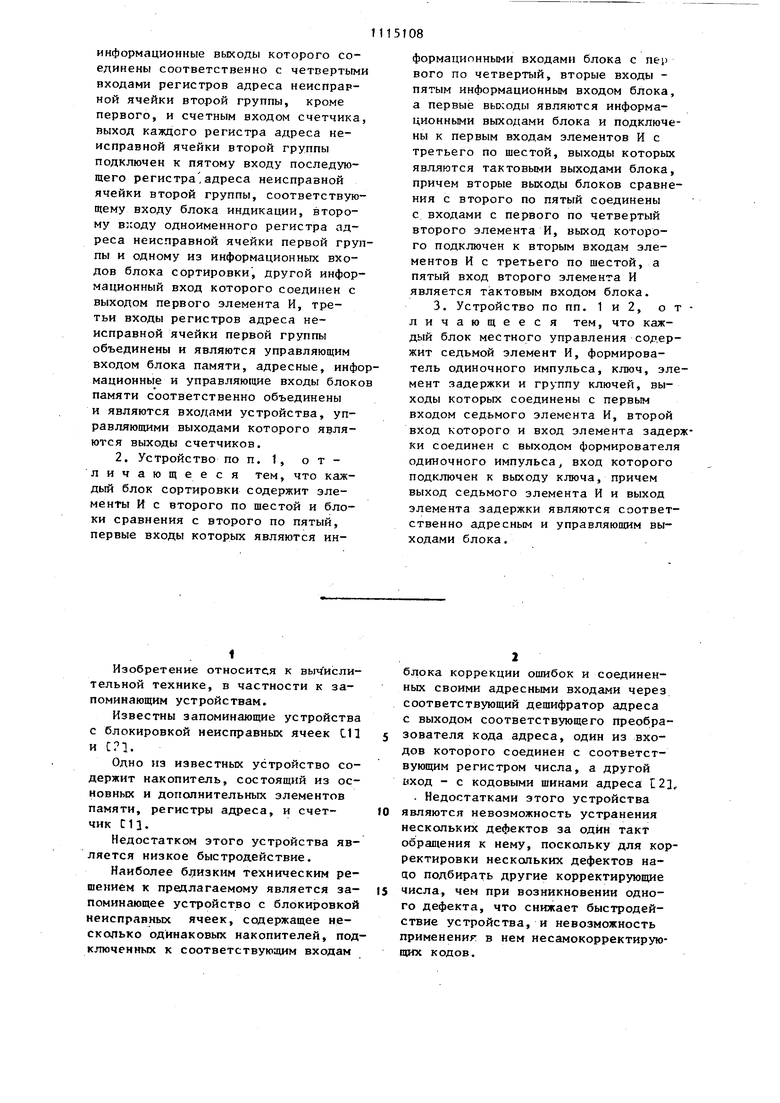

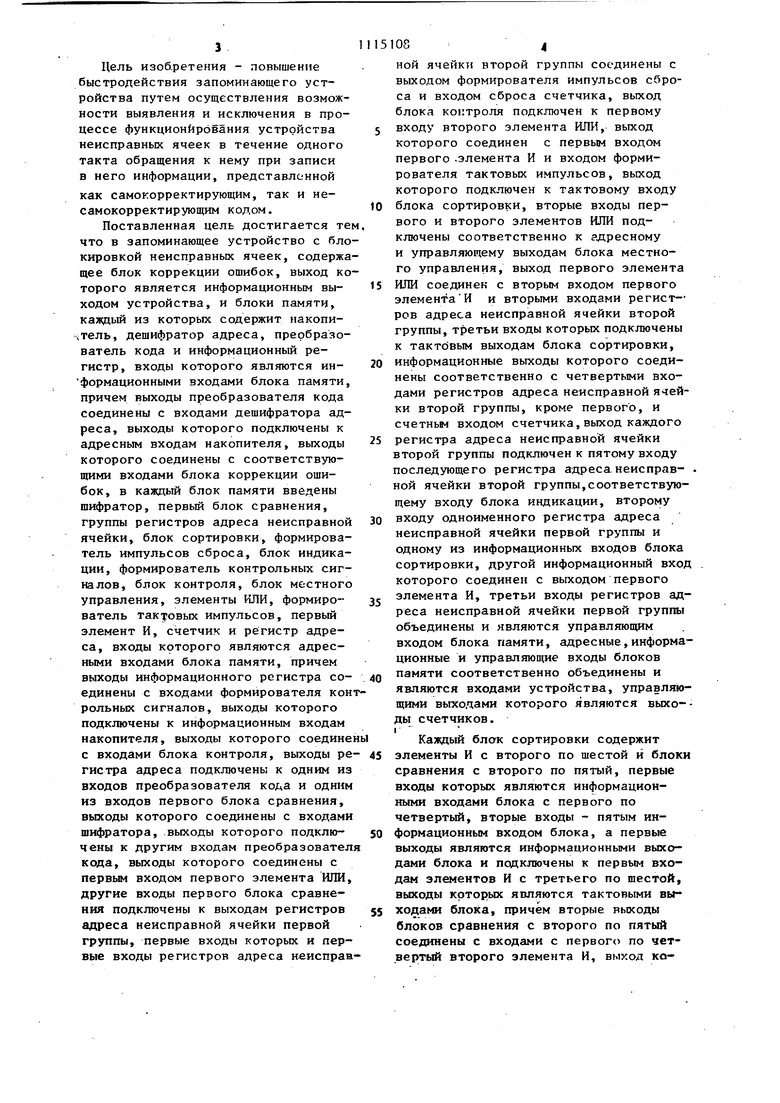

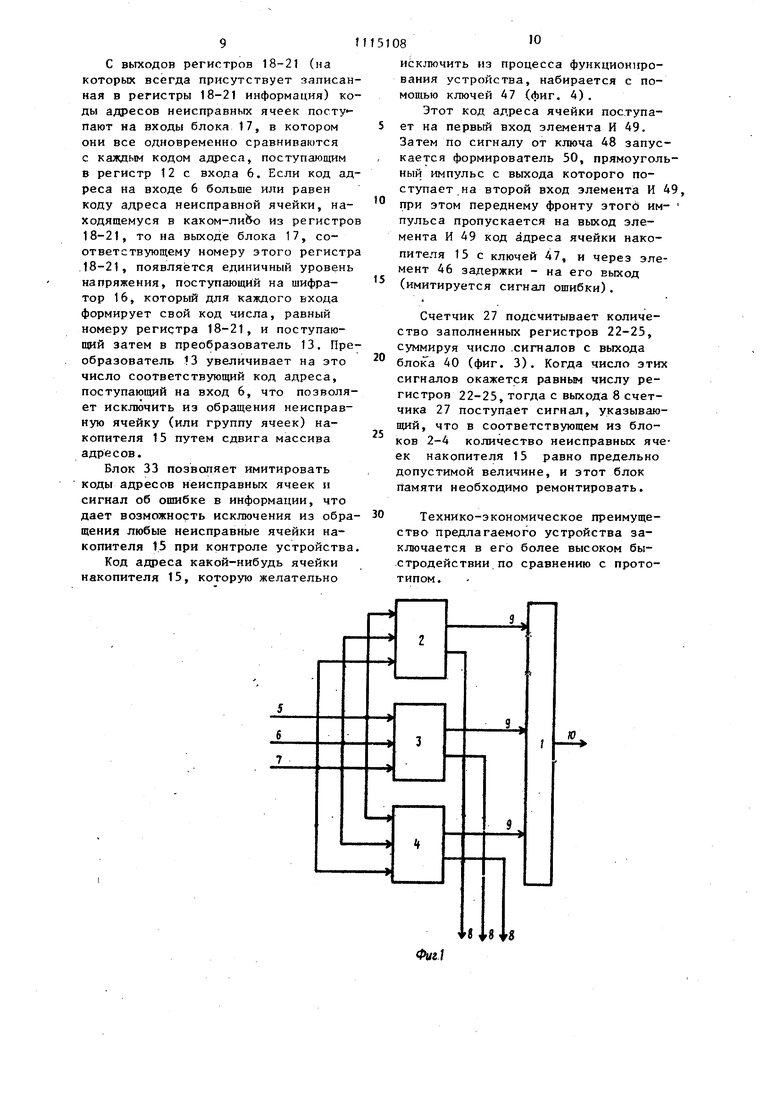

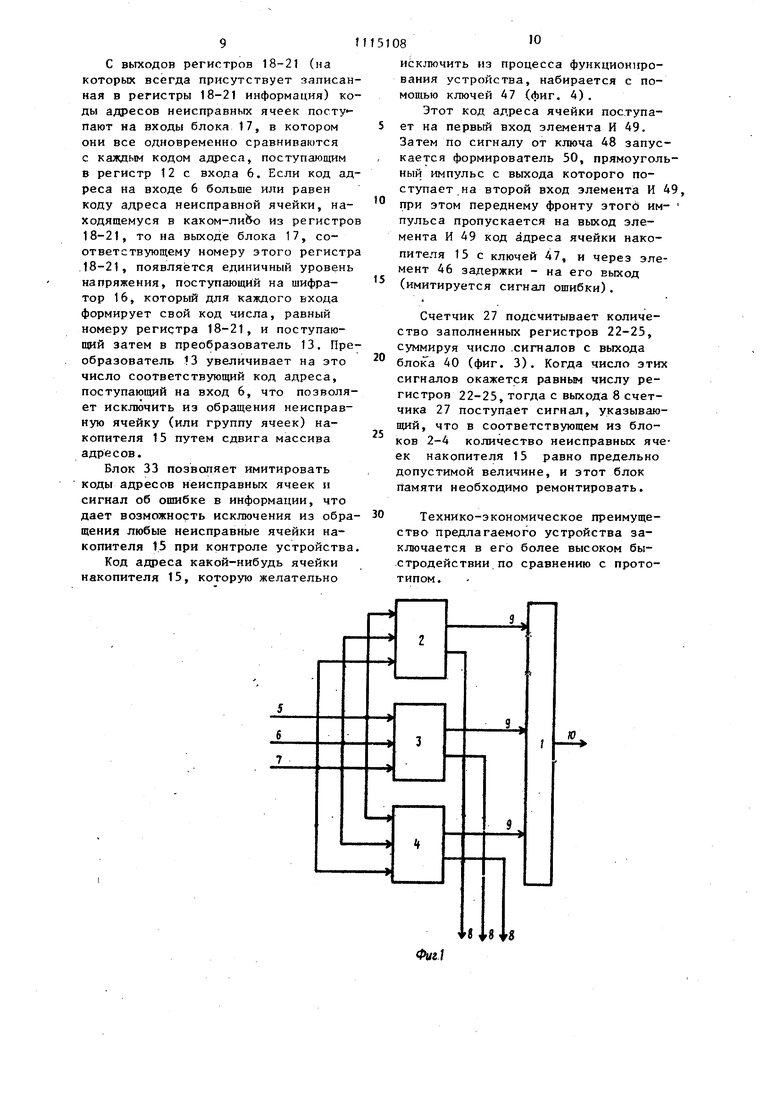

числа, чем при возникновении одного дефекта, что снижает быстродействие устройства, и невозможность применения в нем несамокорректирующих кодов. 3 Цель изобретения - повышение быстродействия запоминающего устройства путем осуществления возможности выявления и исключения в процессе функционирования устройства неисправных ячеек в течение одного такта обращения к нему при записи в него информации, представленной как самокорректирующим, так и несамокорректирующим кодом. Поставленная цель достигается те что в запоминающее устройство с бло кировкой неисправных ячеек, содержа щее блок коррекции ошибок, выход ко торого является информационным выходом устройства, и блоки памяти, каяздый из которых содержит накопи- тель, дешифратор адреса, преобразователь кода и информационный регистр, входы которого являются информационными входами блока памяти, причем выходы преобразователя кода соединены с входами дешифратора адреса, выходы Которого подключены к адресным входам накопителя, выходы которого соединены с соответствующими входами блока коррекции ошибок, в каждый блок памяти введены шифратор, первый блок сравнения, группы регистров адреса неисправной ячейки, блок сортировки, формирователь импульсов сброса, блок индикации, формирователь контрольных сигналов, блок контроля, блок местного управления, элементы ИЛИ, формирователь TaKfoBbix импульсов, первый элемент И, счетчик и регистр адреса, входы которого являются адресными входами блока памяти, причем выходы информационного регистра соединены с входами формирователя кон рольных сигналов, выходы которого подключены к информационным входам накопителя, выходы которого соедине с входами блока контроля, выходы ре гистра адреса подключены к одним из входов преобразователя кода и одним из входов первого блока сравнения, выходы которого соединены с входами шифратора, .выходы которого подклю- цены к другим входам преобразовател кода, выходы которого соединены с первым входом первого элемента ИЛИ, другие входы первого блока сравнения подключены к выходам регистров адреса неисправной ячейки первой группы, первые входы которых и первые входы регистров адреса неиспран 084 ной ячейки второй группы соединены с выходом формирователя импульсов сброса и входом сброса счетчика, выход блока контроля подключен к первому входу второго элемента ИЛИ, выход которого соединен с первым входом первого .элемента И и входом формирователя тактовых импульсов, выход которого подключен к тактовому входу блока сортировки, вторые входы первого и второго элементов ИЛИ подключены соответственно к адресному и управляющему выходам блока местного управления, выход первого элемента ИЛИ соединен с вторым входом первого элементаИ и вторыми входами регист-ров адреса неисправной ячейки второй группы, третьи входы которых подключены к тактовым выходам блока сортировки, информационные выходы которого соединены соответственно с четвертыми входами регистров адреса неисправной ячейки второй группы, кроме первого, и счетньм входом счетчика, выход каждого регистра адреса неисправной ячейки второй группы подключен к пятому входу последующего регистра адреса неисправ- . ной ячейки второй группы,соответствующему входу блока индикации, второму входу одноименного регистра адреса неисправной ячейки первой группы и одному из информационных входов блока сортировки, другой информационный вход которого соединен с выходом первого элемента И, третьи входы регистров адреса неисправной ячейки первой группы объединены и являются управляющим входом блока памяти, адресные,информационные и управляющие входы блоков памяти соответственно объединены и являются входами устройства, управляющими выходами которого являются выхо-ды счетчиков. I Казкдый блок сортировки содержит элементы И с второго по шестой и блоки сравнения с второго по пятый, первые входы которых являются информационными входами блока с первого по четвертый, вторые входы - пятым информационным входом блока, а первые выходы являются информационными выходами блока и подключены к первым входам элементов И с третьего по шестой, выходы которых являются тактовыми выходами блока, причем вторые выходы блоков сравнения с второго по пятый соединены с входами с первого по четвертый второго элемента И, выход которого подключен к вторым входам элементов И с третьего по шестой, а пятый вход второго элемента И является- тактовым входом блока. Кроме того, каждый бло1с местного управления содержит седьмой элемент И, формирователь одиночного импульса, ключ, элемент задержки и группу ключей, выходы которых соединены с первым входом элемента И, йторой вход которого и вход элемента задержки соединены с выходом формирователя одиночного импульса, вход которого подключен к выходу клю ча, причем выход седьмого элемента И и выход элемента задержки являются соответственно адресньм и управляющим выходами блока. На фиг. 1 изображена структурная схема устройства; на фиг. 2 - функциональная схема каяздого блока памяти; на фиг. 3 и 4 -функциональные сх мы блоков сортировки и местного упра ления соответственно. Устройство содержит (фиг. 1) блок 1 коррекции ошибок, блоки 2-4 памяти с информационными 5, адресными 6 и управляющими 7 входами и управляющими 8 и информационными 9 выходами Устройство имеет информационный 10. Каждьй блок 2-4 памяти содержит (фиг. 2) информационный регистр J1, регистр 12 адреса, преобразователь 13 кода, дешифратор 14 адреса, накопитель 15, шифратор 16, первый блок 17 сравнения, первую группу регистров 18-21 адреса неисправной ячейки вторую группу регистров 22-25 адреса неисправной ячейки,блок 26 сортировки, счетчик 27, ,рм-ирователь 28 импульсов сброса, блок 29 индикации, формирователь 30 контрольных сигналов, блок 31 контроля, блок 32 местного управления, первый 33 и второй 34 элементы ИЛИ, первый элемент И 35,формирователь 36 тактовых импульсов Каждый блок 26 сортировки (фиг.З содержит блоки 37-40 сравнения с второго по пятый и элементы И 41-45 с второго по шестой. Каждый блок 32 местного управления содержит (фиг. 4) элемент 46 задержки, группу 47 ключей, ключ 48 седьмой элемент И 49 и формирователь 50 одиночного импульса, Устройство работает следующим об разом. Информационные слова, представленные Самокорректирующим или несамокорректирующим (параллельным двоичным импульсным) кодом, поступают с входов 5 (фиг. 1 и 2) одновременно в блоки 2-4, где одновременно записывается в ячейки накопителей 15 по адресам, коды которых одновременно поступают с входов 6. В накопитель 15 каждого из блоков 2-4 . по одинаковым адресам одновременно записывается одинаковая информация. При чтении информационные слова, представленные параллельно двоичным кодом, с выхода 9 каждого из блоков 2-4 поступают одновременно на входы блока 1. Из ячеек накопителя 15 с одинаковым адресом с выходов 9 блоков 2-4 в блок 1 поступает одинаковая информация. Если в считываемой информации имеются ошибки, то они корректируются в блоке 1 с помощью самокорректирующего кода, или (если информационное слово представлено несамокорректирующим кодом) путем , одновременного сравнивания информационных слов, считанных из блоков 2-4. Откорректированная информация поступает на выход 10. Выявление и блокировка неисправHbtx ячеек в каждом из блоков 2-4 за один такт обращения к устройству происходит следующим образом. Перед началом функционирования устройства все разряды регистров 18-21 и счетчика 27 устанавливаются в нулевое положение, а все разряды регистров 22-25 в единичное положение по сигналу с выхода формирователя 28. Последовательность информационных слов (с контрольными разрядами или без контрольного разряда каждое слово) с выхода регистра 11 поступает на вход формирователя 30, в котором она передается на его выход и одновременно с этим формируется дополнительный контрольньй разряд для каждого информационного слова который вместе со своим информационным словом с выхода формирователя 30 записывается в накопитель 15 по адресам, коды которых поступают с выхода регистра 12 через преобразователь 13 и дешифратор 14. При чтении информации с выхода накопителя 15 в виде последовательности информационных слов, со своим

7t

дополнительным контрольным разрядом кахдое, поступает на вход блока 31, а без дополнительного контрольного разряда - на выход 9. В блоке 31 каждое информационное слово вместе со своим дополнительным контрольным разрядом подвергается свертке по модулю два. Если в этом информационном слове нет ошибки, то результат свертки будет равен нулю и на выходе блока 31 будет отсутствовать сигнал, что говорит об исправности ячейки, соответствующей адресу, по которому это проверяемое слово было записано в накопитель 15.

Для контроля правильности функци нирования ячейки каждого адреса накопителя 15 могут быть использованы контрольные разряды (если они име.ются) каждого .слова, поступающего на вход регистра 11. В этом случае информационные слова с выхода регистра 11 поступают через формирователь 30 без изменения (т.е.. без формирования дополнительного контрольного разряда на вход накопителя I I

При чтении информация с выхода

накопителя 15 в виде последовательности информационных слов (со своими контрольными разрядами) поступает на вход блока. 31 и на выход блока 9. В блоке 31 в этом случае каждое информационное слово участвует в свертке по модулю два со сво ми контрольными разрядами (например код Хемминга), лричем каждая группа разрядов информационного слова участвует в свертке со своим контрольным разрядом, при этом результаты всех групповых сверток объединяются

При наличии ошибки в информационном слове с выхода блока 31 через элемент ИЛИ 34 поступает сигнал для запуска формирователя 36 и на вход элемента И 35, разрешая прохождение кода адреса ячейки, из которой было считано слово с ошибкой, с выхода преобразователя 13 через элемент ИЛИ 38 и элемент И 35 на пятый информационный вход блока 26, на тактовьй вход которого с выхода формирователя 36 поступает одиночный тактовый импульс с задержкой во времени относительно переднего фрота сигнала на входе запуска формирователя 36 (задержка больше времени; срабатывания блоков 37-40).

5108

Блок 26 предназначен для записи кодов неисправных ячеек в регистры 22-25 R порядке возрастания абсолютных величин кодов этих адресов. 5 Для этого в блоке 26 код адреса каждой новой неисправной ячейки, поступающий с выхода элемента ИЛИ 35 на вторые входы блоков 37-40 (фиг. 3) одновременно сравниваются с кодами неисправных ячеек на выходах регистров 22-25, поступающими через информационные входы блока 26 на первые входы блоков 37-40.

Если код адреса новой неисправной ячейки меньше кода адреса, содержащегося в каком-либо из регистров 22-25, то один из блоков 27-40, соответствующий этому адресу, формирует сигнал, поступающий с выхода

20 соответствующего из блоков 37-40 на соответствующий выход блока 26 и на вход соответствующего из элементов И 42-45, открывая его для прохождения тактового импульса с

тактового входа блока 26 - через элемент И 41 на соответствующий тактовый выход блока 26.

Если же код адреса неисправной ячейки, поступающий на пятый ин-0 формационный вход блока 26, при сравнении окажется равным коду адреса в каком-либо из регистров 2225, то соответствующий блок 37-40 выставляет на втором выходе запре5 щающий сигнал (низкий уровень напряжения) , поступающий на соответствующий вход элемента И 41, закрывая его для прохождения тактового импульса,

Таким образом, если код адреса

новой неисправной ячейки меньще одних из кодов адресов или меньще первоначального единичного кдда, но больше других кодов адресов неисправных ячеек, записанных ранее в регистры 22-25, то большие коды сдвигаются на один из регистров 22-25 в сторону последнего регистра 25, а в освободившийся из регистров 22-25 записывается код адреса новой неисправной ячейки (в последнем регистре 25 информация теряется),

С выходов регистров 22т25 коды адресов неисправных ячеек поступают в блок 29 для визуального контроля и в регистры 18-21, куда записываются по сигналу перезаписи, поступающему с входа 7.

9П

С выходов регистров 18-21 (на которых всегда присутствует записанная в регистры 18-21 информация) коды адресов неисправных ячеек поступают на входы блока 17, в котором они все одновременно сравниваются с каждым кодом адреса, поступающим в регистр 12 с входа 6. Если код адреса на входе 6 больше или равен коду адреса неисправной ячейки, находящемуся в каком-ли з из регистров 18-21, то на выходе блока 17, соответствующему номеру этого регистра 18-21, появляется единичный уровень напряжения, поступающий на шифратор 16, который для каждого входа формирует свой код числа, равный номеру регистра 18-21, и поступающий затем в преобразователь 13, Преобразователь 13 увеличивает на это число соответствующий код адреса, поступающий на вход 6, что позволяет исключить из обращения неисправную ячейку (или группу ячеек) накопителя 15 путем сдвига массива адресов.

Блок 33 позволяет имитировать коды адресов неисправных ячеек и сигнал об ошибке в информации, что дает возможность исключения из обращения любые неисправные ячейки накопителя 15 при контроле устройства

Код адреса какой-нибудь ячейки накопителя 15, которую желательно

5108О

исключить из процесса функционирования устройства, набирается с помощью ключей 47 (фиг. 4).

Этот код адреса ячейки пос.тупа5 ет на первый вход элемента И 49. Затем по сигналу от ключа 48 запускается формирователь 50, прямоугольный импульс с выхода которого поступает на второй вход элемента И 49, при этом переднему фронту этого импульса пропускается на выход элемента И 49 код адреса ячейки накопителя 15 с ключей 47, и через элемент 46 задержки - на его выход (имитируется сигнал ошибки).

Счетчик 27 подсчитывает количество заполненных регистров 22-25, суммируя число .сигналов с выхода бло1Га 40 (фиг. 3). Когда число этих сигналов окажется равным числу регистров 22-25,тогда с выхода 8 счетчика 27 поступает сигнал, указывающий, что в соответствующем из блоков 2-4 количество неисправных ячеек накопителя 15 равно предельно допустимой величине, и этот блок памяти необходимо ремонтировать.

Технико-экономическое преимущество предлагаемого устройства заключается в его более высоком быстродействии по сравнению с прототипом.

.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек | 1973 |

|

SU492935A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с блокировкой неисправных ячеек памяти | 1976 |

|

SU587509A1 |

Авторы

Даты

1984-09-23—Публикация

1983-02-17—Подача