(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1982 |

|

SU1096640A1 |

| Генератор многомерных случайных величин | 1982 |

|

SU1084791A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для считывания графической информации | 1985 |

|

SU1252803A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

| Устройство для формирования изображения | 1987 |

|

SU1478206A1 |

| Устройство для формирования маркера на экране двухгорловой электронно-лучевой трубки | 1983 |

|

SU1280432A1 |

Изобретение относится к вычистп-епьной технике и предназначено дпя использования в спещшлизированных цифровых устройствах обработки дискретной информации, в частности для .обработки дннатной информации.

Известны устройства для вычислевия квадрачного корня из суммы квадратов двух чисел, содержащие сумматоры, бло. ки сдвига и блок управления Cl .

Недостатком этих устройств является их ограниченная область применения.

Наиболее близким к предлагаемому по технической сущности является устройство для вычисления квадратного кория КЗ суммы квадратов двух чисел, содерж. жащее регистры операндов, сумматор, группы элементов И, группы элемевтов ИЛИ, регистр сдвига, распределитель вмпуяьсов к соответствующие связи t2j.

Устройство функционирует в COOTBOIVствии с приближенной зависимостью

l,5YA B :i{A|-HBH-0,5 (|АИВ1).

Недостатком данного устройства является ограниченная область применения, la именно невозможность применять его ;в системах управления, где возникает необходимость вычислять расстояние меж5ду двумя точками, заданными координатами X и У. Кроме то1ч, наличие коэффициента, равного 1,5, успЕякняет эксплуатацию устройства, так как необходимо осуществлять пересчет.

10

Цель изобретения - расширение области применения устройства за счет вычисления функций (расстояния между двумя произвольными точками), в ортом.

15 гональной системе координат.

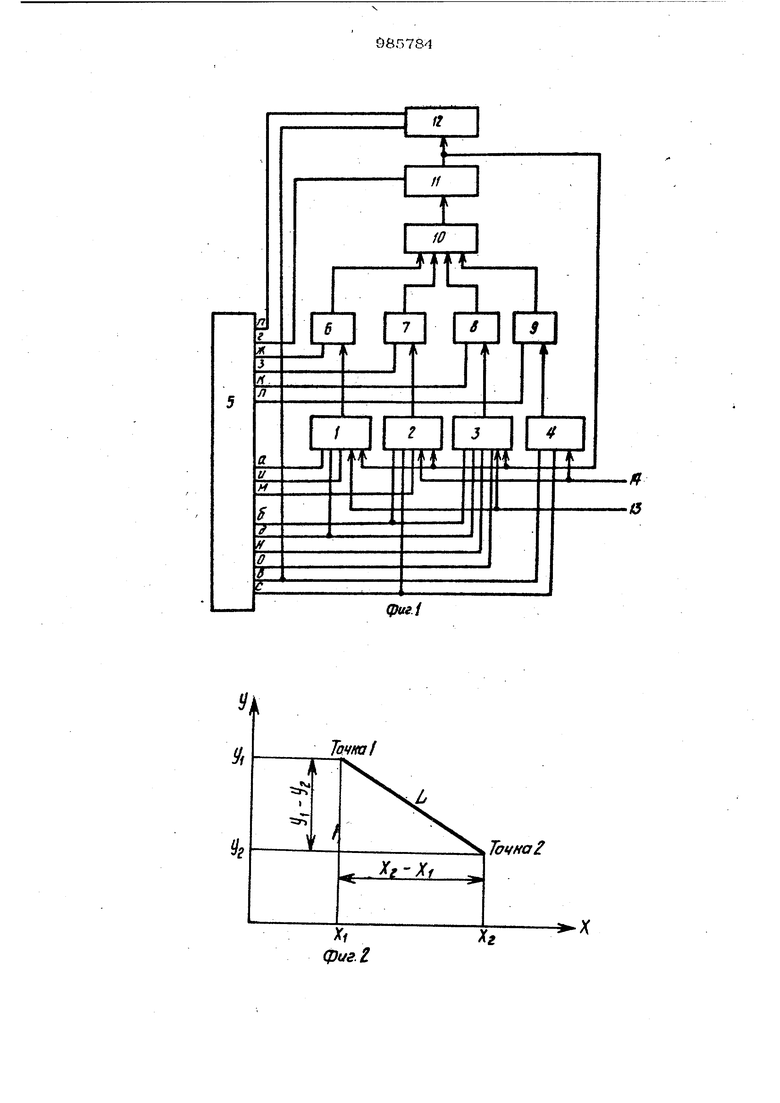

Поставленная цель достигается тем, что в вычислительное устройство, содерцжащее первый, второй и третий регистры, блок распределения импульсов, первую

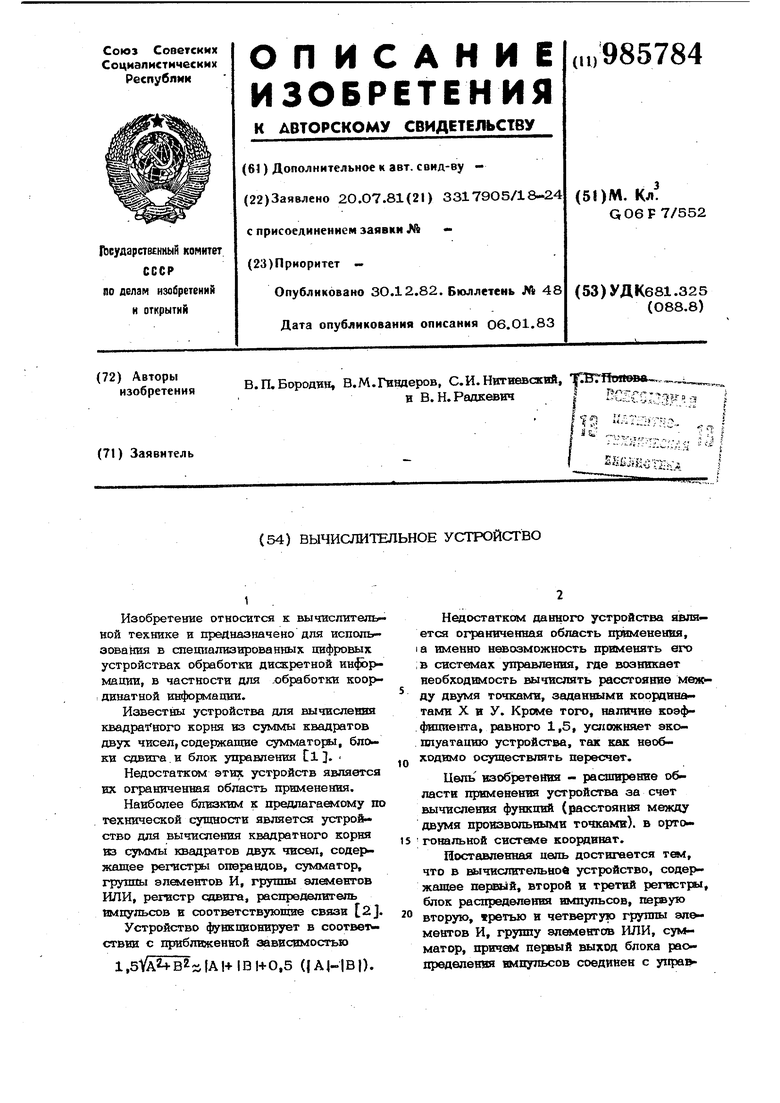

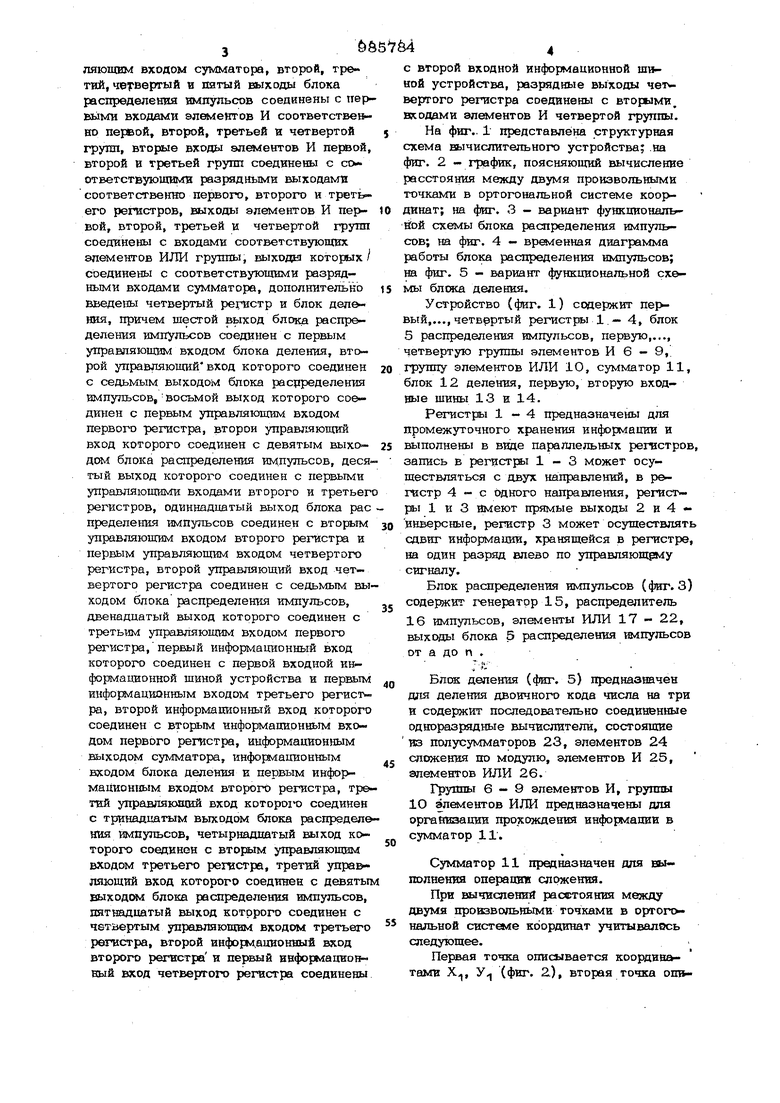

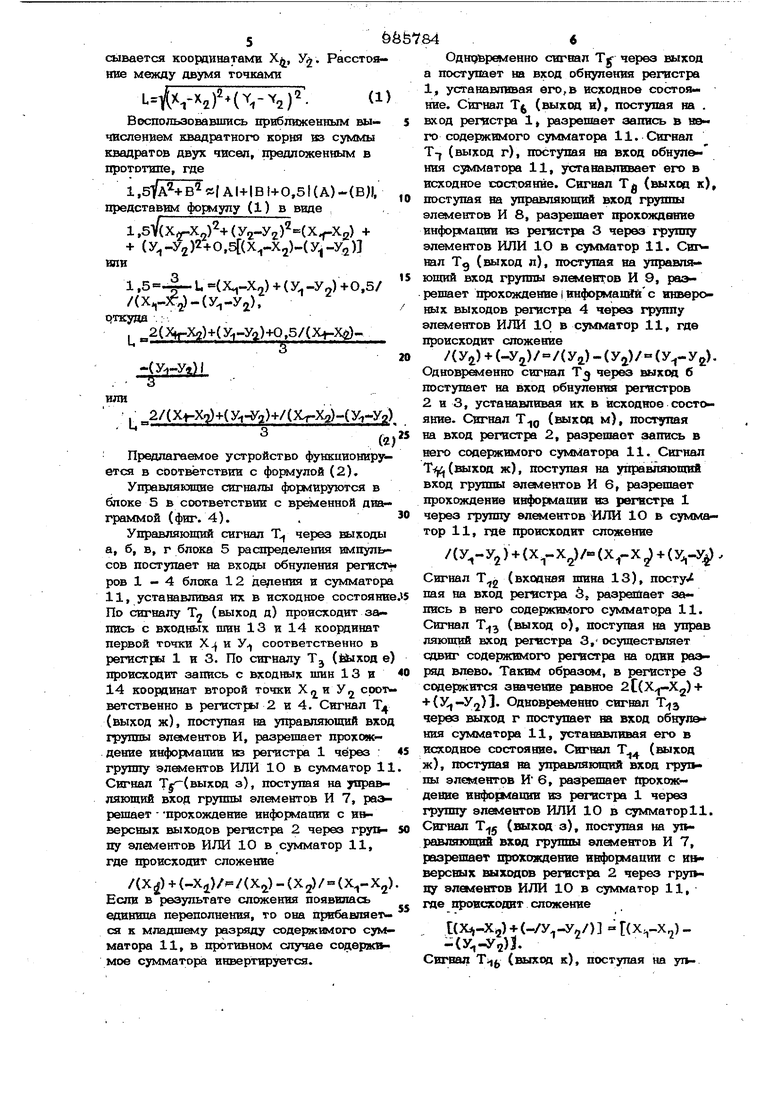

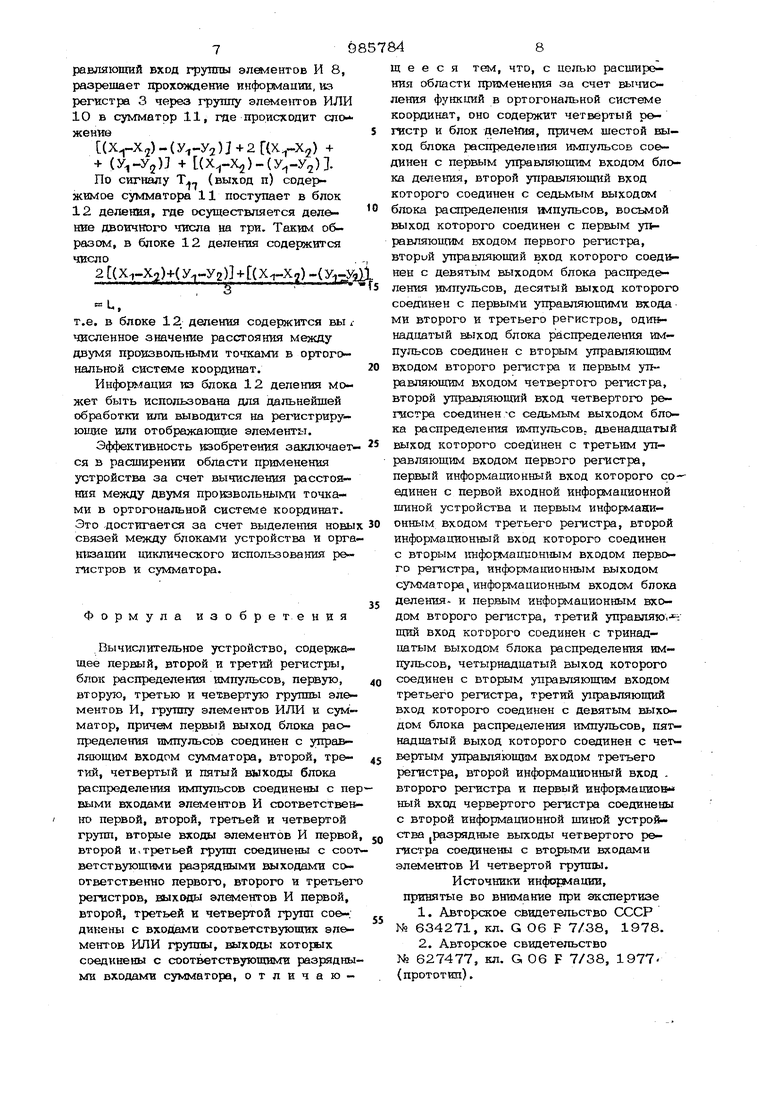

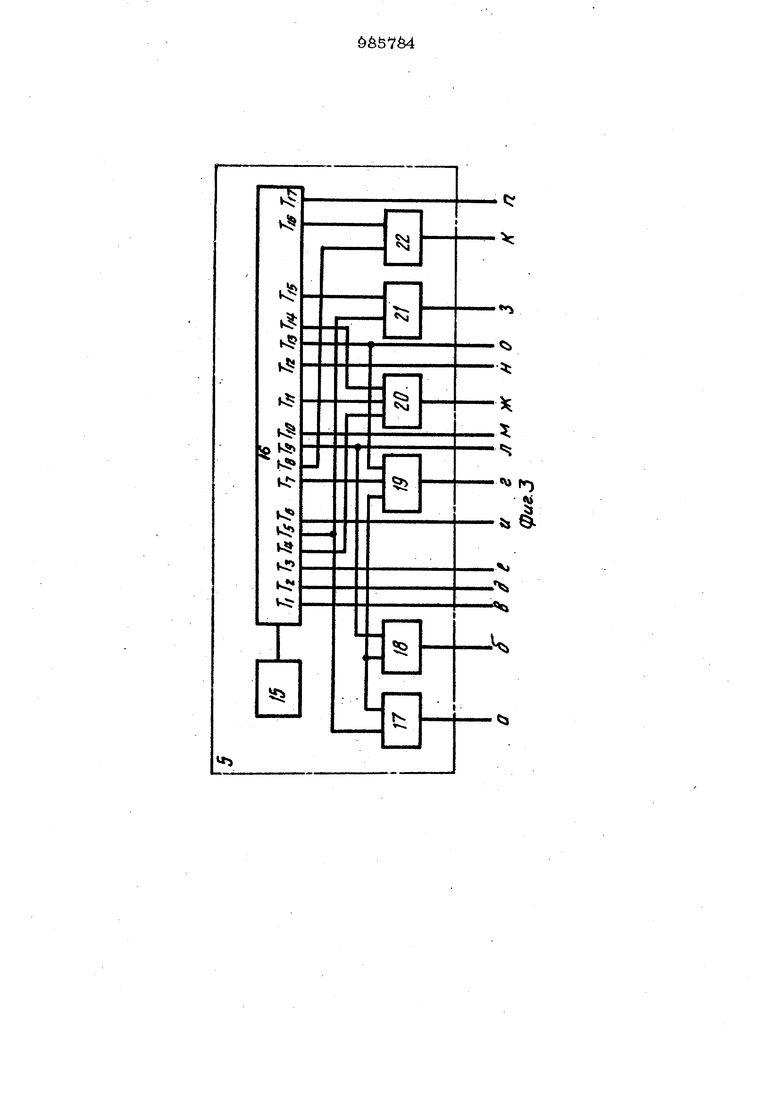

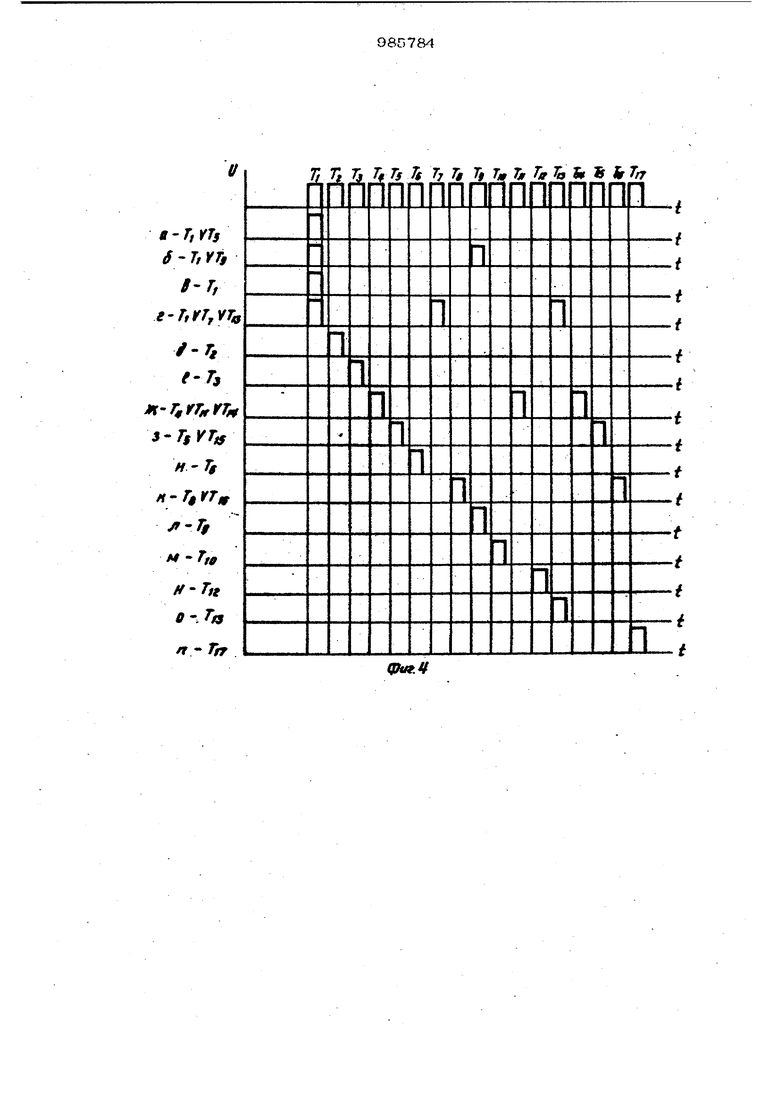

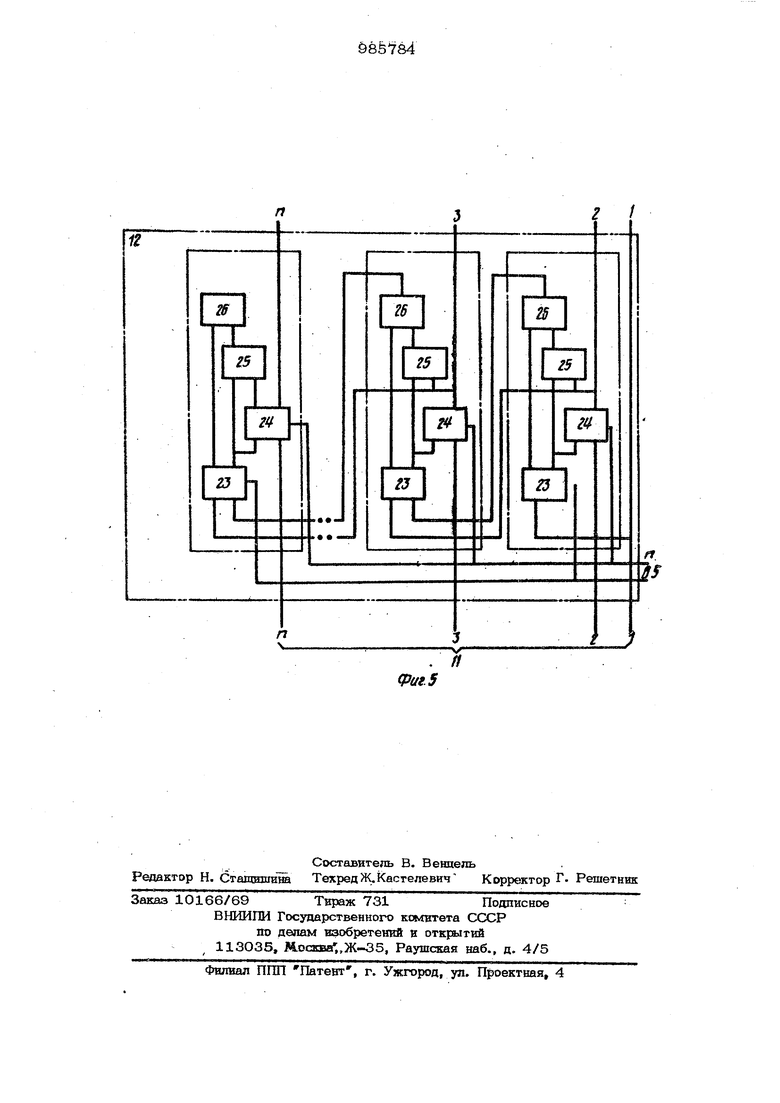

20 вторую, сретью и четвертую группы элементов И, группу элемевтов ИЛИ, сук матор, причем первый выход блока рао пределевня вмпульсов соединен с упра ляющим входом сумматора, второй, тре тий, четвертый и пятый выходы блока распределения импульсов соединены с пер выми входами элементов И соответственно первой, второй, третьей и четвертой групп, вторые входы элементов И первой, второй и третьей групп соединены с соответствующими разрядными выходами соответственно первого, второго и третьего регистров, выходы элементов И первой, второй, третьей и четвертой групп соединены с входами соответствующих элементов ИЛИ группы, выходи которых/ соединены с соответствующими разрадными входами сумматора, дополнительно введены четвертый регистр и блок деления, причем шестой выход блока распр&деления импульсов соединен с первым управляющим входом блока деления, второй управляющий вход которого соединен с седьмым выходом блока распределения импульсов, восьмой выход которого соединен с первым управляющим входом первого регистра, второй управляющий вход которого соединен с девятым выходом блока раатределения импульсов, деся тый выход которого соединен с первыми управляющими входами второго и третьег регистров, одиннадцатый выход блока рас пределения импульсов соединен с вторым управляющим входом второго регистра и первым управляющим входо1у1 четвертого регистра, второй управляющий вход четвертого регистра соединен с седьмым вы ходом блока распределения импульсов, двенадцатый выход которого соединен с третьим управляющим входом первого регистра,первый информационный вход которого соединен с первой входной и формационной щиной устройства и первым информационным входом третьего регистра, второй информационный вход которого соединен с вторым информационным вхо дом первого регистра, информационным выходом сумматора, информационным входом блока деления и первым инфо1 мацион1вым входом второго регистра, тре тий управляющий вход которошэ соединен с тринадцатым выходом блока распределе ния импульсов, четырнадцатый выход которого соединен с вторым управляющим входом третьего регистра, третий упра&ляющий вход которого соединен с девяты выходе блока распределения импульсов, пятнадцатый выход которого соединен с четвертым управляющим входом третьего регистра, второй информдционный вход вторюго регнстра и переый ввформацио Бий вход четвертого регистра соединены С второй входной информационной шииой устройства, разрядные выходы четвертого регистра соединены с вторыми, входами элементов И четвертой группы. На фиг.. 1 представлена структурная схема вычислительного устройства; .на фиг. 2 - график, поясняющий вычисление расстояния между двумя произвольными точками в ортогональной системе координат; на фиг. 3 - вариант фушспиональЙой схемы блока распределения импульсов; на фиг. 4 - временная диаграмма работы блока распределения импульсов; на фиг. 5 - вариант функциональной блока деления. Устройство (фиг. 1) содержит первый,..., четвертый регистры 1.- 4, блок 5 распределения импульсов, первую,..., четвертую группы элементов И 6 - 9,. l jyimy элементов ИЛИ 10, сумматор 11, блок 12 деления, первую, вторую входные шины 13 и 14. Регистры 1-4 предназначены для промежуточного хранения информации и выполнены в ввде параллельных регистров, запись в регистры 1-3 может осуществляться с двух направлений, в р&гистр 4 - с одного направления, решстр 1 1 и 3 имеют прямые выходы 2 и 4 инверсные, регистр 3 может осуществлять сдвиг информации, хранящейся в регистре, на один разряд влево по утфавляющрму сигналу. Блок распределения импульсов (фиг. 3) содержит згенератрр 15, распределитель 16 импульсов, элементы ИЛИ 17 - 22, выходы блока 5 распределения галпульсов от а до п . Блок деления (фиг. 5) предназначен щш деления двоичного кода числа на три и содержит последовательно соединенные одноразрядные вычислители, состоящие да полусумматоров 23, элементов 24 сложения по модулю, элементов И 25, элементов ИЛИ 26. Группы 6-9 элементов И, группы 1О элетлентов ИЛИ предназначены для организации прохождения информации в сумматор 11. Сумматор 11 предназначен для выполнения операции сложения. При вычислений расстояния между двумя произвольными точками в ортоп наяьной системе координат учитывалось следующее. Первая точка описывается координ тамв Х, У (фиг. 2), вторая точка оп сывается координатами Х, У,, Расстоя- ние между двумя точками 1ф,-чМ) Веспользовавпгась приближенным вычислением квадратного корня из суммы квадратов двух чисел, предложенным в прототипе, где 1 . AH-IB 14-0,51 (А)-{ВЛ, представим формулу (1) в виде i,5T/()4( + + ()2+0,5(Х -Х2МУ,-У2) или 1,. (Х,-Х2) -«-(У.-Уо) +0,5/ /()e,j)-(y-i-y2 рткуяа .:. I 2(Хн-Х2)+(У,-.Уа)-Ю,5/(Х -Х U3)1 . 3 Г /(Х|-Хд)+( )+/(Хг-Х.г)() С. Предлагаетлое устройство функииониру- ется в соответствии с формулой (2), Управляющие сигналы формируются в блоке 5 в соответствии с вретленной диаграммой (фиг. 4).. Управляющий сигнал Т, через выходы а, б, в, г блока 5 расяределетш импульсов поступает на входы обнуления регистров 1-4 блока 12 деления и сумматора 11, устанавливая их в исходное состояние По сигналу Т (выход д) происходит запись с входных шин 13 и 14 координат первой точки Х и У соответственно в решсгры 1 и 3. По сигналу Т ( е происходит запись с входшлх шин 13 и 14 координат второй точки Х., 2 cpoivветственно в регистры 2 и 4. Сигнал Т (выход ж), поступая на управляющий вход группы элементов И, разрешает прохождение информации из регистра 1 через : группу элементов ИЛИ 10 в сумматор 11 Сигнал Т( выход з), поступая на управляющий вход группы элементов И 7, разрешает Прохождение информации с иоверсных выходов регистра 2 через элементов ИЛИ 1О в сумматор 11, где происходит сложение /(Х) + (-Х,)(Х,)-(Х2)/ () Если в результате сложения появилась едивиоа переполнения, то она прибавляе ся к младшй у разряду содержимого сумматора 11, в противном случае содерял мое сумматора инвертируется. e S4 Одновременно сигнал Tj- через выход а поступает на вход обнуления регистра 1, устанавливая е1п,в исходное состояние. Сигнал Т (выход и), поступая на . вход регистра 1 разрешает запись в него содержимого сумматора 11. Сигнал T-J (выход г), поступая на вход обнулвния сумматора 11, устанавливает его в исходное состояние. Сигнал Tg (выхоа к), поступая на управляющий вход группы элементов И 8, разрешает прохождение информации из регистра 3 через группу элементов ИЛИ 1О в сумматор 11. Тд (выход л), поступая на управляющий вход группы элементов И 9, разрешает прохождение I информации с инвероных выходов регистра 4 через группу элементов ИЛИ 1О в сумматор 11, где происходит сложение /(У2) + (-У2))-(Уа5/-(У1-Уе)Одновременно сигнал Тд через выход б поступает на вход обнуления регистров 2 и 3, устанавливая их в исходное состояние. Сигнал (выход м), поступая на вход регистра 2, разреоюет запись в него содержимого сумматора 11. Сигнал Т (клход ж), поступая на управляющий вход группы элементов И 6, разрешает прохождение информации из регистра 1 через группу элементов ИЛИ 1О в сумматор 11, где происходит сложение /()-«-()/() + ( Сигнал (входная шина 13), посту, пая на вход регистра 3 разрешает запись в него содержимого сумматора 11. Сигнал (выход о), поступая на упреш ляющий вход регистра 3,- осуществляет сдвиг содержимого регистра на одии разряд . Таким образом, в регистре 3 содержится значение равное 2t(y + + (У,-У2)1. Одновременно сигнал Т через выход г поступает ш вход обнул ния сумматора 11, устанавливая его в исходное состояние. Сигшл Т (выход ж), постушш на управляющий вход груп пы элементов И6, разрешает Прохождение информации из регистра 1 через группу элементов ИЛИ 10 в сумматор 11. Сигнал Т (выход з), поступая на управогаюпшй вход группы элементов И 7, разрешает прохсякдение информации с иви версиых выходов регистра 2 через группу элементов ИЛИ 1О в сумматор 11, где происходит сложение t(X4i-X2) + (-/y--y,,/) Г(Х.-Х„))1. Сигнал , (выход к), поступая на уп-. равляющий вход грутаты элементов И 8, разрешает прохождение информации, из регистра 3 через группу элементов ИЛИ 1О в сумматор 11, где происходит ело-женке() - (У-,-У2) J + 2 Г(Х,-Х2) + + ( + (.Х2)-()1. По сигналу Т (выход п) содержимое сумматора 11 поступает в блок 12 деления, где осуществляется дел&ние двоичного числа на три. Таким образом, в блоке 12 деления содержится число 2С(Х1-Х2)+()-ьГ()(.У . т.е. в блоке 12 деления содержится вы i Численное значение расстояния между двумя произвольными точками в ортогональной системе координат. Инфорфлация из блока 12 деления может быть использована для дальнейшей обработки или выводится на регистриру- юидие или отображаюпгие элементы. Эффективность изобретения заключает ся S расширении области применения устройства за счет вычисления расстояния между двумя произвольными точками в ортогональной системе координат. Это достигается за счет выделения новы связей между блоками устройства и орга шззатге циклического использования регистров и сумматора. Формула изобретения Вычислительное устройство, содержащее первый, второй и третий регистры, блок распределения mv пyльcoв, первую, вторую, третью и четвертую группы элементов И, группу элементов ИЛИ и сумматор, причем первый выход блока распределения импульсов соединен с упра&ляющим входом сумматора, второй, третий, четвертый и пятый выходы блока распределения импульсов соединены с пе выми входами элементов И соответствен но первой, второй, третьей и четвертой групп, вторые входы элементов И перво второй и третьей групп соединены с соо ветствующими разрядными выходами соответственно первого, второго и третьег регистров, выходы элементов И первой, второй, третьей и четвертой групп сое. динены с входами соответствующих элементов ИЛИ группы, выходы которых соединены с соответствующими разрядны ми входами сумматора, отлнчающ е е с я тем, что, с цс1шю расигаре- ния области применения за счет вьпгасления функций в ортогональной системе координат, оно содержит четвертый регистр и блок деления, причем шестой выход блока распределения импульсов соединен с первым управляющем входом блеска деления, второй управляющий вход которого соединен с седьмым выходом блока распределения тыпульсов, ВОСЬАЛОЙ выход которого соединен с первым управляющим входом первого регистра, вторий управляющий вход которого с девятым выходом блока распределения импульсов, десятый выход которого соединен с первыми управляющими входа ми второго и третьего регистров, оди наддатый выход блока распределения импульсов соединен с вторым управляющим входом второго регистра и первым утьpaвляющжv входом четвертого регистра, второй управляющий вход четвертого ре- тастра соединение седьмым выходом блока распределения импульсов, двенадцатый выход которого соединен с третьим управляющим входом первого регистра, первый информационный вход которого соединен с первой входной информационной шиной устройства и первым информанионным входом третьего регистра, второй информационный вход которого соединен с вторым информашюнным входом первого регистра, инфорзмационным выходом сумгматора, информационным входом блока деления- и первым информационным входом второго регистра, третий управляю,щкй вход которого соединен с тринадцатым выходом блока распределения импульсов, четырнадцатый выход которого соединен с вторым управляющим входом третьего регистра, третий управляющий вход которого соединен с девятым выходом блока распределения импульсов, пятнадцатый выход которого соединен с четвертым управляющим входом третьего регистра, второй информационный вход . второго регистра и первый информациов ный вход червертого регистра соединены с второй информационной шиной устройства разрядные выходы четвертого регистра соединены с вторыми входами элементов И четвертой группы. Источники инфо{я 1ации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 634271, кл. G Об F 7/38, 1978. 2.Авторское свидетельство Мо 627477, кл. G 06 F 7/38, 1977. (npoTDTmi).

Точка

Тоцна

Д-Г,КГ, 6-T,Yff

8-Г, e-TtirTjyTff

/Г

f-T9

TtYTts

HTf Tt M-Tfo

ff Tn O.Ta

/r - TfT

(Puf,4

п

г

, п

(риг. 5

Авторы

Даты

1982-12-30—Публикация

1981-07-20—Подача