го элемента ИЛИ и вторым выходом распределителя импульсов, третий выход которого соединен с единичным входом третьего и нулевым входом четвертого триггеров, нулевой вход первого триггера -соединен с единичным входом четвертого триггера, перзым входом шестого элемента И и вы, ходом седьмого элемента И, входы которого соединены с соответствующими выходами разрядов счетчика, выход переполнения которого соедине с вторым входом шестого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ и нулевым входом третьего триггера, выход третьего коммутатора соединен с первыми информационными входами первого и второго компараторов,первые выходы результатов сравнения операндов которых соединены соответственно с первым и вторым входами восьмого элемента И соответственно, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом девятого элемента И, первый и второй входы которого соединены с вторыми выходами результатов сравнения операндов соответственно первого и второго;компараторов, управляющие входы которых соединены с выходом третьего элемента ИЛИ, выход четвертого элемента ИЛИ соединен через элемент НЕ с вторыми входами четвертого и пятого элементов И, выходы которых соединены с единичными входами второго и пятого триггеров соответственно, первый и второй входы пятого элемента ИЛИ соединены с выходами первого и десятого элементов И соответственно первые входы которых соединены с выходами первого и второго вычитсС телей аргумента соответственно, первые входы операндов которых соединены с выходом первого коммутатора и выходами элементов .И первой группы,вторые входы операндов первого и второго вычитателей аргумент соединены с выходом второго коммутатора и выходами элементов И второй группы соответственно, выход вшоррго элемента И соединен с управляющим входом счетчика, информационный вход четвертого блока поворота вектора соединен с четвертой группо входов операндов преобразователя, l epeaa группа выходов операндов

четвертого блока поворота вектора соединена с информационными входами .элементов И третьей группы, управляющие входы которых соединены с выходом второго элемента ИЛИ блока управления и управляющими входами элементов И четвертой группы преобразователя, информационные входы которых соединены с первой группой выходов операндов блока поворота вектора и первым информационным входом первого коммутатора блока управления, второй информационный вход первого коммутатора блока управления соединен с вторым входом первого компаратора блока управления и второй группой выходов операндов второго блока поворота вектора, первая группа выходов операндов которого соединена с первым информационным входом второго коммутатора .блока управления и информационными входами элементов И пятой группы, управляющие входы которых соединены с выходом второго элемента ИЛИ блока управления и управляющими входами элементов И шестой группы преобразователя, информационные входы которых соединены с первой, группой выходов операндов третьего блока поворота вектора, вторая группа выходов операндов которого .соединена с вторым информационным входом второго коммутатора блока управления и первым информационным входом третьего коммутатора, второй информационный вход которого соединен с вторыми входами элементов И первой группы и. второй группой выходов операндов четвертогоблока поворота вектора, вторая группа выходов операндов первого блока поворота вектора соединена с первыми входами элементов И второй группы и вторым информационным входом второго компаратора, ВЫХОД пятого элемента ИЛИ блока управления соединен с первыми управляющими входами первого и четвертого блоков поворота вектора, вторые управляющие входы которых соединены с выходом второго элемента И блока управления, управляющими входами первого и второго мнЬжитель но-делительных блоков и вторыми управляющими входами второго и третьего блоков поворота вектора преобразователя, первые уп равляющие входы которых соединены с выходами первого вычитателя аргумента блока управлепия, второй выход распределите. импульсов блока управления соединен с вторыми управляющими входами первого и второго множительно-делительных блоков, третьи управляющие входы которых соединены с четвертым выходом распределителя импульсов блока управления, выход шестого элемента И блока управления соединен с четвертыми управляющими входами первого и второго множительноделительных блоков, выходы которых соединены соответственно с пятой и шестой группами выходов преобразователя, выходы элементов И третьей и четвертой групп соединены соответственно с входами первого и второго операндов первого вычитателя, выход которого соединен с второй группой выходов преобразователя и с первыми информационными входами первого и второго множительно-делительных блоков, вторые информационные входы которых соединены с выходом второго вычитателя, входы первого и второго операндов которого соединены с выходами элементов И пятой и шестой групп соответственно, выходы второго вычитателя соединены с первой группой выходов преобразователя, третьи информационные входы первого и второго множительно-делительных блоков соединены с третьей группой входов операндов преобразователя, четвертая группа входов операндов соединена с четвертыми информационными входами первого и второго множительно-делительных блоков.

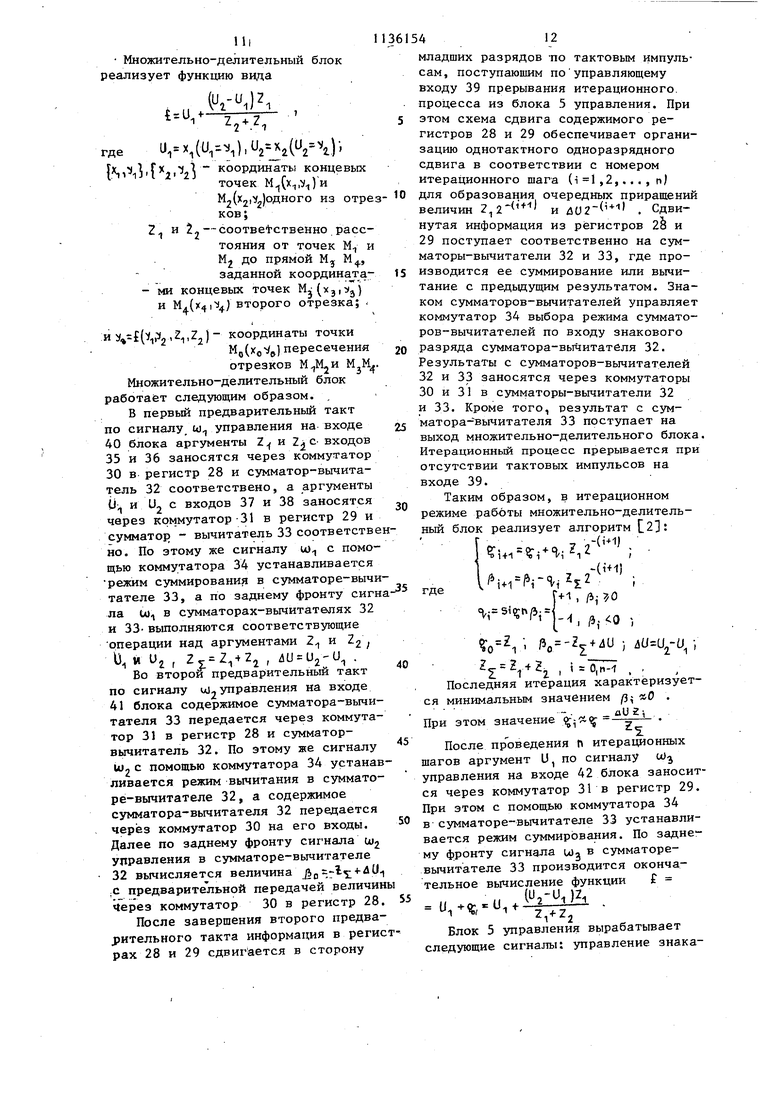

2. Преобразователь по п. 1, отличающийся тем, что каждый множительно-делительный блок содержит первый, второй и третий коммутаторы, первый и второй регистры сдвига,первый и второй сумматоры - вычитатели, причем первый информационный вход первого коммутатора соединен с первым информационным входом второго коммутатора и первым информ ционным входом множительно-делительЬ|54

ного блока, первый управляющий вход которого соединен с управляющими входами первого и второго регистров сдвига, разрядные выходы которых соединены с первыми входами операндов соответствующих сумматоров -вычитателей, вторые входы операндов которых соединены с первыми выходами соответствующих коммутаторов, вторые выходы которых соединены с разрядными входами соответствующих регистров сдвига, выходы первого и второго сумматоров-вычитателей соединены с вторыми информационными входами соответствующих коммутаторов, вьгход знакового разряда первого сумматора-вычитателя соединен с управляющим входом третьего коммутатора, выход которого соединен со знаковыми входами первого и второго сумматоров-вычитателей, второй управляющий вход множительно-делительного блока соединен с первым информационным входом третьего коммутатора и первыми управляющими входами первого и второго коммутаторов, вторые управляющие входы которых соединены с третьим управляющим входом множительно-делительного блока и вторым информационным входом третьего коммутатора, третий информационный вход которого соединен с третьимуправляющим входом второго коммутатора и .четвертым управляющим входом множительно-делительного блока, второй информационный вход которого соединен с третьим информационным входом второго коммутатора, третий информа ционный выход которого соединен с разрядными входами первого регистра сдвига, третий и четвертый информационные входы множительно-делительного блока соединены с третьими и четвертыми информационными входами соответственно первого и второго - коммутаторов, информационный выход второго сумматора-вычитателя соединен с выходом множительно-делительного блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1986 |

|

SU1456951A1 |

| Функциональный преобразователь | 1980 |

|

SU924714A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1105888A1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Вычислительное устройство | 1986 |

|

SU1361546A1 |

| Матричный преобразователь координат | 1988 |

|

SU1559343A1 |

| Устройство для вычисления элементарных функций | 1986 |

|

SU1310812A1 |

| Цифровое множительно-делительное устройство | 1990 |

|

SU1730623A1 |

| Устройство для вычисления модуля трехмерного вектора | 1989 |

|

SU1672442A1 |

| Устройство для преобразования координат вектора в трехмерном пространстве | 1986 |

|

SU1403062A1 |

1. ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий первый, второй и третий блоки поворота вектора, информационные входы которых являются соответственно первой, второй и третьей группами входов операндов преобразователя, два элемента И, вычитатель, блок управления, содержащий вычитатель аргумента, счетчик, два триггера, пять элементов И , первый и второй коммутаторы, первый и второй компараторы, первый, второй и третий элементы ИЛИ и элемент НЕ, отличающийся тем, что, с целью расширения функциональных возможностей путем дополнительного вычисления координат точки пересечения двух отрезков на плоскости и расстояний от концевых точек одного из отрезков до другого отрезка и между концевыми точками отрезков, он дополнительно содержит четвертый блок поворота вектора, третью и четвертую группу элементов И, второй вычитатель, первый и второй множительно-делительные блоки, а .в блок управления уведены второй вычитатель аргумента, две группы элементов И, третий коммутатор, три триггера, распределитель импульсов, пять элементов И и два элемента ИЛИ, причем в блоке управления единичный выход первого триггера соединен с .первым входом первого элемента ИЛИ, вторым входом первого элемента И и первыми управляющими входами первого и второго коммутаторов, вторые управляющие входы первого и второго коммутаторов соединены с управляющими входами элементов И первой и (Л второй групп, единичным выходом третьего триггера, вторым входом десятого элемента И и вторым входом первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с тактовым входом преобразователя и с первым входом третьего со элемента И, второй вход которого Од соединен с единичным выходом четвертого, триггера, нулевой вход которого ел соединен с единичным входом первого, 4; нулевыми входами второго, третьего и пятого триггеров и установочным входом преобразователя, выход третьего элемента И соединен с управляю щим входом распределителя импульсов, первый выход которого соединен с первыми входами второго и третьего элементов ИЛИ и первым управляющим входом третьего коммутатора, второй управляющий вход которого соединен с первыми входами четвертого и пятого элементов И, вторым входом третье

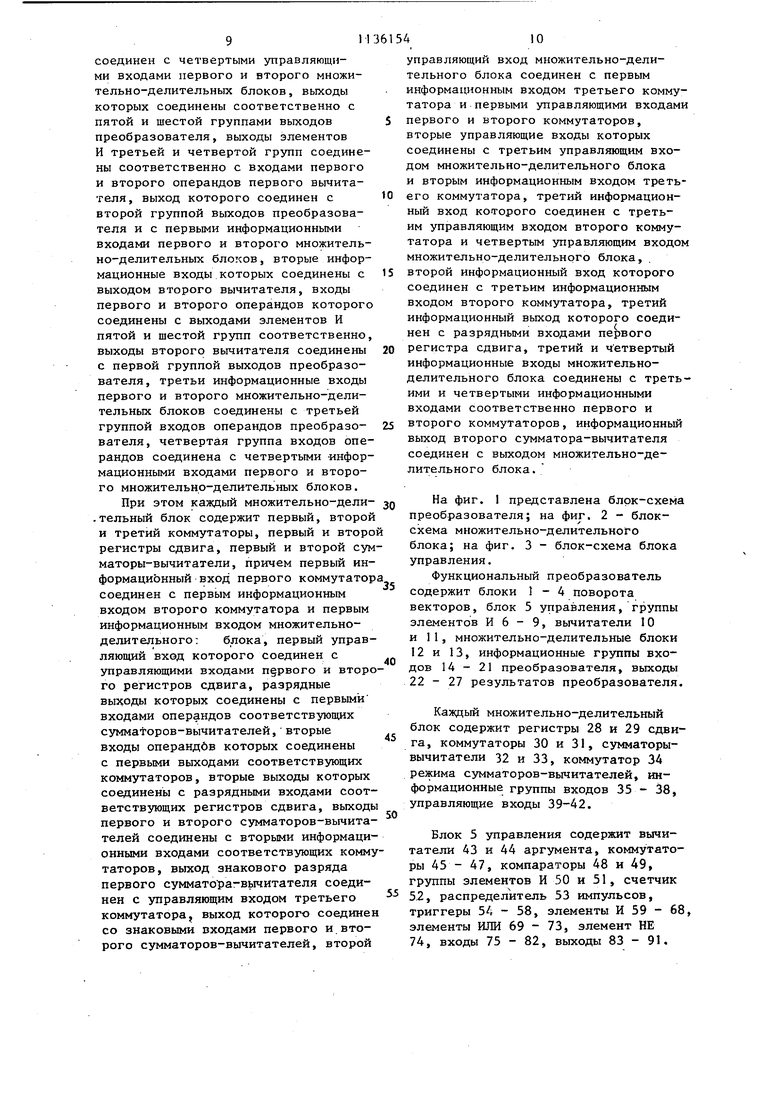

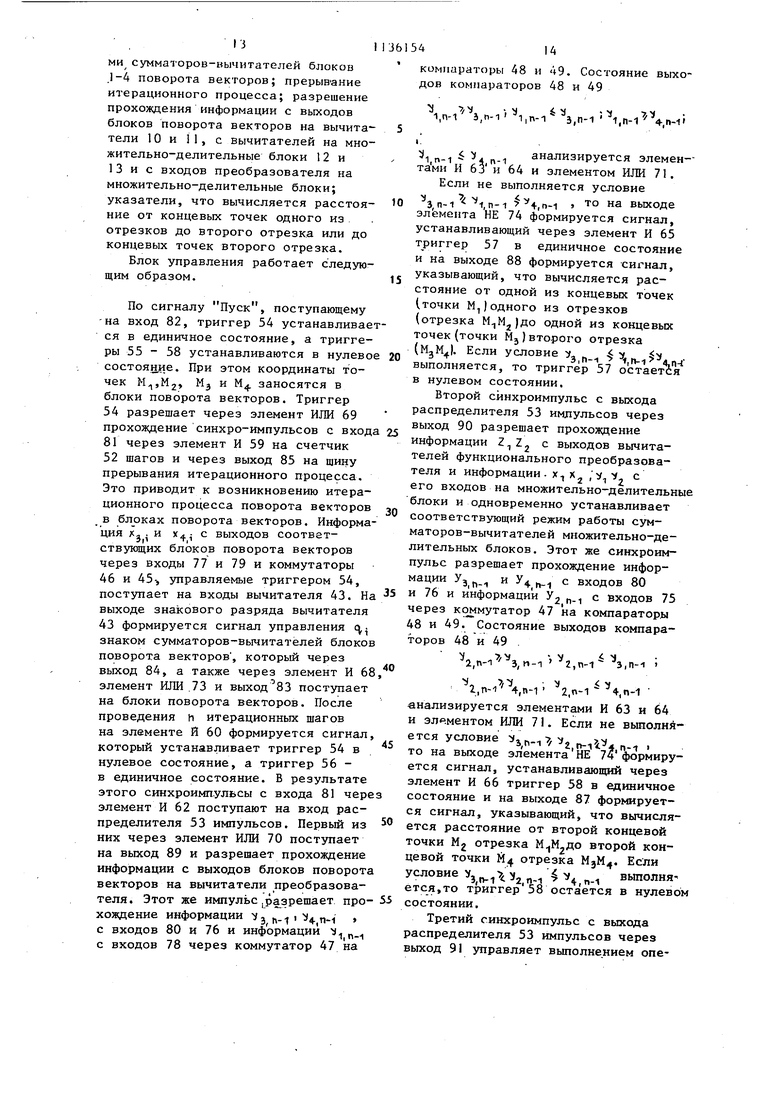

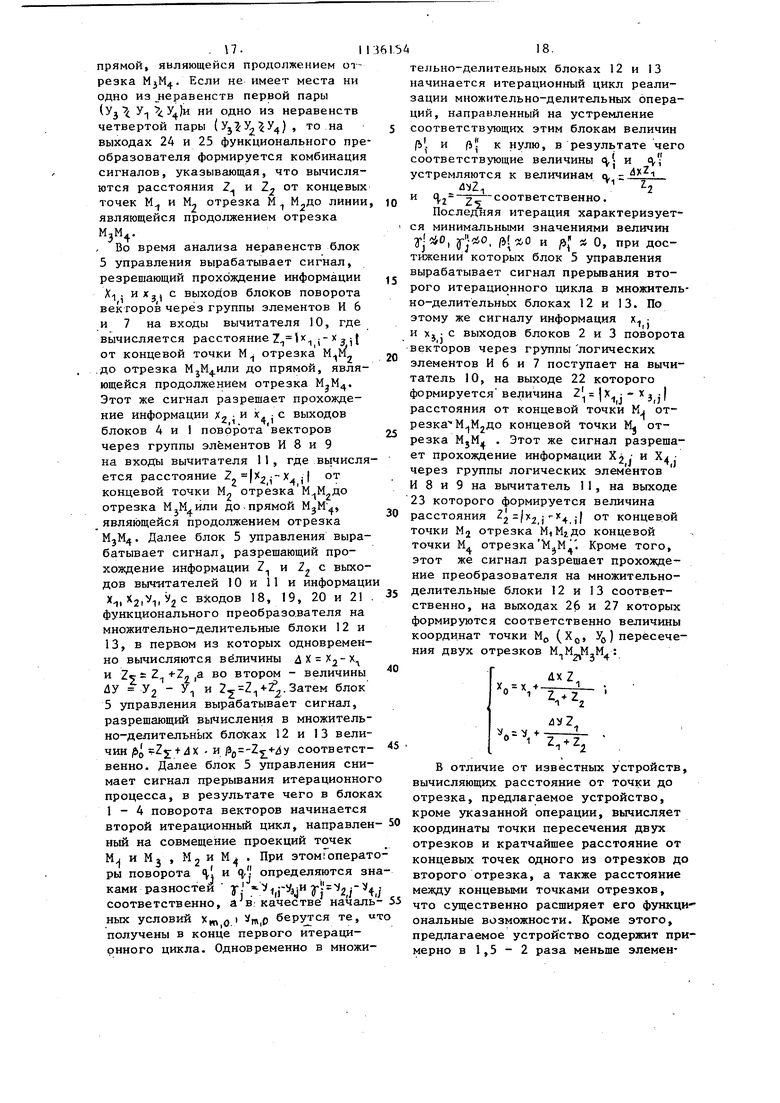

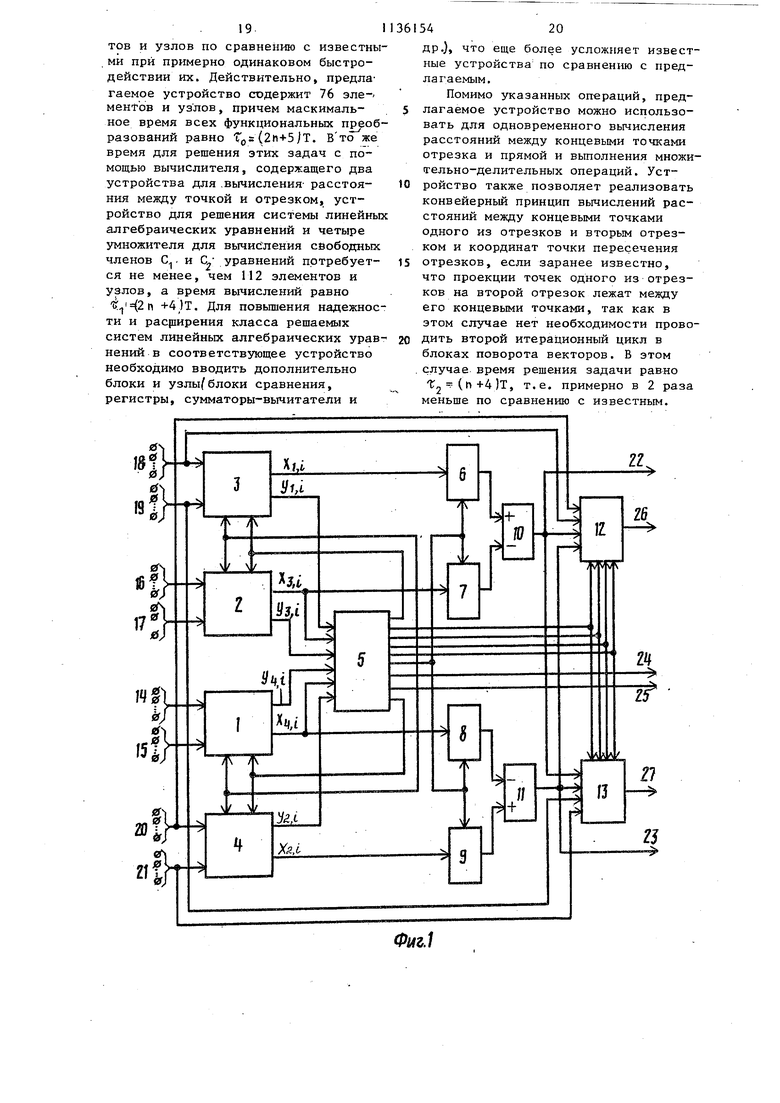

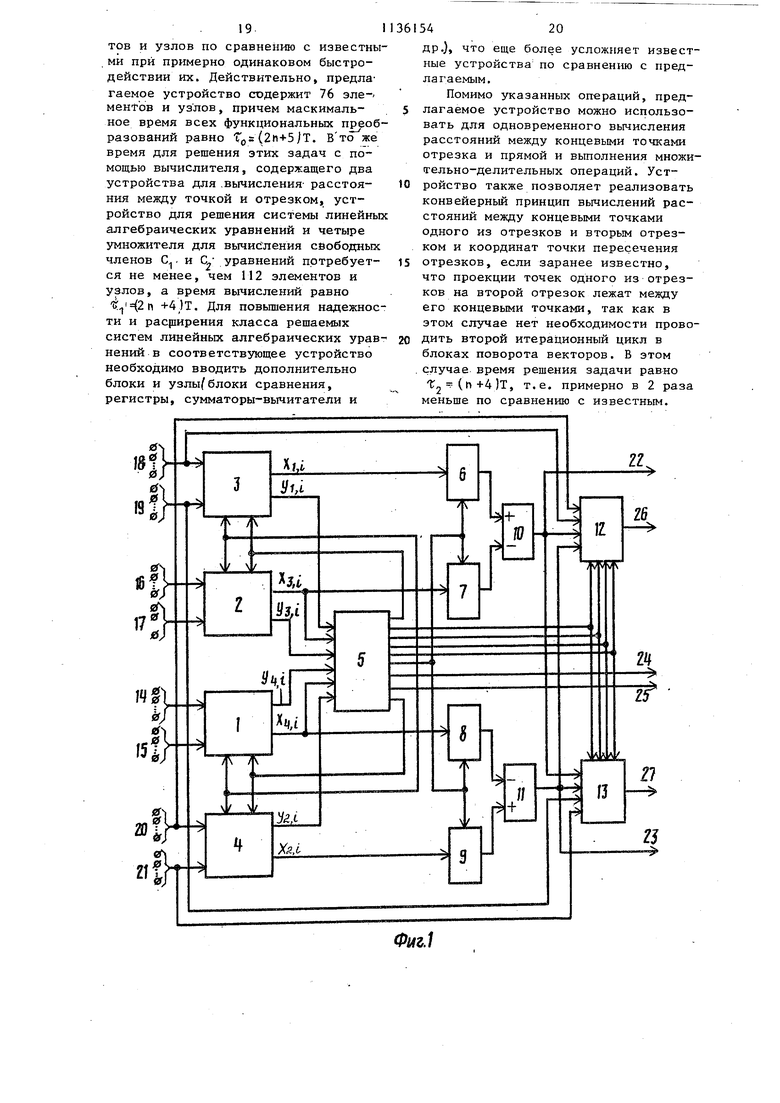

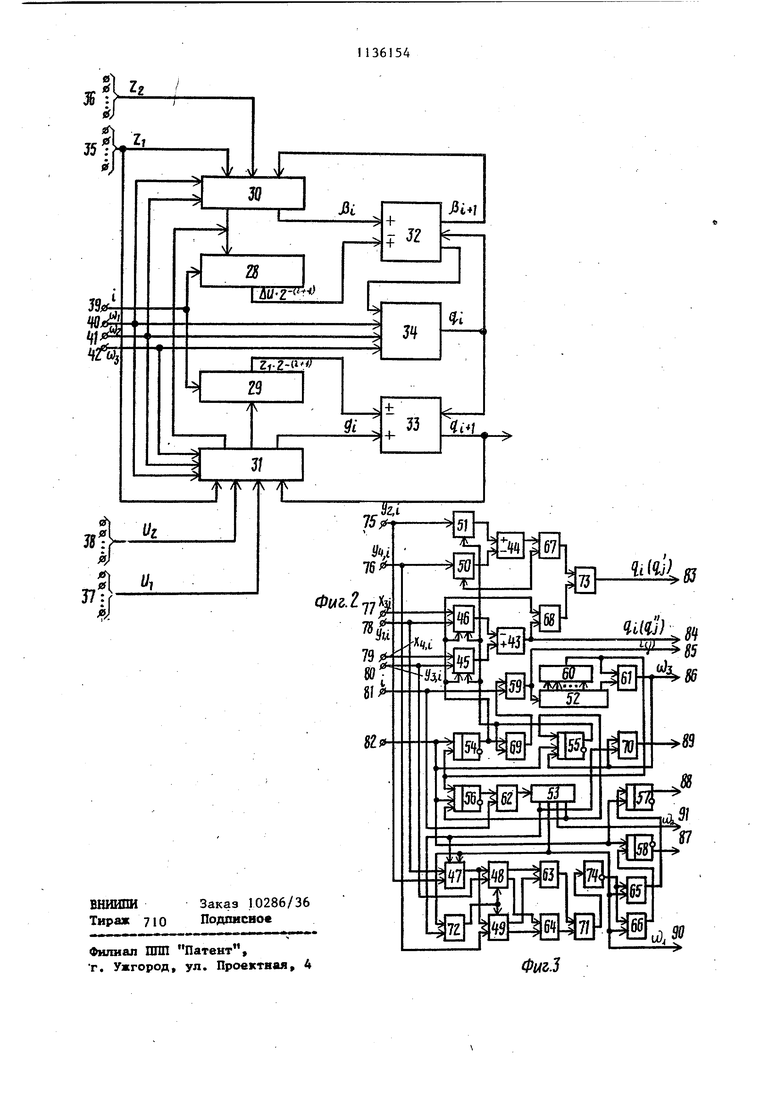

Изобретение относится к цифровой вычислительной технике и может быть использовс1но для аппаратной реализации вычисления координат точки пересечения двух отрезков на плоскости, заданных в декартовой системе 3 координат, и вычисления расстояний от концевых точек одного из отрезко до второго отрезка, а также между концевыми точками отрезков. Известно цифровое устройство для решения системы линейных алгебраических уравнений, содержащие сдвиго вые регистры, одноразрядные суммйторы-вычитатели, реверсивные счетчики, блоки анализа и логические элементы И и ИЛИ. Устройство осуществляет вычисление координат (° о) точки пересечения двух отрезко заданных в декартовой системе координат в йипе системы уравнений: A X-f-B y C 0 -, где А,В, С, (i 1,21 - коэффициент уравнений о резков: А . х+В,., ч-С.0 СП. Однако устройство не обеспечивает вычисления расстояний от концевых точек одного из отрезков до второго отрезками между концевыми точками отрезков, т.е. вычисления функций вида z..4iilii, 1 fTfTif rfTMMv. где j l,2; ,4; kj v. - координат концевых точек отрезка одной из прямых. Известно также цифровое устройст во для вычисления функций вида и --- , содержащее сдвиговые регист ры и сумматоры-вычитатели C2j. Однако это устройство не предназ начено для вычисления координат точ ки пересечения двух отрезков, задан ных в декартовой системе координат и расстояний между концевыми точкам одного из отрезков и вторым отрезком, а также между концевыми точкам отрезков. Наиболее близким к изобретению по технической сущности является функциональный преобразователь для вычисления расстояния на плоскостиот точки до отрезка, заданных в декартовой системе координат, содержащий первый, второй и третий блоки поворота вектора, две Группы элементов 544 И, вычитатель и блок управления, содержащий вычитатель аргумента, счетчик, два триггера, пять элементов И, два коммутатора, два компаратора, три элемента ИЛИ и элемент НЕ, причем первый и второй управляющие входы коммутаторов соединены с выходами первого и второго триггеров соответственно и входами первого элемента ИЛИ, выход которого соединен с первым входом первого элемента И второй вход которого является входом тактовых импульсов преобразователя, выход первого элемента И соединен с входом счетчика, выходы разрядов которого через второй элемент И соединены с управляющим входом первого и второго компараторов, первым входом второго триггера и первым входом третьего элемента И, второй вход которого соединен с выходом переполнения счетчика, выход третьего элемента И соединен с первым входом первого триггера и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента ИЛИ, входы которого соединены с выходами четвертого и пятого элементов И, входы четвертого элемента И соединены с первыми выходами компараторов, входы пятого элемента И соединены с вторыми выходами компараторов, выход третьего элемента ИЛИ через элемент НЕ соединен с вторым входом первого триггера, установочный вход которого соединен с входом пуска преобразователя и установочным входом второго триггера, выходы коммутаторов соединены с входами вычитателя аргументов, причем информационные входы первого, второго и третьего блоков поворота вектора являются соответственно первой, второй и третьей группами входов преобразователя, первая и вторая группы выходов первого блока поворота вектора соединены с входами первого коммутатора, первая и вторая группы вькодов третьего блока поворота вектора соединены с первыми входами первого компаратора и второго коммутатора, вторые входы которых соединены с второй группой выходов второго блока поворота вектора и первыми входами второго компаратора, вторые входы которого соединены с второй группой выходов первого блока поворота вектора, выход первого триггера является выходом преобразователя, выходы первого элемента И и вычитателя аргументов соединены соответственно с первыми и вторыми управляющими входами блоков noBOpot .вектора, выход второго элемента ИЛИ соединен с управляющими входами элементов И первой и второй групп, вторые входы элементов И которых соединены соответственно с вторыми выходами второго и третьего блоков поворота вектора, выходы элементов И первой и второй групп соединены с первыми и вторыми входами вычитателя, выход которого является выходом преобразователя. Каждый блок поворота вектора содержит два коммутатора, два регистра сдвига и два сумматора-вычитател причем первые входы коммутаторов являются информационными входами блока поворота вектора, первый и второй управляющие входы которого соединены соответственно с управляю щими входами регистров сдвига и вхо дами управления режимом сумматороввычитателей, выходы которых являются первой и второй группами блоков поворота вектора и соединены с вторыми входами соответствующих . коммутаторов, выходы которых соеди нены с входами соответствующих регистров сдвига .и первыми входами соответствующих сумматоров-вычитат лей, вторые входы которых соединен с выходами разноименных регистров сдвига З. Однако в известном устройстве отсутствует возможность вычисления координат точки пересечения двух отрезков на плоскости и одновременного вычисления расстояний от концевых точек одного из отрезков до второго отрезка. Цель изобретения - расширение функциональных возможностей путем дополнительного вычисления координ точки пересечения двух отрезков на плоскости и расстояний от конце вых точек одного из отрезков до другого отрезка и между концевыми точками отрезков. Поставленная цель достигается тем, что функциональный преобразователь, содержащий первый, второй и третий блоки поворота вектора, информационные входы которых являю ся соответственно первой, второйи третьей группами входов операндов преобразователя, два элемента И, вычитатель, блок управления, содержащий вычитатель аргумента, счетчик, два триггера, пять элементов И, первый и второй коммутаторы, первый и второй компараторы, первый,- второй и третий элементы ИЛИ и элемент НЕ, дополнительно содержит четвертый блок поворота вектора, третью и четвертую группы элементов И, второй вычитатель, первый и второй множительно-делительные блоки, а в блок управления введены второй вычитатель аргумента,, две группы элементов И, третий коммутатор, три триггера, распределитель импульсов, пять элементов И и два элемента ИЛИ, причем в блоке управления единичный выход первого триггера соединен с первым входом первого .элемента ИЛИ, вторым входом первого элемента И и первыми управляющими входами первого и второго коммутаторов, вторые управляющие входы первого и второго коммутаторов соединены с управлякицими входами элементов И первой и второй групп, единичным выходом третьего триггера, вторым входом десятого элемента И и вторым входом первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с тактовым входом преобразователя и с первым входом третьего элемента И, второй вход которого соединен с единичным выходом четвертого триггера, нулевой вход которого соединен с единичным входом первого, нулевыми входами второго, третьего и пятого триггеров и установочным входом преобразователя, выход третьего элемента И соединен с управляющим входом распределителя импульсов, первый выход которого соединен с первыми входами второго, и третьего элементов ИЛИ и первым управляющим входом третьего коммутатора, второй управляющий вход которого соединён с первыми входами четвертого и пятого элементов И, вторым входом третьего элемента ИЖ и вторым выходом распределителя импульсов. Третий выход которого соединен с единичным входом третьего и нулевым входом четвертого триггеров, нулевой вход первого триггера соединен с единичным входом четвертого триггера, первым входом шестого элемента И ц 71 выходом седьмого элемента И, входы которого соединены с соответствующи ми выходами разрядов счетчика, выход переполнения которого соединен с вт рым входом шестого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ и нулевым входом третьего триггера, выход третье го коммутатора соединен с первыми информационными входами первого и второго компараторов, первые выходы результатов сравнения операндов которых соединены соответственно с первым и вторым входами восьмого элемента И соответственно, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом девятого элемента И, первый и второ входы которого соединены с вторыми выходами результатов сравнения операндов соо-тветственно первого и вто рого компараторов, управляющие вход которых соединены с выходом третьег элемента ИЛИ, выход четвертого элемента ИЛИ соединен через элемент НЕ с вторыми входами четвертого и пятого элементов И, выходы которых соединены с единичными входами второго и пятого триггеров соответстве но, первый и второй входы пятого элемента ИЛИ соединены с выходами первого и десятого элементов И соот ветственно, первые входы которых соединены с выходами.первого и второго вьгчитателей аргумента соответственно, первые входы операндов кот рык соединены с выходом первого коммутатора и выходами элементов И первой группы, вторые входы операндов первого и второго вычитателей аргумента соединены с выходом второ го коммутатора и выходами элементов И второй группы соответственно, выход второго элемента И соединен с управляющим входом счетчика,информа ционный вход четвертого блока пово рота вектора соединен с четвертой группой входов операндов преобразователя , первая группа выходов операндов четвертого блока. поворота вектора соединена с информационными входами элементов И третьей группы, управляющие входы которых соединены с выходом второго элемента ИЛИ блок управления и управляющими входами элементов И четвертой группы преобразователя, информационные входы . (соторых соединены с первой группой 4 выходов операндов блока поворота вектора и первым информационным входом первого коммутатора блока управления, в торой информационньш вход первого коммутатора блока управления соединен с вторым входом первого компаратора блока управления и второй группой выходов операндов второго блока поворота вектора, первая группа выходов операндов которого соединена с первым информационным входом второго коммутатора блока управления и информационными входами элементов И пятой группы, управляющие входы которых соединены с выходом второго элемента ИЖ блока управления и управляющими входами элементов И шестой группы преобразователя, информационные входы которых соединены с первой группой вьпсодов операндов третьего блока поворота- вектора, вторая группа выходов операндов которого соединена с вторым информационным входом второго коммутатора блока управления и первым информационным входом третьего коммутатора, второй информат ционный вход которого соединен с вторыми входами элементов И первой группы и второй группой выходов операндов четвертого блока поворота вектора, вторая группа выходов операндов первого блока поворота вектора соединена с первыми входами элементов И второй группы и вторым информационным входом второго компаратора, выход пятого элемента ИЛИ блока управления соединен с первыми управляющими входами первого и четвертого блоков поворота .вектора, вторые управляющие входы которых соединены с выходом в горого элемента И блока управления, первыми управляющими входами первого и второго множительно-делительных блоков и вторыми управляющими входами второго и третьего блоков поворота вектора преобразователя, первые, управляющие входы которых соединены с выходами первого вьгаитателя.аргумента блока управления, второй выход распределителя импульсов блока управления соединен с вторыми управляющими входами первого и второго множительноделительных блоков, третьи управляющие входы которых соединены с четвертым выходом распределителя импульсов блока управления, выход шестого элемента И блока управления соединен с четвертыми управляющими входами первого и второго множительно-делительных блоков, выходы которых соединены соответственно с пятой и шестой группами выходов преобразователя, выходы элементов И третьей и четвертой групп соединены соответственно с входами первого и второго операндов первого вычитателя, выход которого соединен с второй группой выходов преобразователя и с первыми информационными входами первого и второго множительно-делительных блоков, вторые информационные входы которых соединены с выходом второго вычитателя, входы первого и второго операндов которого соединены с выходами элементов И пятой и шестой групп соответственно, выходы второго вычитателя соединены с первой группой выходов преобразователя, третьи информационные входы первого и второго множительно-делительных блоков соединены с третьей группой входов операндов преобразователя, четвертая группа входов операндов соединена с четвертыми -информационными входами первого и второго множительнр-делительных блоков. При этом каждый множительно-дели.тельный блок содержит первый, второй и третий коммутаторы, первый и второ регистры сдвига, первый и второй сум маторы-вычитатели, причем первый информационный вход первого коммутатор соединен с первым информационным входом второго коммутатора и первым информационным входом множительноделительного: блока, первый управляющий вход которого соединен с управляющими входами п§рвого и второ го регистров сдвига, разрядные вьпсоды которых соединены с первыми входами операндов соответствующих сумматоров-вычитателей,вторые входы операндбв которых соединены с первыми выходами соответствующих коммутаторов, вторые выходы которых соединены с разрядными входами соот ветствующих регистров сдвига, выходы первого и второго сумматоров-вычита телей соединены с вторыми информаци онными входами соответствующих комм таторов, выход знакового разряда первого сумматора-вьтчитателя соединен с управляющим входом третьего коммутатора, выход которого соедине со знаковыми входами первого и второго сумматоров-вычитателей, второй управляющий вход множительно-делительного блока соединен с первым информационным входом третьего коммутатора и первыми управляющими входами первого и второго коммутаторов, вторые управляющие входы которых соединены с третьим управляющим входом множительно-делительного блока и вторым информационным входом третьего коммутатора, третий информационный вход которого соединен с третьим управляющим входом второго коммутатора и четвертым управляющим входом множительно-делительного блока, второй информационный вход которого соединен с третьим информационным входом второго коммутатора, третий информационный выход которого соединен с разрядными входами первого регистра сдвига, третий и четвертый информационные входы множительноделительного блока соединены с третьими и четвертыми информационными входами соответственно первого и второго коммутаторов, информационный выход второго сумматора-вычитателя соединен с выходом множительно-делительного блока. На фиг. 1 представлена блок-схема преобразователя; на фиг. 2 - блоксхема множительно-делительного блока; на фиг. 3 - блок-схема блока управления. Функциональный преобразователь содержит блоки J - 4 поворота векторов, блок 5 управления, группы элементов И 6 - 9, вычитатели 10 и 11, множительно-делительные блоки 12 и 13, информационные группы входов 14-21 преобразователя, выходы 22 - 27 результатов преобразователя. Каждый множительно-делительный блок содержит регистры 28 и 29 сдвига, коммутаторы 30 и 31, сумматорывычитатели 32 и 33, коммутатор 34 режима сумматоров-вычитателей, информационные группы входов 35 - 38, управляющие входы 39-42. Блок 5 управления содержит вычитатели 43 и 44 аргумента, коммутаторы 45 - 47, компараторы 48 и 49, группы элементов И 50 и 51, счетчик 5.2, распределитель 53 импульсов, триггеры 54 - 58, элементы И 59 - 68, элементы ИЛИ 69 - 73, элемент НЕ 74, входы 75 - 82, выходы 83 - 91. Множительно-делительный блок реализует функцию ви,да (У) U..) ГУ 1 Гх -i-V координаты концевых точек M(XT,VI)H М (х V Ьпного из отоез 2 2 и 2,-соотвефственно расстояния от точек М и М2 до прямой Mj М, заданной координата- ми концевых точек Mj{x3,2(5} и М(Х41) второго отрезка; (i,,Z, кооркккаты точки Мц() пересечения отрезков ,и ММ. Множительно-делительный блок работает следующим образом. В первый предварительный такт по сигналу w управления на входе 40 блока аргументы Z и 2л с- входов 35 и 36 заносятся через коммутатор 30 в регистр 28 и сумматор-вычитатель 32 соответствено, а аргументы Uv, и Uj с входов 37 и 38 заносятся через коммутатор 31 в регистр 29 и сумматор - вычитатель 33 соответстве но. По этому же сигналу u) с помощью коммутатора 34 устанавливается режим суммирования в сумматоре-вычи тателе 33, а по заднему фронту сигн ла U) в сумматорах-вычитателях 32 и 33- выполняются соответствующие операции над аргументами 2 к 22 / U, И Uj , ,42, , dU U2U . Во второй предварительный такт по сигналу ujj управления на входе 41 блока содержимое сумматора-вычи тателя 33 передается через коммута тор 31 в регистр 28 и сумматорвычитатель 32. По этому же сигналу ВШЧИЮ 1 CJiu j. . ,..j W, с ПОМОЩЬЮ коммутатора 34 устана ливается режим вычитания в суммато ре-вычитателе 32, а содержимое сумматора-вычитателя 32 передается через коммутатор 30 на его входы. Далее по заднему фронту сигнала CAJJ управления в сумматоре-вычитателе 32 вычисляется величина ji --1.5;-ьди ;С предварительной передачей величи через коммутатор 30 в регистр 28 После завершения второго предва рительного такта информация в реги рах 28 и 29 сдвигается в сторону 1 4 младших разрядов -по тактовым импульсам, поступающим поуправляющему входу 39 прерывания итерационного, процесса из блока 5 управления. При этом схема сдвига содержимого регистров 28 и 29 обеспечивает организацию однотактного одноразрядного сдвига в соответствии с номером итерационного шага (,2,..., п) f образования очередных приращений величин 2, и 4U2-( . Сдвинутая информация из регистров 28 и 29поступает соответственно на сумматоры-вычитатели 32 и 33, где производится ее суммирование или вычитание с предыдущим результатом. Знаком сумматоров-вычитателей управляет коммутатор 34 выбора режима сумматоров-вычитателей по входу знакового разряда сумматора-вычитателя 32. Результаты с сумматоров-вычитателей 32 и 33 заносятся через коммутаторы 30и 31 в сумматоры-вычитатели 32 и 33. Кроме того, результат с сумматора- вычитателя 33 поступает на выход множительно-делительного блока. Итерационный процесс прерывается при отсутствии тактовых импульсов на входе 39. Таким образом, в итерационном режиме работы множительно-делительный блок реализует алгоритм С 21: U-i . i где r-i-1 , ft-7,0 -1, /з, -, /5o i ) , . . , Последняя итерация характеризуетминимальным значением /3, «О . При этом значение . После проведения п итерационных щагов аргумент U, по сигналу ы л о -эамг управления на входе 42 блока заносится через коммутатор 31 в регистр 29. При этом с помощью коммутатора 34 в сумматоре-вычитателе 33 устанавливается режим суммирования. По заднему фронту сигнала Ыд в сумматоревычитателе 33 производится окончательное вычисление функции f и )2i ., i Z,Z2 Блок 5 управления вырабатывает следующие сигналы: управление знаками сумматоров-вычитателей блоков ,1-4 поворота векторов; прерывание итерационного процесса; разрешение прохождения информации с выходов блоков поворота векторов на вычита тели 10 и 11, с вычитателей на множительно-делительные блоки 12 и 13 и с входов преобразователя на множительно-делительные блоки; указатели, что вычисляется расстоявне от концевых точек одного из отрезков до второго отрезка или до концевых точек второго отрезка.

Блок управления работает следующим образом.

По сигналу Пуск, поступающему -на вход 82, триггер 54 устанавливается в единичное состояние, а триггеры 55 - 58 устанавливаются в нулевое состояние. При этом координаты точек М,М2, Мз и М. заносятся в блоки поворота векторов. Триггер 54 разрешает через элемент ИЛИ 69 прохождение синхро-импульсов с входа 81 через элемент И 59 на счетчик 52 шагов и через выход 85 на щину прерывания итерационного процесса. Это приводит к возникновению итерационного процесса поворота векторов в блоках поворота векторов. Информация и выходов соответствующих блоков поворота векторов через входы 77 и 79 и коммутаторы 46 и 45 управляемые триггером 54, поступает на входы вычитателя 43. На выходе знакового разряда вычитателя 43 формируется сигнал управления с знаком сумматоров-вычитателей блоков поворота векторов , который через выход 84, а также через элемент И 68 элемент ИЛИ .73 и выход ВЗ поступает на блоки поворота векторов. После проведения h итерационных шагов на элементе И 60 формируется сигнал, который устанавливает триггер 54 в нулевое состояние, а триггер 56 в единичное состояние. В результате этого синхроимпульсы с входа 81 чере элемент И 62 поступают на вход распределителя 53 импульсов. Первый из них через элемент ИЛИ 70 поступает на выход 89 и разрешает прохождение информации с выходов блоков поворота векторов на вычитатели преобразователя. Этот же импульс|разрешает прохождение информации Vj „. i -.n-i с входов 80 и 76 и информации а. с входов 78 через коммутатор 47 на

компараторы 48 и 49. Состояние выходов компараторов 48 и 49

,n-i,n-i ,n-n ,п-1 ,n-l n-.i

I.

-1 п-1 - 4 п-1 анализируется элементами И 63 и 64 и элементом ИЛИ 71. Если не выполняется условие

3,n-i -(,п-1 4, ГО «а выходе элЬмеита НЕ 74 формируется сигнал, устанавливающий через элемент И 65 триггер 57 в единичное состояние и на выходе 88 формируется сигнал, указывающий, что вычисляется расстояние от одной из концевых точек (точки М)одного из отрезков (отрезка )до одной из концевых точек (точки Mj)второго отрезка (. Если условие v,., ,,,1 „чвыполняется, то триггер 57 остается в нулевом состоянии.

Второй синхроимпульс с выхода распределителя 53 имлульсов через выход 90 разрешает прохождение информации с выходов вычитателей функционального преобразователя и информации. XT Х- ,v, V- с его входов на множительно-делительны блоки и одновременно устанавливает соответствующий режим работы сумматоров-вычитателей множительно-делительных блоков. Этот же синхроимпульс разрешает прохождение информации УЗ,. и У4,1 с входов 80 и 76 и информации УЗ f,-i входов 75 через коммутатор 47 на компараторы 48 и 49. Состояние выходов компараторов 48 и 49 .

2,п--| 3, м-1 z,n-i з,п-1 ;

-У f l,n-i 4,n-l 2,n-1 4,n-1

анализируется элементами И 63 и 64 и элементом ИЛИ 71. Если не выполнйется условие ,., 7, v . , то на выходе элемента НЕ 74 формируется сигнал, устанавливающий через элемент И 66 триггер 58 в единичное состояние и на выходе 87 формируется сигнал, указывающий, что вычисляется расстояние от второй концевой точки Mg отрезка второй концевой точки М отрезка MjM. Если

условие 4,п-1 вьшолня ется,то триггер 58 остается в нулево состоянии.

Третий синхроимпульс с выхода распределителя 53 импульсов через выход 91 управляет выполнением one15, рации вычитания величины - из величины л и в множительно-делитель ных блоках преобразователя. Четвертый синхроимпульс с выхода распределителя 53 импульсов устанав ливает триггер 55 в единичное состояние, а триггер 56 в нулевое состояние. При этом через элемент ИЛИ 69 .открьшается элемент И 59 и начинается второй итерационный процесс в блоках поворота векторов и итерационный процесс в множительноделительных блоках.. Информация ii э выходов соответст ву1ощихблоков поворота векторов через входы 78 и 80 и коммутаторы 46 и 45 поступает на входы вычислителя 43, где формируется сигнал управления знаком сумматоров-вычита телей соответствующих блоков поворо та векторов. Одновременно информа; ция У 1 4 )с выходов соответствующих блоков поворота векторо через входы 75 и 76 и группы элемен тов И 51 и.50 поступает на входы вычитателя 44, где формируется сигHaji q/j управления знаком сумматоров вычитателей соответствующих блоков поворота векторов, который через элемент И 67 и элемент ИЛИ 73 поступает на выход 83. Второй итерационный процесс зака чивается после того, как в счетчике 52 зафиксировано число 2п итерационных шагов. При этом на выходе эле мента И 61 формируется сигнал, разрешающий прохождение информации Xi, Yiс входов функционального преобразователя на множительно-делител ные блоки и устанавливающий режим суммирования сумматоров-вычитателей множительно-делительных блоков. Это же сигнал через элемент ИЛИ 70 разрешает прохождение информации на входы вычитателей функционального п образователя и устанавливает в нулевое состояние триггер 55. Функциональный преобразователь работает следующим образом. Координаты концевых точек М 1,, (Х , У) и (У) первого отрезк поступают через входы 18 - 21 в блоки 3 и 4 поворота векторов соответственно, а координаты концевых точек MjlXjYjJH М ) поступают через входы 16,17,14 и 15 в блоки 2 и 1 поворота векторов соответственно. В блоках 1 -.4 поворота вект ров производится итерационный процесс одновременного .поворота векторов OFf;;, , оТГз и ОЙ на угол Ч, определяемый равенством проекций точек Mj и М на одну из осей координат (например, на ось ОХ|по алгоритму Волдера:.. . х - х - - m,,i m,i+i у 41 Я, ) 1 tn,i+i m.i 1 m,i , , ..,; Ti ,.; , , i 0,n-- , Последняя итерация, характеризуется минимальным значением , при достижении которого блок 5 управления вырабатывает сигнал прерывания процесса поворота векторов. При этом взаимное расположение проекций всех четырех точек М, М М, и М,на ось ОУ определяется парой из двенадцати возможных неравенств: УЗ У1 У4; У1 У4 УЗ ; У, УЗ У4 ; 4 2 УЭ 4 У2 У4 УзУЗ У Эти неравенства анализируются в блоке 5 управления. Если имеет место одного из неравенств первой пары (УЗ УТ У4) и одно из неравенств четвертой пары (УЗ У2- У4 J выходах 24 и 25 функционального преобразователя присутствует комбинация сигналов, указьшающая, что после окон- чания первого итерационного цикла вычисляются расстояния Z и концевых точек М и М, отрезка М.М до отрезка М-М.. Если имеет место одно из неравенств первой пары () и одно из неравенств либо пятой пары (Уг У %; Уо ) либо шестой пары{3 УДУ2/ , то на выходах 24 и 25 функционального преобразователя формируется комбинация сигналов, указывающая, что вычисляется расстояние Z от концевой точки М отрезка ММ до отрезка и расстояние Z от концевой точки М отрезка М.М до прямой, являющейся продолжением отрезка . Если имеет место одно из неравенств четвертой пары ( : i) и одно из неравенств либо второй пары , ( V4 зЬ .либо третьей пары (УТ УЗ 4 выходах 24 и 25 функционального преобразователя формируется комбинация сигналов, указывающая, что вычисляется расстояние Z от концевой точки М отрезка М.М до отрезка Mj М и расстояние Н, от концевой точки М отрезка прямой, являющейся продолжением отрезка МзМ. Если не имеет места ни одно из jiepaseHCTB первой пары (YJ( У Х(.)и ни одно из неравенств четвертой пары ( то на выходах 24 и 25 функционального пре образователя формируется комбинация сигналов, указывающая, что вычисляются расстояния 2 и 2 от концевых точек М и М- отрезка М М-ДО линии являющейся продолжением отрезка . Во время анализа неравенств блок 5 управления вырабатывает сигнал, резрешающий прохождение информации Х . и X J с выходов блоков поворота векторов через группы элементов И 6 и 7 на входы вычитателя 10, где вычисляется расстояниеZ l (зт от концевой точки М отрезка .до отрезка М2МфИли до прямой, являющейся продолжением отрезка MjM. Этот же сигнал разрешает прохождение информации Xg и Jfi j с выходов блоков 4 и поворота векторов через группы элементов И 8 и 9 на входы вычитателя 11, где вычисля ется расстояние j l i ° концевой точки Mg отрезкаM..M2ДO отрезка М,М.или до-прямой , являющейся продолжением отрезка MjM. Далее блок 5 управления вырабатывает сигнал, разрешающий прохождение информации Z и 2 с выходов выч-итателей 10 и 11 и информаци Xii2i i.2 входов 18, 19, 20 и 21 функционального преобразователя на множительно-делительные блоки 12 и 13, в перном из которых одновременно вычисляются величины ДХ Х2-Х и Z - Z -е2, ,а во втором - величины 4У у2 - У и . Затем блок 5 управления вырабатывает сигнал, разрешающий вычисления в множительно-делительных блохах 12 и 13 вепкчин JX - соответственно. Далее блок 5 управления снимает сигнал прерывания итерационног процесса, в результате чего в блока 1-4 поворота векторов начинается второй итерационный цикл, направлен ный на совмещение проекций точек М иМ , MjHM . При этомГоперат ры поворота «Vj -j определяются зн ками разностей -у i, 2,f соответственно, а в. качестве началь ных условий Х,,п,о. п,Р берутся те, « получены в конце первого итерационного цикла. Одновременно в множи 11 18. тельно-делительных блоках 12 и 13 начинается итерационный цикл реализации множительно-делительных операций, направленный на устремление соответствующих этим блокам величин /ь1 и fij к нулю, в результате чего соответствующие величины и е, устремляются к величинам о, -. и 2- 2 °°1ветственно. Последняя итерация характеризуется минимальными значениями величин TJ, (Гу. и и О, при достижении которых блок 5 управления вырабатывает сигнал прерывания второго итерационного цикла в множительно-делительных блоках 12 и 13. По этому же сигналу информация х и Xj с выходов блоков 2 и 3 поворота векторов через группы логических элементов И 6 и 7 поступает на вычитатель 10, на выходе 22 которого формируется величина Z | х j - х j . | расстояния от концевой точки К. отрезка концевой точки М отрезка MjM . Этот же сигнал разрешает прохождение информации Xjу и через группы логических элементов И 8 и 9 на вычитатель 11, на выходе 23 которого формируется величина 2,i ч,; от концевой расстояния точки Mj отрезка М,МгДо концевой точки М отрезка jM. Кроме того, этот же сигнал разрешает прохождение преобразователя на множительноделительные блоки 12 и 13 соответственно, на выходах 26 и 27 которых формируются соответственно величины координат точки MO (Х, У ) пересечения двух отрезков M-MJi.M.: л о Z,.2, . В отличие от известных устройств, вычисляющих расстояние от точки до отрезка, предлагаемое устройство, кроме указанной операции, вычисляет координаты точки пересечения двух отрезков и кратчайшее расстояние от концевых точек одного из отрезков до второго отрезка, а также расстояние между концевыми точками отрезков, что существенно расширяет его функциональные возможности. Кроме этого, предлагаемое устройство содержит примерно в 1,5-2 раза меньше элемен19

трв и узлов по сравнению с известны.мй при примерно одинаковом быстродействии их. Действительно, предлагаемое устройство содержит 76 эле-ментов и узлов, причем маскимальное время всех функциональных преобразований равно T(5s(2n+5JT. время для решения этих задач с по мощью вычислителя, содержащего два устройства для .вычисления- расстояния между точкой и отрезком, устройство для решения системы линейных алгебраических уравнений и четыре умножителя для вычисления сеободных членов С, и уравнений потребуется не менее, чем 112 элементов и узлов, а время вычислений равно . Для повьшения надежности и расщирения класса решаемых систем линейных алгебраических уравнений в соответствующее устройство необходимо вводить дополнительно блоки и узлы блоки сравнения, регистры, сумматоры-вычитатели и

15420

др.), что еще более усложняет известные устройства по сравнению с предлагаемым.

Помимо указанных операций, предлагаемое устройство можно использовать для одновременного вычисления расстояний между концевыми точками отрезка и прямой и выполнения множительно-делительных операций. Устройство также позволяет реализовать конвейерный принцип вычислений расстояний между концевыми точками одного из отрезков и вторым отрезком и координат точки пересечения отрезков, если заранее известно, что проекции точек одного из отрезков на второй отрезок лежат меязду его концевыми точками, так как в этом случае нет необходимости проводить второй итерационный цикл в блоках поворота векторов. В этом случае время решения задачи равно (, т.е. примерно в 2 раза меньше по сравнению с известным.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1975 |

|

SU543943A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппаратные методы в цифровой вычислительной технике, Минск, изд-во БГУ им | |||

| В.И.Ленина, 1977, с | |||

| Способ получения кодеина | 1922 |

|

SU178A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1985-01-23—Публикация

1983-06-17—Подача