Изобретение относится к вычислительной технике и может быть использовано в микропрограммных устройствах управления.

Известно запоминающее устройство микрокоманд, содержащее накопитель микрокоманд, коммутаторы, дешифратор фаз операций, формирователь адреса, счетчик фаз операций и накопитель защиты фазы операции 1.

Недостатком устройства является то, что быстродействие его работы также определяется временем обращения к накопителю за выбором микрокоманд для выполняемой операции, что не позволяет использовать его в составе быст родействукхдих ЦВМ.

Наиболее близким по технической сущности к предлагаемому является запоминакхцее устройство микрокоманд, которое содержит накопитель, адресные шины которого связаны через дешифратор операций и регистр операций формирователя адреса с первыми входа-. ми запоминающего устройства микрокоманд, первые выходы накопителя соединены с соответствующими входами к-групп коммутаторов, вторые выходы которюго соединены через дешифратор фаз с управляющими входами к-групп

ксяимутаторов, выходы которого являются выходами запоминакадего устройства микрокоманд 2.

Быстродействие работы этого устройства ограничиваете временем обращения к накопителю за последовательным выбором всех микрокоманд для выполняемой операции, что не позволяет испрльзовать его в быстродействующих сие-;

10 темах, в которых быстродейс вие определяется временем передачи информации через базовые логические эл ементы И, ИЛИ и,НЕ.

Цель изобретения - повышение быст

15 родействня работу устройс.тва. , :

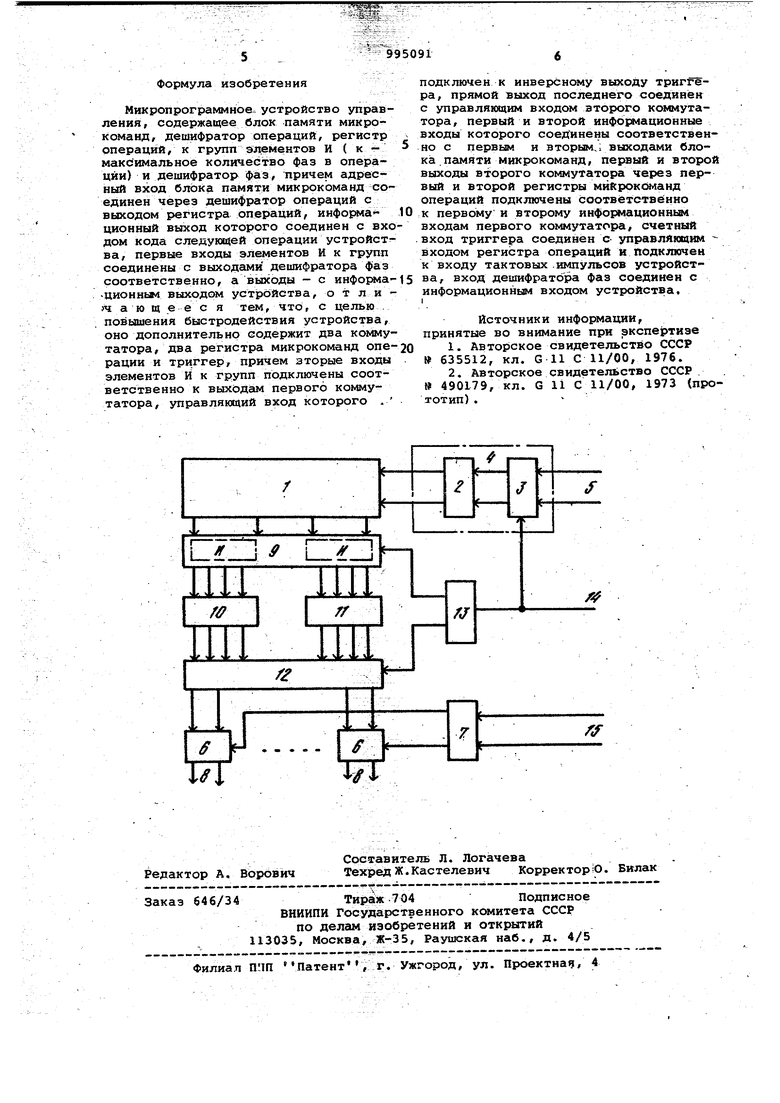

Поставленная цель достигается тем, что микропрограммное устройство управления, содержащее блок памяти микрокоманд, дешифратор операций, ре20гистр операций, к-групп элементов И (к - максимальное количество фаз в операции) и дешифратор фаз, причем а; ресный вход блока памяти микрокоманд соединен через дешифратор операций с

25 выходом регистра операций, информационный вход которого соединен с входом кода следукадей операции устройства, первые входы элементов И к групп соединены с выходакц дешифратора фаз

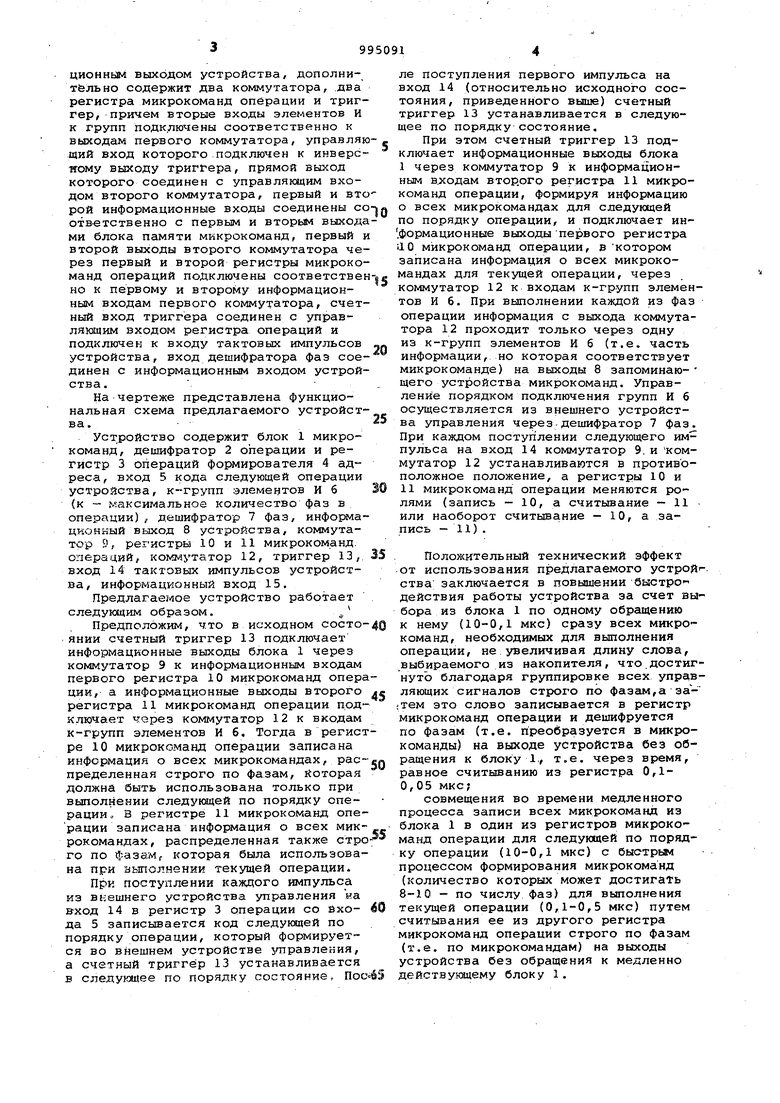

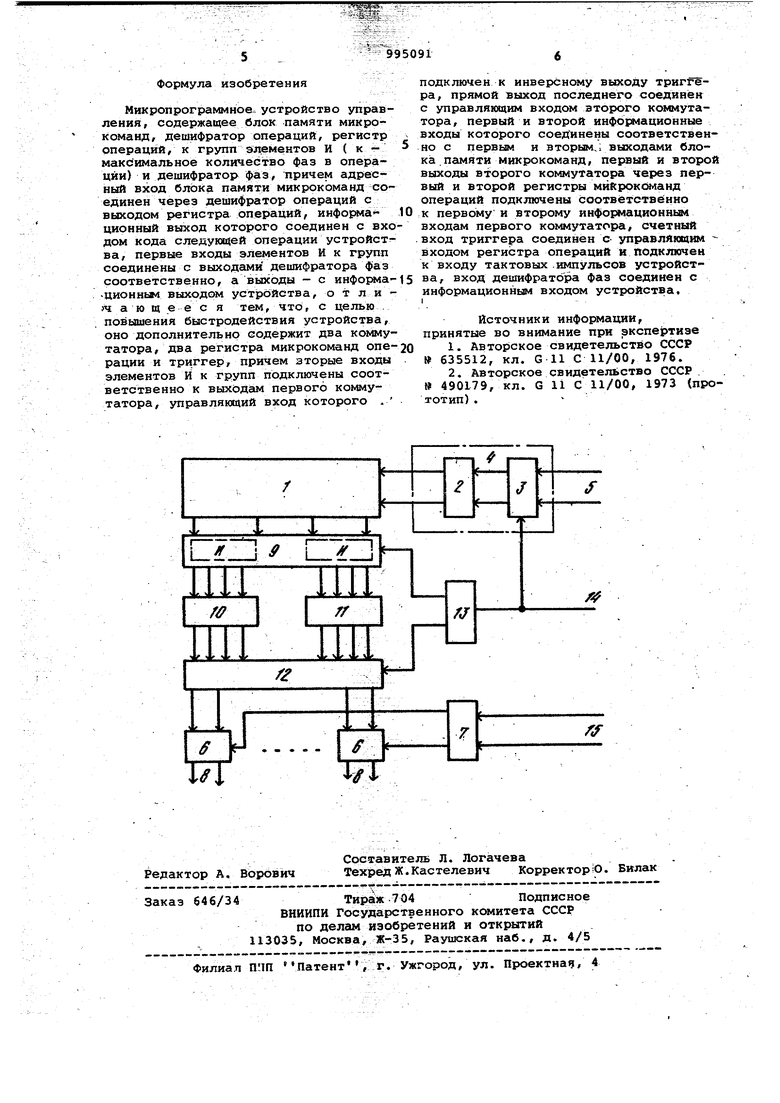

30 соответственно, а выходы - с информационньам выходом устройства, дополнительно содержит два коммутатора, .два регистра микрокоманд операции и триг гер, причем вторые входы элементов И к групп подключены соответственно к выходам первого коммутатора, управля щий вход которого подключен к инверс ному выходу триггера, прямой выход которого соединен с управляющим входом второго коммутатора, первый и вт рой информационные входы соединены c отв-етственно с первым и вторым выход ми блока памяти микрокоманд, первый второй выходы второго коммутатора че рез первый и второй регистры микроко манд операций подключены соответстве но к первому и второму информационным входам первого коммутатора, счет ный вход триггера соединен с управля ацим входом регистра операций и подключен к входу тактовьлх импульсов устройства, вход дешифратора фаз сое динен с информационным входом устрой ства. На чертеже представлена функциональная схема предлагаемого устройст ва. Уст ройство содержит блок 1 микрокоманд, дешифратор 2 операции и регистр 3 операций формирователя 4 адреса, вход 5 кода следующей операции устройства, к-групп элементов И б {к -- максимальное количество фаз в операции), дешифратор 7 фаз, информа ционный выход 8 устройства, коммутатор 9, регистры 10 и 11 микрокоманд. операций, коммутггтор 12, триггер 13, вход 14 тактовых импульсов устройства, информационный вход 15. Предлагаемое устройство работает следукяцим образом. Предположим, что в исходном состоянии счетный триггер 13 подключает информационные выходы блока 1 через коммутатор 9 к информационным входам первого регистра 10 микрокоманд опера ции, а информационные выходы второго регистра 11 микрокоманд операции подключает через коммутатор 12 к входам к-групп элементов И б. Тогда в регист ре 10 микрокоманд операции записана информация о всех микрокомандах, распределенная строго по фазам, Которая должна быть использована только при выполнении следукадей по порядку операции,, В регистре 11 микрокоманд операции записана информация о всех микрокомандах, распределенная также стро го по фазаМг которая была использована при выполнении текущей операции. При поступлении каждого импульса из внешнего устройства управления иа вход 14 в регистр 3 операции со Входа 5 записывается код следующей по порядку операции, который формируется во внешнем устройстве травления, а счетный триггер 13 устанавливается в следуищее по порядку состояние, Пос ле поступления первого импульса на вход 14 (относительно исходного состояния, приведенного выше) счетный триггер 13 устанавливается в следующее по порядку состояние. При этом счетный триггер 13 подключает информационные выходы блока Iчерез коммутатор 9 к информационным в.ходам втор.ого регистра 11 микрокоманд операции, формируя информацию о всех микрокомандах для следующей по порядку операции, и подключает ин.формационные выходы первого регистра ilO микрокоманд операции, в котором записана информация о всех микрокомандах для текущей операции, через коммутатор 12 к входам к-групп элементов И 6. При выполнении каждой из фаз операции информация с выхода коммутатора 12 проходит только через одну из к-групп элементов и 6 (т.е. часть информации, но которая соответствует микрокоманде) на выходы 8 запоминаю- щего устройства микрокоманд. Управление порядком подключения групп И 6 осуществляется из внешнего устройства управления через-дешифратор 7 фаз. При каждом поступлении следующего импульса на вход 14 коммутатор 9. и коммутатор 12 устанавливаются в противоположное положение, а регистры 10 и IIмикрокоманд операции меняются ролями (запись - 10, а считывание - 11 или наоборот считывание - 10, а запись - 11) . Положительный технический эффект от использования предлагаемого устройства; заключается в повышении быстро действия работы устройства за счет выбора из блока 1 по одному обращению к нему (10-0,1 мкс) сразу всех микро команд, необходимых для выполнения операции, не увеличивая длину слова, выбираемого из накопителя, что.достигнуто благодаря группировке всех управляющих сигналов строго по фазам,а затем это слово записывается в регистр микрокоманд операции и дешифруется по фазам (т.е. преобразуется в микрокоманды) на выходе устройства без обращения к блоку 1., т.е. через время, равное считыванию из регистра 0,10,05 мкс; совмещения во времени медленного процесса записи всех микрокоманд из блока 1 в один из регистров микрокоманд операции для следующей по порядку операции (10-0,1 мкс) с быстрым процессом формирования микрокоманд (количество которых может достигать 8-10 - по числу фаз) для выполнения текущей операции (0,1-0,5 мкс) путем считывания ее из другого регистра микрокоманд операции строго по фазам (т.е. по микрокомандам) на выходы устройства без обращения к медленно действуквдему блоку 1.

Формула изобретения

Микропрограммное, устройство управления, содержащее блок памяти микрокоманд, дешифратор операций, регистр операций, к групп элементов И ( к максимальное количество фаз в операции) и дешифратор фаз, причем адресный вход блока памяти микрокоманд соединен через дешифратор операций с выходом регистра операций, инфор«1ационный выход которого соединен с входом кода следующей операции устройст:ва, первые входы элементов И к групп соединены с выходами дешифратора фаз соответственно, а выходы - с информа-ционньм выходом уст ройства, о т л и J4 а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно дополнительно содержит два коммутатора, два регистра микрокоманд oneрации и триггер, причем вторые входы элементов И к групп подключены соответственно к выходам первого коммутатора, управляющий вход которого .

подключен к инверсному выходу триггера, прямой выход последнего соединён с управляющим входом второго коммутатора, первый и второй информационные входы которого соединены соответственно с первым и вторым.; выходами блока .памяти микрокоманд, первый и второ выходы второго коммутатора через первый и второй регистры мйкрокс 1анд операций подключены соответственно к первому и второму информационным входам первого коммутатора счетный вход триггера соединен с управляющим входом регистра операций и подключен к входу тактовых .импульсов устройства, вход дешифратора фаз соединен с

информационным входом устройства,

I.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 635512, кл. G 11 С 11/00, 1976.

2,Авторское свидетельство СССР

490179, кл. G 11 С 11/00, 1973 (пртотип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU987623A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство управления | 1978 |

|

SU742937A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| Микропрограммное устройство управления | 1977 |

|

SU746516A1 |

| Устройство для группового управления лифтами | 1982 |

|

SU1089024A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

Авторы

Даты

1983-02-07—Публикация

1981-09-09—Подача