Изобретение относится к вычислительной технике, в частности к системам программного контроля.

Известно устройство для отыскания неисправностей, на вход испытуемого изделия подается так назьшаемый счетно-диагностический тест, а выходная .реакция, являющаяся функцией данного теста, фиксируется на сдвиговом регистре 1 .

Недостатком этого устройства является то, что оно предназначено для контроля узкого круга типа узлов, так как они не обеспечивают сопряжения с узлами, имеющими различную природу входных сигналов.

Наиболее близким к предлагаемому по технической сущности является устройство для контроля логических узлов, содержащее адресный коммутатор, выход которого подключен к входу блока анализа, неисправностей, блок оперативной памяти, выходы которого подключены к блоку управления, блоку генерации стимулирующих воздействий и блоку анализа, неисправностей, блок управления, а также блок памяти неисправностей, соединенный входом с блоком выявления неисправностей, а выходом - с входом блока анализа неисправностей.

Генератор чисел вырабатывает серию кодовых комбинаций, которые посыпает через блок коммутации стимулирующих воздействий на объект проверки, при этом обеспечивается проверка на рабочей частоте объекта проверки независимо ОТбыстродействия оперативной i, памяти. Кодовые комбинации реакции объекта проверки накапливаются в блоке выявления неисправностей, в котором происходит сравнение по окончании работы генератора чисел накопленной

I информации с эта лонной. При совпадении накопленной и эталонной информации блок оперативной памяти задает следующий порядок следов.ания воздействий, генератору чисел 2 .

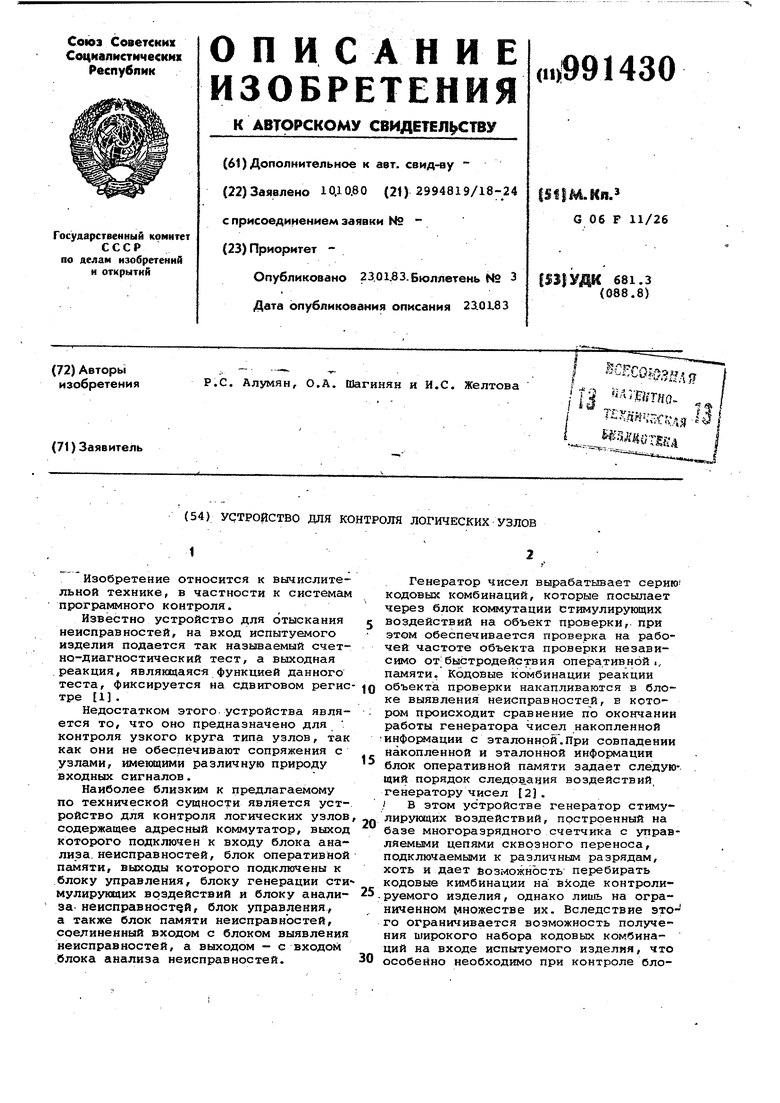

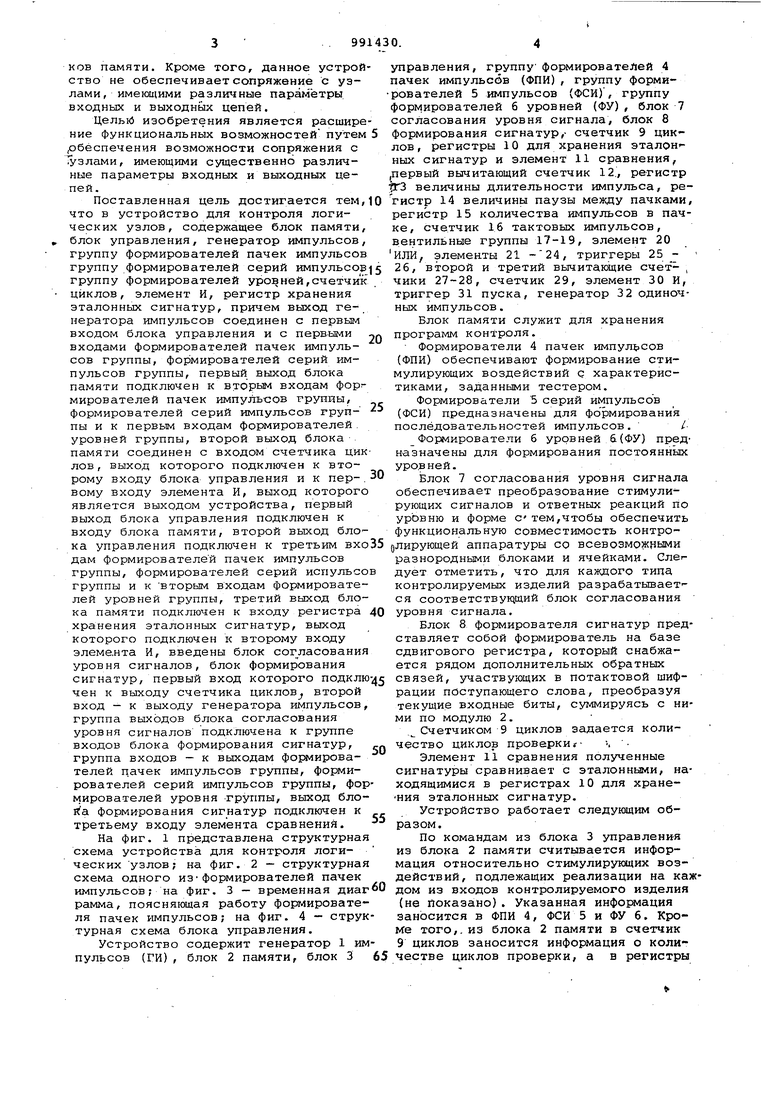

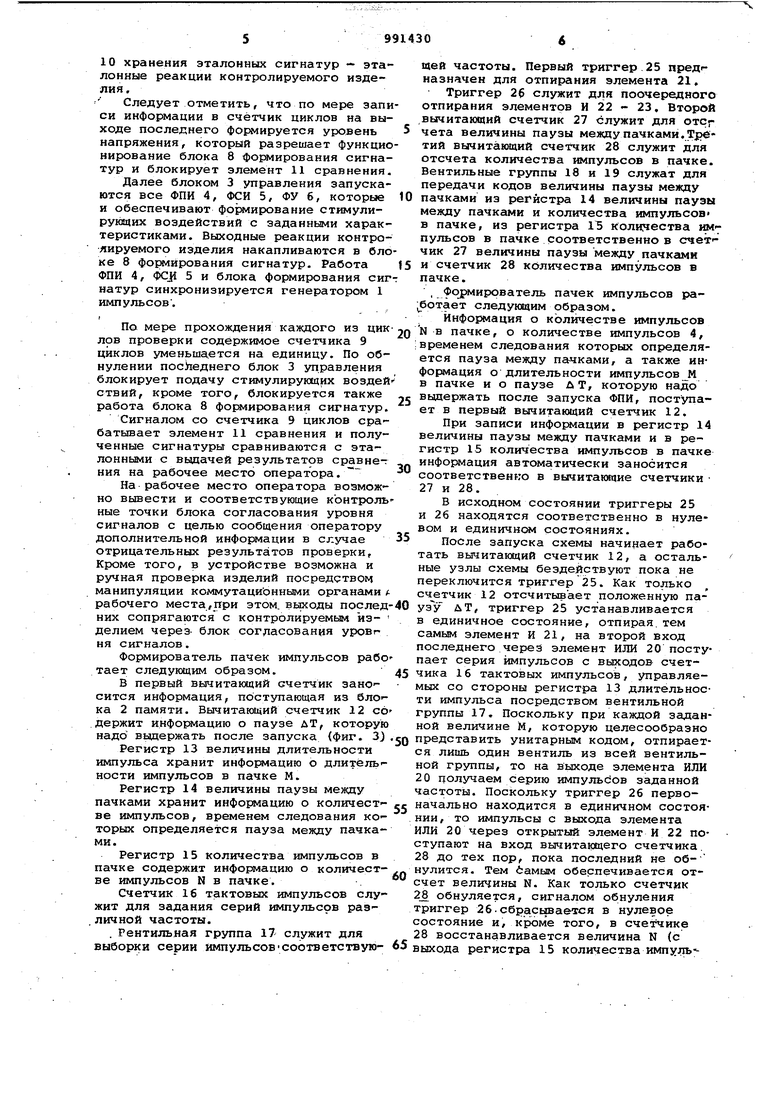

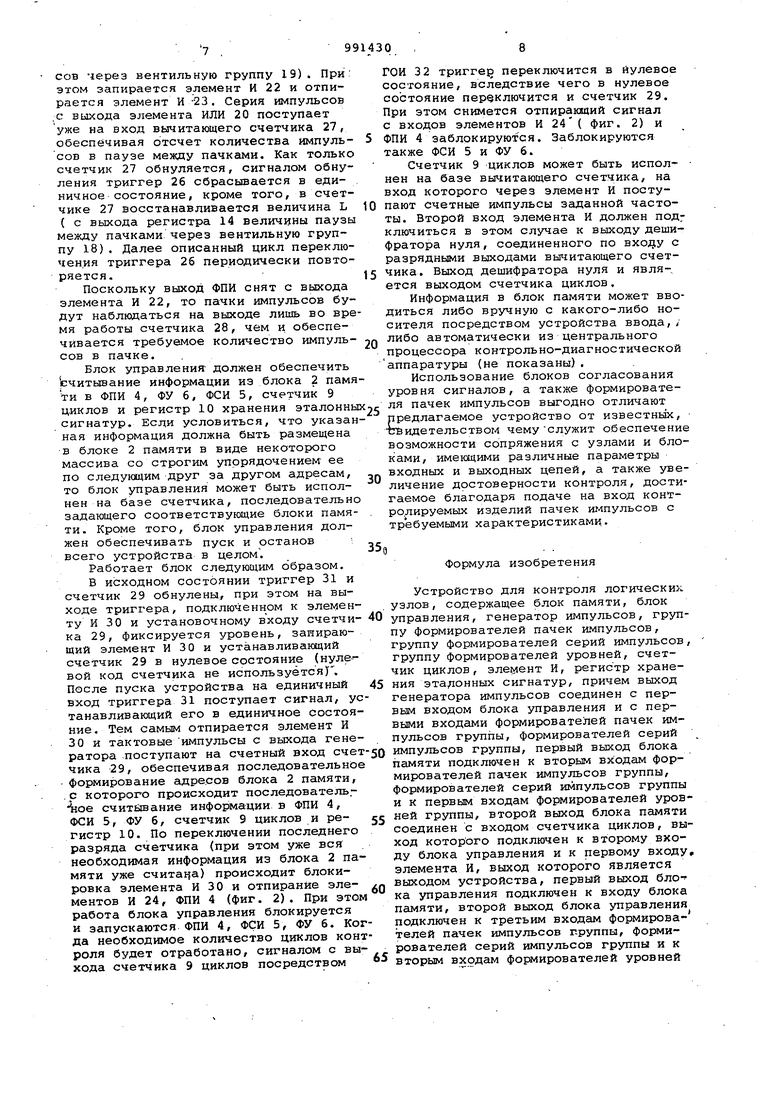

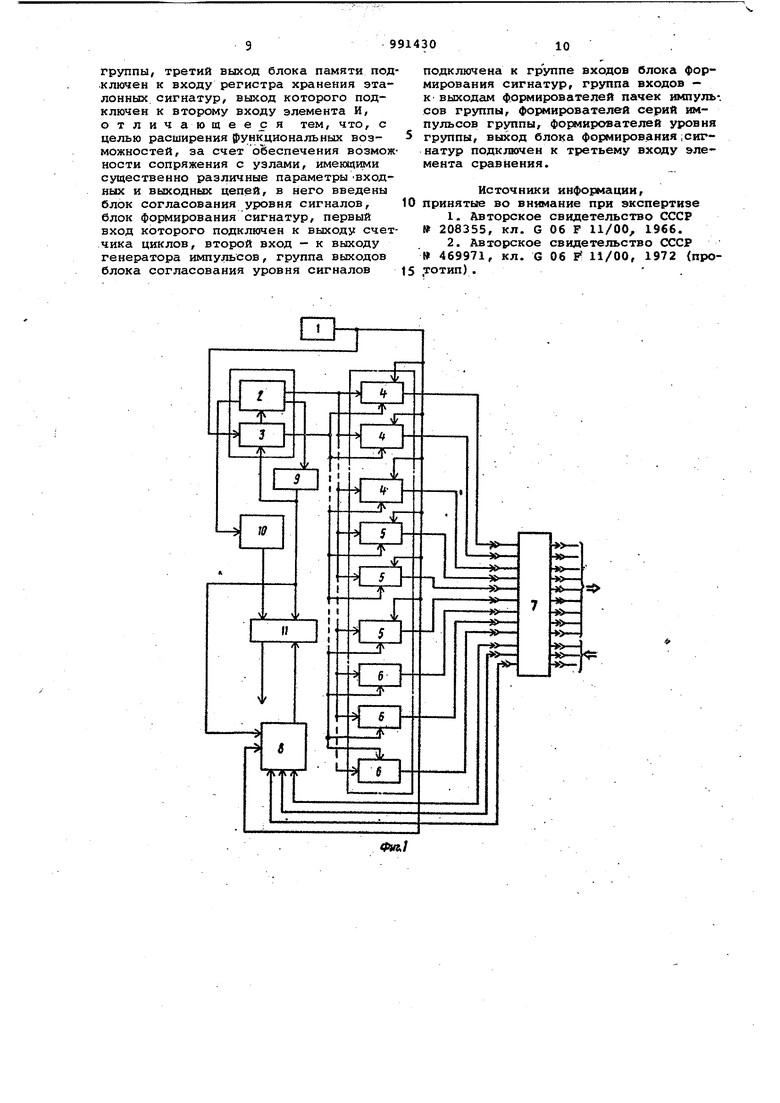

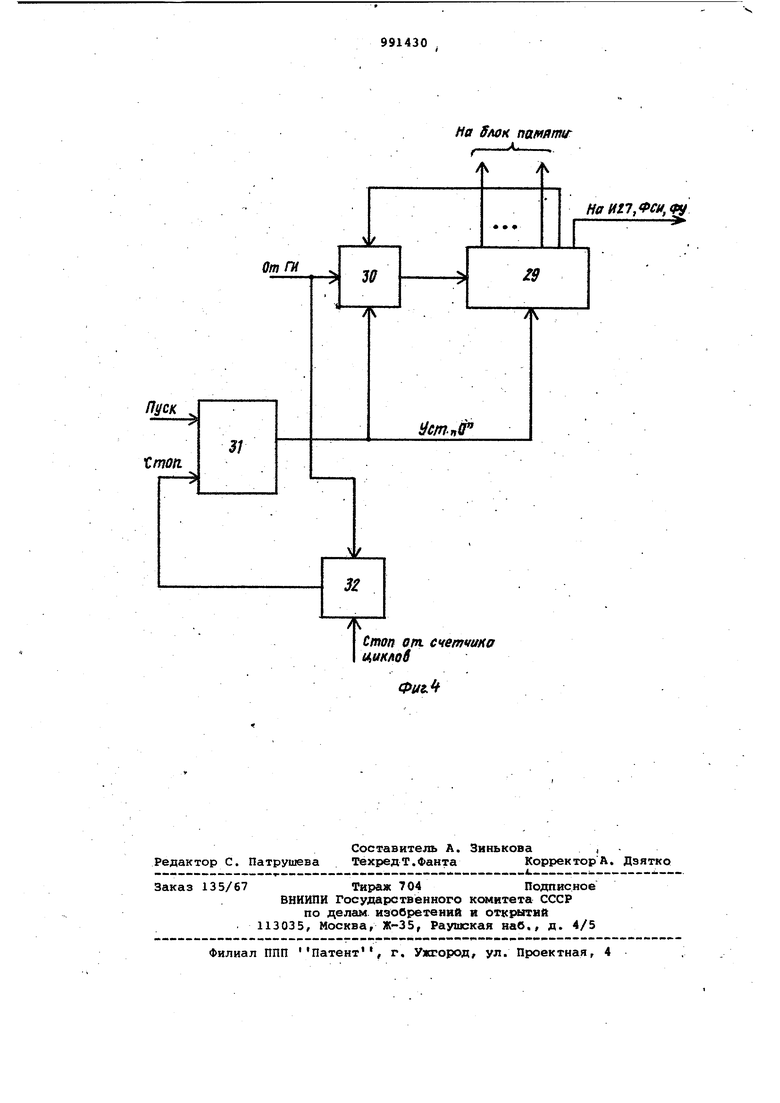

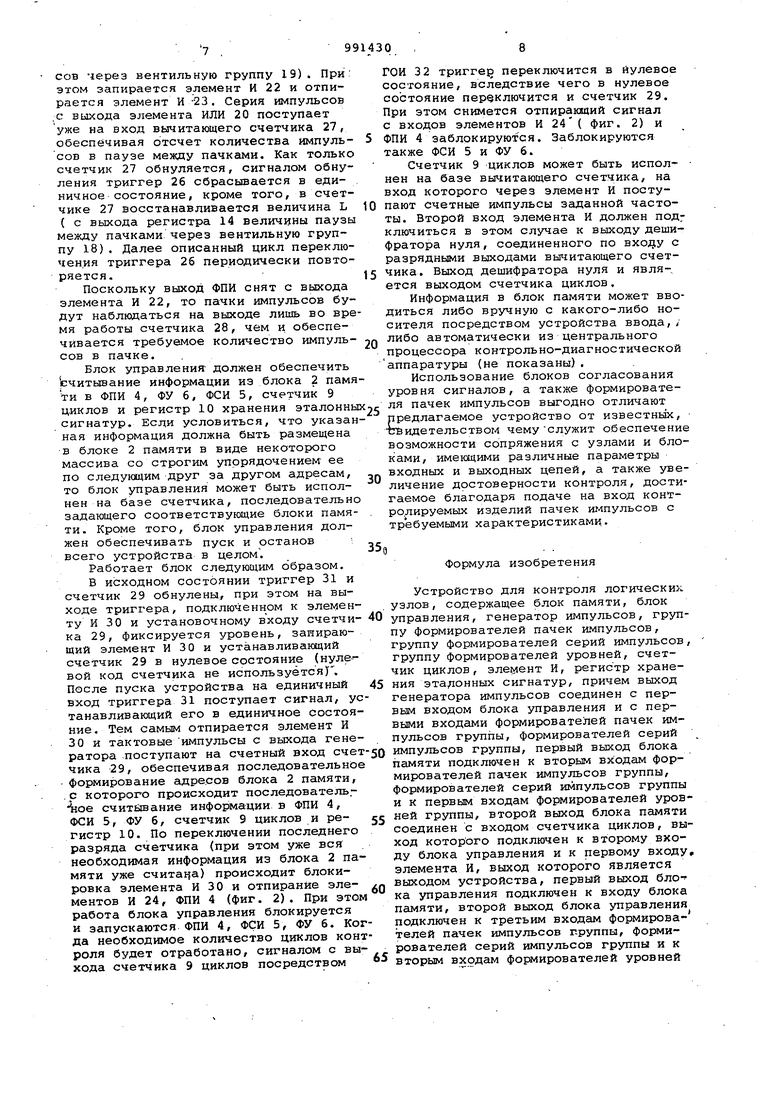

I В этом устройстве генератор стимулирующих воздействий, построенный на базе многоразрядного счетчика с управляемыми цепями сквозного переноса, подключаемыми к различным разрядам, хоть и дает 8оз1 1ожнЬстъ перебирать кодовые кимбинации на контроли.руемого изделия, однако лишь на ограниченном множестве их. Вследствие этого ограничивается возможность получения широкого набора кодовых комбинаций на входе испытуемого изделия, что особенно необходимо при контроле блоков памяти. Кроме того, данное устрой ство не обеспечивает сопряжение с узлами, имеющими различные параметры BxoflHiJX и выходных цепей. Цельн5 изобретения является расшире ние функциональных возможностей путем рбеспечения возможности сопряжения с узлами, имеющими существенно различные параметры входных и выходных цепей. Поставленная цель достигается тем, что в устройство для контроля логических узлов, содержащее блок памяти, блок управления, генератор импульсов, группу формирователей пачек импульсов группу формирователей серий импульсор группу формирователей уровней,счетчик циклов, элемент И, регистр хранения эталонных сигнатур, причем выход генератора импульсов соединен с первым входом блока управления и с перв-ыми входами формирователей пачек импульсов группы, формирователей серий импульсов группы, первый выход блока памяти подключен к вторьм входам форг мирователей пачек импульсов группы, формирователей серий импульсов группы и к первым входам формирователей. уровней группы, второй выход блока памяти соединен с входом счетчика цик лов , выход которого подключен к второму входу блока управления и к пер-. вому входу элемента И, выход которого является выходом устройства, первый выход блока управления подключен к входу блока памяти, второй выход блока управления подключен к третьим вхо дам формирователей пачек импульсов группы, формирователей серий испульсо группы и к вторым входам формирователей уровней группы, третий выход блока памяти подключен к входу регистра хранения эталонных сигнатур, выход которого подключен к второму входу элемента И, введены блок сог ласования уровня сигналов, блок формирования сигнатур, первый вход которого подклю чен к выходу счетчика циклов, второй вход - к выходу генератора импульсов, группа выходов блока согласования уровня сигналов подключена к группе входов блока формирования сигнатур, группа входов - к выходам формирова телей дачек импульсов группы, формирователей серий импульсов группы, фор мирователей уровня группы, выход блоi a формирования сигнатур подключен к третьему входу элемента сравнения. На фиг. 1 представлена структурная схема устройства для контроля логических узлов; на фиг. 2 - структурная схема одного изформирователей пачек импульсов; на фиг. 3 - временная диаг рамма, поясняющая работу формирователя пачек импульсов; на фиг. 4 - струк турная схема блока управления. Устройство содержит генератор 1 им пульсов (ГИ), блок 2 памяти, блок 3 управления, группу формирователей 4 пачек импульсбв (ФПИ), группу формирователей 5 импульсов (ФСИ), группу формирователей б уровней (ФУ), блок 7 согласования уровня сигнала, блок 8 формирования сигнатур,- счетчик 9 циклов , регистры 10 для хранения эталонных сигнатур и элемент 11 сравнения, Первый вычитающий счетчик 12., регистр гЗ величины длительности импульса, регистр 14 величины паузы между пачками, регистр 15 количества импульсов в пачке, счетчик 16 тактовых импульсов, вентильные группы 17-19, элемент 20 или, элементы 21 -24, триггеры 25 26, второй и третий вычитающие счет- , чики 27-28, счетчик 29, элемент 30 И, триггер 31 пуска, генератор 32 одиночных импульсов. Блок памяти служит для хранения программ контроля. Формирователи 4 пачек импульсов (ФПИ) обеспечивают формирование стимулирующих воздействий g характеристиками, заданными тестером. Формирователи 5 серий импульсов (ФСИ) предназначены для формирования последовательностей импульсов. /Формирователи 6 уровней 6.(ФУ) предназначены для формирования постоянных уро.вней. Блок 7 согласования уровня сигнала обеспечивает преобразование стимулирующих сигналов и ответных реакций по уровню и форме С тем,чтобы обеспечить функциональную совместимость контролирующей аппаратуры со всевозможными разнородными блоками и ячейками. Слегдует отметить, что для каждого типд контролируемых изделий разрабатывает-ся соответствующий блок согласования уровня сигнала. Блок 8 формирователя сигнатур представляет собой формирователь на базе сдвигового регистра, который снабжается рядом дополнительных обратных связей, участвующих в потактовой шифрации поступающего слова, преобразуя текущие входные биты, суммируясь с ними по модулю 2. Счетчиком 9 циклов задается количество циклов проверки - ., . Элемент 11 сравнения полученные сигнатуры сравнивает с эталонными, находящимися в регистрах 10 для хранения эталонных сигнатур. Устройство работает следующим образом. По командам из блока 3 управления из блока 2 памяти считывается информация относительно стимулиругадих воздействий, подлежащих реализации на каждом из входов контролируемого изделия (не Показано). Указанная информация заносится в ФПИ 4, ФСИ 5 и ФУ 6. Кроме того,, из блока 2 памяти в счетчик 9 циклов заносится информация о количестве циклов проверки, а в регистры 599 10 хранения эталонных сигнатур - эталонные реакции контролируемого издеяия. Следует отметить, что по мере эаписи информации в счётчик циклов на выходе последнего формируется уровень напряжения, который разрешает функционирование блока 8 формирования сигнатур и блокирует элемент 11 сравнения. Далее блоком 3 управления запускаются все ФПИ 4, ФСИ 5, ФУ 6, которые и обеспечивают фо змирование стимулирующих воздействий с заданными характеристиками. Выходные реакции контролируемого изделия накапливаются в блоке 8 формирования сигнатур. Работа ФПИ 4, фсу. 5 и блока формирования сигт натур синхронизируется генератором 1 импульсов. ,По мере прохождения каждого из ЦИКлов проверки содержимое счетчика 9 циклов уменьшается на единицу. По обнулении последнего блок 3 управления блокирует подачу стимулирующих воздей ствий, кроме того, блокируется также работа блока 8 формирования сигнатур, Сигналом со счетчика 9 циклов ерабатывает элемент 11 сравнения и полученные сигнатуры сравниваются с эталонными с вьщачей результатов сравнения на рабочее место оператора. На-рабочее место оператора возможно вывести и соответствующие контрольные точки блока согласования уровня сигналов с целью сообщения оператору дополнительной информации в случае отрицательных результатов проверки, Кроме того, в устройстве возможна и ручная проверка изделий посредством манипуляции коммутационными органами/: рабочего места,при этом, выходы последних сопрягаются с контролируемым из- делием через- блок согласования уровгня сигналов, Формирователь пачек импульсов рабо тает следующим образом, В первый вычитающий счетчик заносится информация, поступающая из бло-ка 2 памяти, Вычитакадий счетчик 12 с6 держит информацию о паузе дТ, которую надо вьщержать после запуска (фиг. 3J . Регистр 13 величины длительности импульса хранит инфо1 ацию о длитбльности импульсов в пачке М. Регистр 14 величины паузы между пачками хранит информацию о количестве импульсов, временем следования которых определяется пауза между пачками. Регистр 15 количества импульсов в пачке содержит информацию о количестве импульсов N в пачке. . Счетчик 16 тактовых импульсов служит для задания серий импульсов различной частоты. Рентильяая группа 17 служит для выборки серии импульсовСоответствую06щей частоты. Первый триггер 25 пред назначен для отпирания элемента 21, Триггер 26 служит для поочередного отпирания элементов И 22 - 23. Второй вычитающий счетчик 27 служит для отс-чета величины паузы между пачками.Третий вычитающий счетчик 28 служит для отсчета количества импульсов в пачке. Вентильные группы 18 и 19 служат для передачи кодов величины паузы между пачками из регистра 14 величины паузы между пачками и количества импульсов в пачке, из регистра 15 количества ши пульсов в пачке соответственно в счетчик 27 величины паузы между пачками и счетчик 28 количества импульсов в пачке. , Формирователь пачек импульсов ра ботает следующим образом. Информация о количестве импульсов N в пачке, о количестве импульсов 4, :временем следования которых определяется пауза между пачками, а также информация о длительности импульсов М в пачке и о паузе Д Т, которую надо выдержать после запуска ФПИ, поступает в первый вычитающий счетчик 12. При записи информации в регистр 14 величины паузы между пачками и в регистр 15 количества импульсов в пачке информация автоматически заносится соответственно в вычитакячие счетчики27 и 28, в исходном состоянии триггеры 25 и 26 находятся соответственно в нулевом и единичном состояниях, После запуска схемы начинает работать вычитающий счетчик 12, а остальные узлы схемы бездействуют пока не переключится триггер 25. Как только счетчик 12 отсчитывает положенную паузу ДТ, триггер 25 устанавливается в единичное состояние, отпирая, тем caMbHvi элемент И 21, на второй вход последнего через элемент ИЛИ 20 поступает серия импульсов с выходов счетчика 16 тактовых импульсов, управляемых со стороны регист-ра 13 длительноети импульса посредством вентильной группы 17. Поскольку при каждой задайной величине М, которую целесообразно представить унитарным кодом, отпирается лишь один вентиль из всей вентильной группы, то на выходе элемента ИЛИ 20 получаем серию импульсов заданной частоты. Поскольку триггер 26 первоначально находится в единичном состоянии, то импульсы с выхода элемента ИЛИ 20 через открытый элемент И 22 поступают на вход вычита1рщего счетчика. 28 до тех пор, пока последний не обнулится. Тем бамым обеспечивается отсчет величины N, Как только счетчик 28 обнуляется, сигналом обнуления триггер 26.сбрасывается в нулевое состояние и, кроме того, в счетчике 28 восстанавливается величина N (с выхода регистра 15 количества HMnyj -сов через вентильную группу 19). При этом запирается элемент И 22 и отпирается элемент И -23. Серия импульсов ,с выхода элемента ИЛИ 20 поступает уже на вход вычитающего счетчика 27, обеспечивая отсчет количества импульсов в паузе между пачками. Как только счетчик 27 обнуляется, сигналом обнуления триггер 26 сбрасывается в единичное состояние, кроме того, в счетчике 27 восстанавливается величина L ( с выхода регистра 14 величины паузы между пачками через вентильную группу 18). Далее описанный цикл переключения триггера 26 периодически повторяется. Поскольку выход ФПИ снят с выхода элемента И 22, то пачки импульсов будут наблюдаться на выходе лишь во вре мя работы счетчика 28, чем и обеспечивается требуемое количество импульсов в пачке. Блок управления- должен обеспечить считывание информации из блока 2 памя ти в ФПИ 4, ФУ 6, ФСИ 5, счетчик 9 циклов и регистр 10 хранения эталонны сигнатур. Есди условиться, что указан ная информация должна быть размещена в блоке 2 памяти в виде некоторого массива со строгим упорядочением ее по следующим друг за другом адресам, то блок управления может быть исполнен на баэе счетчика, последовательно задающего соответствующие блоки памяти. Кроме того, блок управления должен обеспечивать пуск и останов всего устройства в целом. Работает блок следующим образом. В исходном состоянии триггер 31 и счетчик 29 обнулены, при этом на выходе триггера, подключенн ом к элементу И 30 и установочному входу счетчика 29, фиксируется уровень, запирающий элемент И 30 и устанавливающий счетчик 29 в нулевое состояние (нулввой код счетчика не используётсяГ. После пуска устройства на единичный вход триггера 31 поступает сигнал, ус танавливающий его в единичное состояние. Тем самым отпирается элемент И 30 и тактовые импульсы с выхода генератора поступают на счетный вход счет чика 29, обеспечивая последовательное формирование адресов блока 2 памяти, .с которого происходит последователь ое считйвание информации в ФПИ 4, ФСИ 5, ФУ б, счетчик 9 циклов и регистр 10. По переключении последнего разряда счетчика (при этом уже вся необходимая информация из блока 2 памяти уже считала) происходит блокировка элемента И 30 и отпирание элементов И 24, ФПИ 4 (фиг. 2). При этом работа блока управления блокируется и запускаются ФПИ 4, ФСИ 5, ФУ б. Ког да необходимое количество циклов конт роля будет отработано, сигналом с выхода счетчика 9 циклов посредством ГОИ 32 триггер переключится в Нулевое состояние, вследствие чего в нулевое состояние переключится и счетчик 29. При этом снимется отпирающий сигнал с входов элементов и 24( фиг. 2) и ФПИ 4 заблокируются. Заблокируются также ФСИ 5 и ФУ б. Счетчик 9 циклов может быть испол- нен на базе вычитающего счетчика, на вход которого через элемент И поступают счетные импульсы заданной частоты. Второй вход элемента И должен подг ключиться в этом случае к выходу дешифратора нуля, соединенного по BXOjDiy с разрядными выходами вычитающего счетчика. Выход дешифратора нуля и является выходом счетчика циклов. Информация в блок памяти может вводиться либо вручную с какого-либо носителя посредством устройства ввода,/ либо автоматически из центрального процессора контрольно-диагностической аппаратуры (не показаны). Использование блоков согласования уровня сигналов, а также формирователя пачек импульсов выгодно отличают предлагаемое устройство от известньах, тгвидетельством чему служит обеспечение возможности сопряжения с узлами и блоками, имеющими различные параметры входных и выходных цепей, а также увеличение достоверности контроля, достигаемое благодаря подаче на вход контролируемых изделий пачек импульсов с требуемыми характеристиками. Формула изобретения Устройство для контроля логических узлов, содержащее блок памяти, блок управления, генератор импульсов, группу формирователей пачек импульсов, группу формирователей серий импульсов, группу формирователей уровней, счетчик циклов, элемент И, регистр хранения эталонных сигнатур, причем выход генератора импульсов соединен с первым входом блока управления и с первыми входами формирователей пачек импульсов группы, формирователей серий импульсов группы, первый выход блока памяти подключен к вторым входам формирователей пачек импульсов группы, формирователей серий импульсов группы и к первым входам формирователей уровней группы, второй выход блока памяти соединен с входом счетчика циклов, выход которого подключен к второму входу блока управления и к первому входу, элемента И, выход которого является выходом устройства, первый выход бло- ка управления подключен к входу блока памяти, второй выход блока управления подключен к третьим входам формирователей пачек импульсов г-руппы, формирователей серий импульсов группы и к вторым входам формирователей уровней

группы, третий выход блока памяти под.ключей к входу регистра хранения эталонных сигнатур, выход которого подключен к второму входу элемента И, отличающееся тем, что, с целью расширения функциональных возможностей, за счет оЬеспечения возможности сопряжения с узлами, имеющими существенно различные параметры входных и выходных цепей, в него введены блок согласования уровня сигналов, блок формирования сигнатур, первый вход которого подключен к выходу счетчика циклов, второй вход - к выходу генератора импульсов, группа выходов блока согласования уровня сигналов

подключена к группе входов блока формирования сигнатур, группа входов - к выходам фО| ирователей пачек импуль-. сов группы, формирователей серий импульсов группы, формирователей уровня группы, выход блока формирования;сигнатур подключен к третьему входу элемента сравнения.

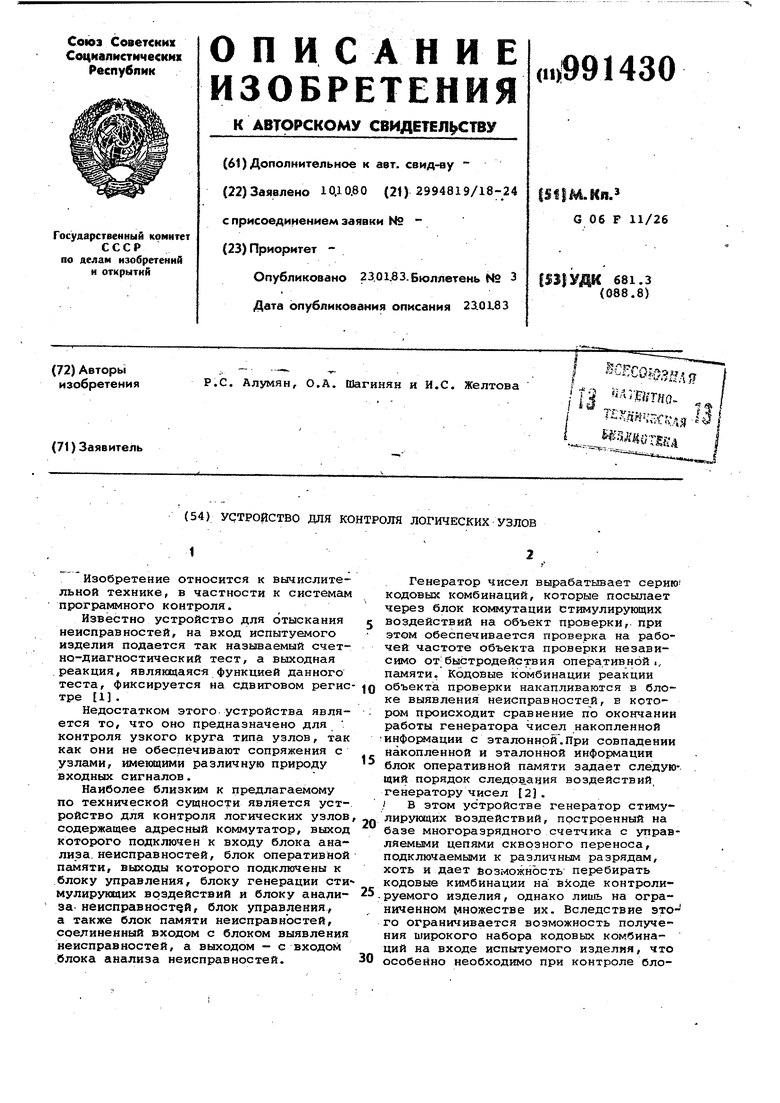

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 208355, кл. G Об F 11/00, 1966.

2.Авторское свидетельство СССР

469971, кл. G 06 11/00, 1972 {прототип). .

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1984 |

|

SU1171797A1 |

| Устройство для генерации пачек импульсов | 1984 |

|

SU1229948A1 |

| Селектор серий импульсов | 1989 |

|

SU1670781A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1991 |

|

RU2023309C1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство для моделирования систем массового обслуживания | 1989 |

|

SU1644156A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Устройство для контроля электрических соединений | 1989 |

|

SU1633433A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1529221A1 |

| СПОСОБ ФОРМИРОВАНИЯ ПАЧЕК ИМПУЛЬСОВ | 1995 |

|

RU2098919C1 |

йт

м

I-I 1-I гт п I-I п гт г г- г- -J LJ LJ L. J « J U-J I.J I. J L.J uJ LJ I1

н

Фиг. 2

лг

L

ОтГИ

Пуск

31

Стоп.

Т

На SMU пимйгтг л.

НаИ17,Фси,(М

Z9

Яст-пЗ

Стоп от. счетчика циклов

Фиг.

Авторы

Даты

1983-01-23—Публикация

1980-10-10—Подача