. t.

Изобретение относится к цифровой вычислительной технике и может быть ис- 4 пользовано в автоматизированных системах .управления при воспроизведении широкого класса функциональных зависимостей.

Известны устройства для воспроизведения функций .

Однако точность известных устройств JQ ограничена в основном погрешностью реализуемой в них линейной аппроксимации.

Наиболее близким к предлагаемому 15 техническим решением является устройство для вычисления элементарных функций, содержащее генератор импульсов, блок управления, ключ, переключатель коэффициентов деления, делитель , 20 программно-распределительнь1й блок, две схемы ИЛИ, три реверсивных счетчика, множительный блок и соответствующие связи 2 .

В этом устройстве вычисляемая функция представляется степенным рядом

)р(к; A-x, о;

где А V - постоянные коэффициенты, определяемью по величине и знаку для каждой вычисляемой функции.

Недостатком данного устройства является то, что оно воспроизводит узкий класс функций непрерьшных и гладких, к которым применим интерполяционный полином Лагранжа, а также недостаточная точность воспроизведения функций;

Целью изобретения является повьпиение точности работы устройства для воспроиэведения функций.и воспроизведение более широкого класса функций.

В обшем виде вычисляемая функция может быть представлена в виде кусоч- но полиномиального сплайна степени М

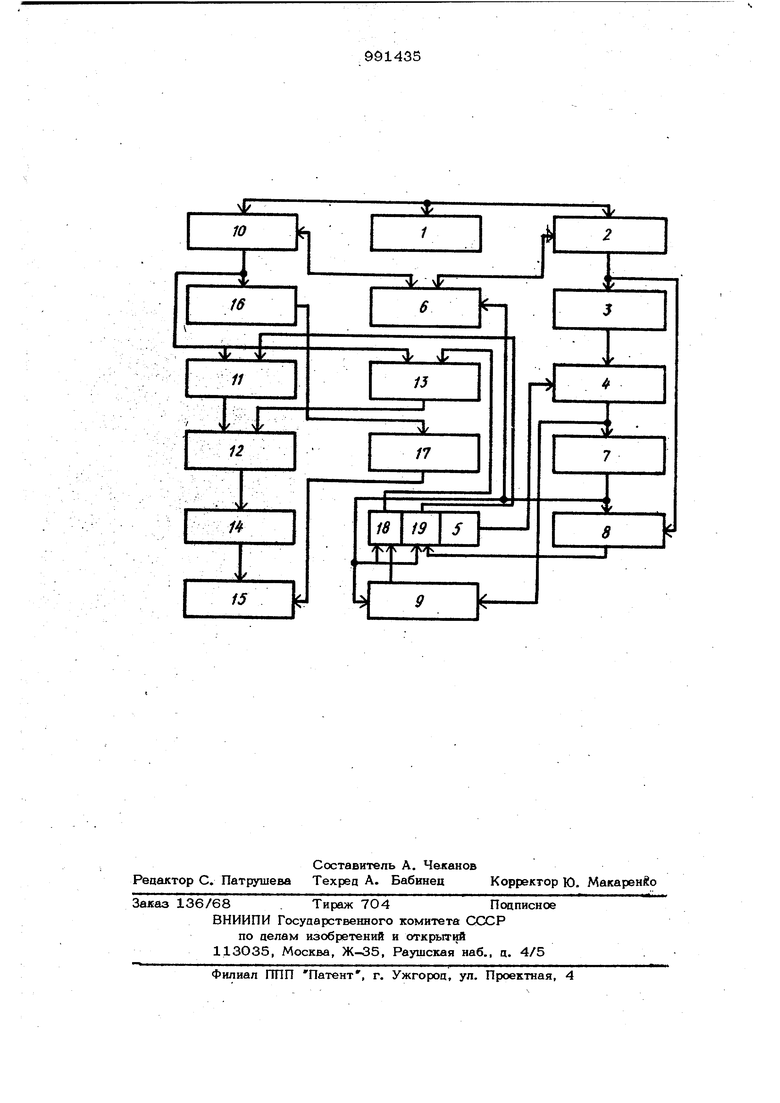

.iU)-5U).).,,)|i) 9 заданного на сетке узлов и являющегося на кажаом из отрезков полиномом степени И1 5(y)--A(j,... ). Известно, что сплайны обладают лучшей скоростью схоцгаиости к воспроизвоцимой функции, чем традиционные полиномы вица (1), и в силу своих свойств могут использоваться для воспроизведения боле широкого класса функций, чем это позво ляют полиномы (1). Поставленная цель достигается тем, что в устройство, содержащее генератор импульсов и блок умножения, введены счетчик числа отрезков, блок пам&ти узлов сетки аргумента, блок вычитания, регистр номера отрезка, регистр разное ти, регистр результата, триггер сброса, две схемы сравнения, две группы элемен тов И, вычитающий счетчик степени, бло памяти коэффициентов, блсж возведения в степень, накапливающий сумматор и элемент задержки, причем выход генераlopa импульсов соединен со счетными входами вычитающего счетчика степени и счетчика числа отрезков, выходы котор го соединены с первыми входами элементов И первой группы и адресными входами блока памяти узлов сетки аргумента, выходы которого соединены с входами уменьшаемого блока вьгчитания, выходы которого подключены к первым входам элементов И второй группы и входам первой схемы сравнения, выход которой соединен с входами синхронизааив регист ра разности и регистра номера отрезка и вторыми входами элементов И первой и второй группы, выходы элементе И .первой группы соединены с информационными входами регистра номера отрезка, а эыходы элементов И второй группы со единены с информационньми входами регистра разности, выходы которого соединены с входами основания степени блока возведения в степень, выходы которого соединены с первыми входами блока умножения, выходы которого соединены с входами накапливающего сумматора, выходы которого соединены с информационными входами регистра результата, кход вьгч1ггаемого блока вычитания сое- динен с входом устройства, выходы регист ра номера отрезка соединен с входами старших разрядов адреса блока памяти 54 коэффициентов, выходы которого соединены со вторыми входами блока умножения, выход первой схемы сравнения соединен со счетным входом триггера сброса, прямой выход которого соединен с входом сброса счетчика числа отрезков, а инвероный - с входом установки вычитающего счетчика степени, выходы которого соединены с входами младших разрядов адреса блока памяти коэффициентов, входами показателя степени блока возведения в степень и входом второй схемы сравнения, выход которой через элемент задержки соещшен с входом синхронизации реГгистра результата. На чертеже схематически изображено предлагаемое устройство. Устройство содержит генератор 1 импульсов, счетчик 2 числа отрезков, блок 3 памяти узлов сетки аргумента, блок 4 вычитания, вход 5 устройства, триггер 6 сброса, первая схема 7 сравнения, первая группа элементов И 8, вторая группа элементов И 9, вычитающий счет- чик Ю степени, блок 11 памяти коэффи-циентов, блок 12 умножения, блок 13 возведения в степень, накаш1ивающ й сумматор 14, регистр 15 результата, вторая схема 16 сравнения, элемент 17 задержки, регистр 18 разности, регистр 19 номера отрезка. Блоки 3, 11 памяти представляют собой бьютродействующую память. Причем блок 11 памяти представляет собой двухадресную память в виде матрицы. регистров. Количество строк.блока 11 определяется максимально возможным числом отрезков (К| ), на которых задан сплайн (2). Количество столбцов блока 11 определяется числом (Vtl + 1), где ки степень сплайна. Блок 3 памяти представляет собой одноадресную память и содержит (М ) ячеек. Триггер 6 сброса служит для разрешения счета счетчику 2 или вычитающему счетчику 10, I Разрядность счетчика 2 определяется максимально возможным числом отрезков ( VI ), а разрядность вычитающего счетчика 10 числом (т +1), где vn - степень сплайна. Устройство работает следующим образом. Перед началом работы устройство приводится в исходное состояние, а именно, в блок 3 памяти заносится массив узлов сетки Xi ( г- 1,М ). В блок 11 памяти заносится матрица коэффициентов Ag И djV; l-Oin). Число строк матрицы соответствует числу отрезков ( N ) а число столбцов определяется числом (ум + 1), гае 1У - степень сплайна. В схемы 7 и 16 сравнения заносятся нуля. Триггер 6 устанавливается в нуль. Счетчик 2 устанавливается в нуль, а в вычитающий счетчик Ю заносится число (т + 1). На вход 5 подается значение когорого необходимо вы числить .значение функции. I По сигналу Пуск запускается генера тор 1 импульсов. Первый импульс с ге- нератора 1 импульсов увеличивает содержимое счетчика 2 на единицу. По адресу, определяемому содерекимым счетчика 2, из блока 3 памяти считывается число, ксугорое поступает в блок 4 вычитания, где из него вычитается число, поступившее с входа устройства. Результат вычитания подается на вход первой схемы 7 сравнения. Описанные операции повторяются до тех пор, пока результат вычитания не станет бопыне или равным нулю, тогда на выхсаде первой схемы 7 сравнения вырабатьшается сигнал, который разрешает запись результата блока 4 вычитания в регистр 18 разности, а содержимого счетчика 2 - в регистр 19 номера отрезка. Этот же сигнал поступает на вход триггера 6, который отключает генератор, сбрасывает счетчик 2 и разрешает счет счетчику 10. Очередной импульс с генератора 1 импульсов поступает на вход вьгаитаюшего счетчика 1О и уменьшает его содержимое на единицу. Из регистра 18 разности на вход блока 13 возведения в степень поступае числоХ - X, которое возводится в степень, равную числу, поступившему с вычитаю- шего счетчика 10. Результат поступает на второй вход блока 12 умножения. По адресу, определяемому содержимым вь читающего счетчика 10 и содеркимым регистра 19 (вьпитаюший счетчик 1О задает младшие разряды адреса, старшие разряды поступают с регистра 19), из блока 11 памяти считывается число, равное соответствующему коэффициенту Д У сплайна и поступает на первый вход блока 12, где умножается на число () , поступившее из блока 13 воэведения в степень. Результат поступает на вход накопительного сумматора 14, . гце в зависимости от знака поступающей A j4xi-x)e величинь происходит кгисапливание величин Wi-)) Описанные операции повторяются до тех пор, пока содержимое вычитающего счетчика 1О не станет равным нулю. При этом йа выходе второй схемы 16 сравнения вырабатьюается сигнал, который через элемент 17 задержки разрешает вьщачу содерисимого сумматора 14 в регистр 15 результата. Оценка технико-экономического эффекта от испспьзования изобретения проводилась теоретически и методом математического моделирования на ЭВМ. Результаты псжазали, что предлагаемое изобретение позволяет решить задачу воспроизведения более широкого класса функций и с большей точностью. Дейст вительно, если воспроизводимая функция f (X) трижды непрерывно дифференцируема на интервале воспроизведения, то для кубического сплайна (ки 3) точность интерполяции определяется формулой |5(.Х)-{(Х)|«|цХ . Н и1ах|1i I, V)., (,;,), i(x)|,Xo ц, порядок п(Я1ближения алгебраическими многочленами, наименее уклоняющимися степени не выше N , определяется как |Т)(х)-(ч)|5С-а7.нЧ где С - величина, близкая к единице я не зависящая от Н , Т)(Х)-многочлен вица {); порядок приближения Сх) интерполяционйыми полиномами Лагранжа степени V) по узлам полинома Чебьппева Vi-й степени, наименее, отклоняющегося от нуля, определяется как/ lG|U)-5(it)j ClTH M((NH); Из сравнения формул (3)-(5) видно, что наилучшей скоростью сходимости обладает кусочно-полиномиальный кубический сплайн. При прочих равных условиях порядок приближения кубическим сплайном в iO,8 раз раз лучше, чем порядок при- ближения алгебраическим многочленом DU) и в 10,8 (9 + ( N + 1) раз лучше, чем интерполяционный полиномом Лагранжа. При этом возможность выбора степени сплайна Hi, его цефекта K.(l Kt;Hi ( номерщ -К указывает пос.лецнюю непрерьшную производную сплай-я на) и узлов позволяет воспроизводить функции с нерегулярными свойствами гладкости на участке воспроизведения Например, для функции V- UlXGE-i,- ошибка приближения сплайном 5(Х) степе ни 1 дефекта 1 с узлом в точке X О будет равна нулю, ошибка приближения сплайном степени 2 дефекта 1 с двумя нефиксированными узлами не превышает величины Е/2., где - сколь угодно малая величина, в то время, как приближение функции (Х),ХеГН,1 многочленами степени не выше ( не может быть лучше, чем E/N, где - абсолютная постоянная. Формула изобретения Устройство для воспроизведения функций, содержащее генератор импульсов, и блок умножения, отличающее - с я тем, что, с целью повышения точкости и расширения класса решаемых задач за счет аппроксимации функции сплай нами, в него введены счетчик числа отрезков, блок цамяти узлов сетки аргумен та, блок вычитания, регистр номера от резка, регистр разности, регистр результ та, триггер сброса, две схемы сравнения две группы элементов И, вычитаюший счетчик степени, блок памяти коэффициентов, блок возведения в степень, накапли ваюший сумматор и задержки, причем выход генератора импу.осов соединен со счетными входами вычитаюшего счетчика степени и счетчика числа отрез ков выходы которого соединены с первьь ми входами элементов И первой группы и адресными входами блока памяти узлов сетки аргумента, выходы которого соединены с входами уменьшаемого блока вычитания, выходы которого подключены к первым входам элементов И второй группы и входам первой схемы сравнения, выход которой соединен с входами синхронизации регистра разности и регистра номера отрезка и вторыми входами элементов И первой и второй группы, выходы элементов И первой группы соединены с информационными входами регистра номера отрезка, а выходы элементов И второй группы соединены с информационными входами регистра разности, выходы которого соединены с входами основания степени блока возведения в степень, выходы которого соединены с первыми входами блока умножения, выход которого соединен с входом накапливающего сумматора, выходы которого соединены с информационным входом регистра результата, вход вычитаемого блока вычитания соединен с входом устройства, выходы регистра номера отрезка соединены с входами старших разрядов адреса блока памяти коэффициентов, выход которюго соединен со вторым входом блока умножения, выход первой схемы сравнения соединен сО счетным входом триггера сброса, прямой вьгход которого соединен с входом сброса счетчика числа отрезков, а инверсный с входом установки вычитающего счетчика степени, выходы которого соединены с входами младших разрядов адреса блока памяти коэффициентов, входами показателя степени блока возведения в степень н входом второй схемы сравнения, выход которой через элемент задержки . соединен с входом синхронизации регистра результата. Ii Источники информации, прин5 Тые во внимание при экспертизе 1.Авторское свидетельство СССР № 459777, кл. G 06 F 15/20, 1975. 2.Авторское сшдетельсгво СССР № 444187, кл. GO6F 15/20, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Устройство для возведения в п-ую степень | 1982 |

|

SU1132287A1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143131C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2143132C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116669C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2140099C1 |

| СПОСОБ ОЦЕНИВАНИЯ НЕСУЩЕЙ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2100812C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| Дифференцирующее устройство | 1982 |

|

SU1042027A1 |

| Устройство для синтеза регрессионных моделей многомерной статистики | 1980 |

|

SU942031A1 |

Авторы

Даты

1983-01-23—Публикация

1981-03-23—Подача