держит реверсивный счетчик, третий регистр, второй коммутатор, первая группа информационных входов которо го соединена соответственно с разря ными выходами реверсивного счетчика инверсным вxoдa и второго элемента первой группы и разрядными входами третьего регистра, третий формирова тель адреса содержит второй счетчик третий и четвертый коммут.аторы, первый элемент ИЛИ, выход которого .соединен с входом записи второго счетчика, разрядные выходы которого соединены с первой . группой информационных входов третьего коммутато ра, разрядными входами первого регистра, второй группой информационных входов первой схемы сравнения и информационными входами пятого и шестого регистров группы, первый и второй управляющие входы первого, второго и третьего коммутаторов сое динены с первым и вторым выходами задания адреса блока управления, выходы управления записью которого соединены соответственно с входами записи вычитающего счетчика, реверсивного счетчика, счетчика номера переменной и третьего регистра, тактовый вход вычитающего счетчи- ка, суммирующий вход реверсивного счетчика, вычитающий вход реверсивного счетчика, тактовый вход второг счетчика и вычитающий вход счетчика номера переменной соединены соответ ственно с группой тактовых выходов блока управления, выход сброса кото рого соединен с входами сброса реверсивного счетчика и второго счетчика, выходы группы управляющих .выходов блока управления соединены соответственно с первым и вторым управляющими входами коммутатора операнда, первый и второй управляющие входы четвертого коммутатора со динены с входами первого элемента ИЛИ, первая и вторая группы информа ционных входов коммутатора операндо соединены соответственно с выходами первого и второго блоков памяти, третья и четвертая группы инфор мационных входов коммутатора операн дов соединены соответственно с выходами третьего и четвертого регист .ров группы и инверсными входами пятого и шестого элементов И первой группы,первый и второй выходы коммутатора операндов соединены соответственно с первым и вторым входам умножителя и сумматора, выходы счетчика номера переменной соединены соответственно с второй группой информационных входов первого, второго и третьего коммутаторов, выходы которых соединены соответственно с адресными входами первого, второго и третьего блоков памяти, разрядные выходы первого и второго регистров группы соединены соответственно с первой и второй группами информационных входов четвертого коммутатора, блок управления содержит генератор импульсов, счетчик циклов, дешифратор, второй элемент ИЛИ, первый и второй шифраторы, вторую группу элементов,И, причем выход генератора импульсов соединен с тактовым входом счетчика циклов, выходы которого соединены соответственно с входами дешифратора, выходы которого соединены соответственно с входами первого шифратора, первая группа выходов дешифратора соединена соответственно с первым входом элементов И второй группы, выходы которых соединены соответственно с входами первой группы входов второго шифратора и первой группой входов второго элемента ИЛИ, вторые группы входов которых соединены соответственно с выходами второй группы выходов дешифратора, выходы с первого по и -Ь второго шифратора соединены соответственно с информационными уходами счетчика циклов,установочный вход которого соединен-с выходом второго элемента ИЛИ, h-и выход второго шифратора соединен с входом останова генератора импульсов,первый вход блока управления соединен с вторыми входами первого и инверсным входом десятого элементов И второй группы, второй вход.блока з равления соединен с инверсным входом второго элемента И второй группы, третий вход блока управления соединен с инверсным входом третьего элемента И второй группы, четвёртьй вход блока управления соединен с вторыми входами четвертого, девятого и тринадцатого элементов И второй группы, пятый вход блока управления соединен с инверсными входами пятого и четырнадцатого элементов И второй группы и вторым входом одиннадцатого элемента И второй группы, шестой вход блока управления соединен с вторым входом шестого элемента И второй группы.

седьмой вход блока управления соединен с вторыми входами седьмого и двенадцатого элементов И второй группы, восьмой вход блока управления соединен с вторым входом восьмого элемента И второй группы, выходы первого шифратора являются выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления полинома | 1982 |

|

SU1098003A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Дифференцирующее устройство | 1982 |

|

SU1042027A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Многоканальный интерполятор функций | 1986 |

|

SU1361588A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ ВП-Ю СТЕПЕНЬ, содержащее блок управления, первый счетчик, первый, второй и третий блоки памяти, блок умножения и сложения, группу регистров и блок сравнения, который содержит две схемы сравнения, первую группу элементов И,первый регистр, выходы которого соединены соответственно с первой группой информационных входов первой схемы сравнения, выход второй схемы сравнения, выходы первого и второго элементов И первой группы, выход первой схемы сравнения, выходы с третьего по шестой элементов И первой группы соединены соответственно с первым по восьмой входами блока управления, блок умножения и сложения содержит умножитель, сумматор, коммутатор результата, информационные входы которого соединены с выходами умножителя и сумматора, выходы управления записью и считыванием блока управления соединены со-. ответственно с входом считывания первого и второго блоков памяти, входом записи второго блока памяти. входом считывания третьего блока памяти, входом записи третьего блока памяти, входами записи с первого по шестой регистров группы, и :входом записи первого регистра, выходы выбора режима блока управления соединены соответственно с входами управления умножения и сложения коммутатора результата, первый тактовый выход блока управления соединен со счетным входом первого счетчика, выходы которого соединены с инверсными входами четвертого элемента И первой группы, первая и вторая группы информационных входов второй схемы сравнения соединены соответственно с выходами пятого и шестого ре(Л гистров группы, информационные входы, регистров группы с первого по четвертый объединены и соединены с выходом третьего блока памяти и информационным входом второго блока памяти, информационный вход третьего блока памяти соединен с выходом коммутатора результата, отличающееся тем, что, с целью расширения класса решаемых задач за счет обеспечения возможности возведения в степень функций г независимых переменных, в устройство введены счетчик номера переменной, коммутатор операндов, первый, второй и третий формирователи адреса, причем первый формирователь адреса содержит вычитающий счетчик, второй регистр, первый коммутатор, первая группа информационных входов которого соответственно с разрядными выходами вычитающего счетчика и инверсными входами первого элемента И первой группы, второй формирователь адреса со

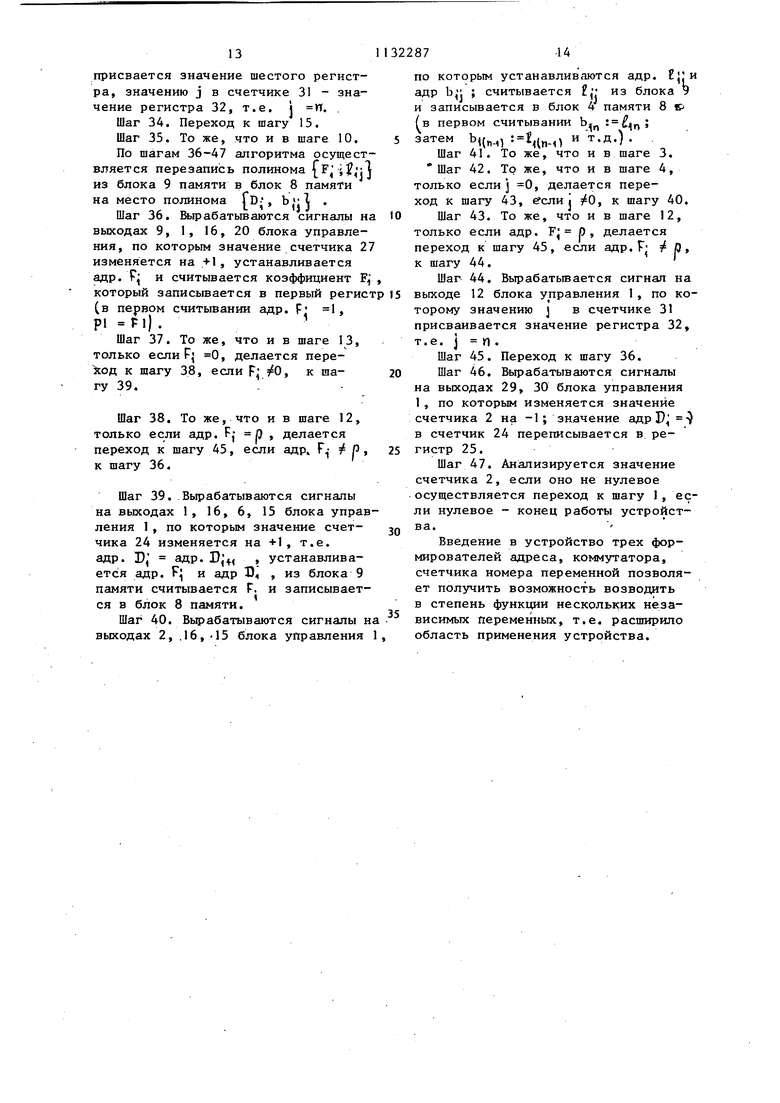

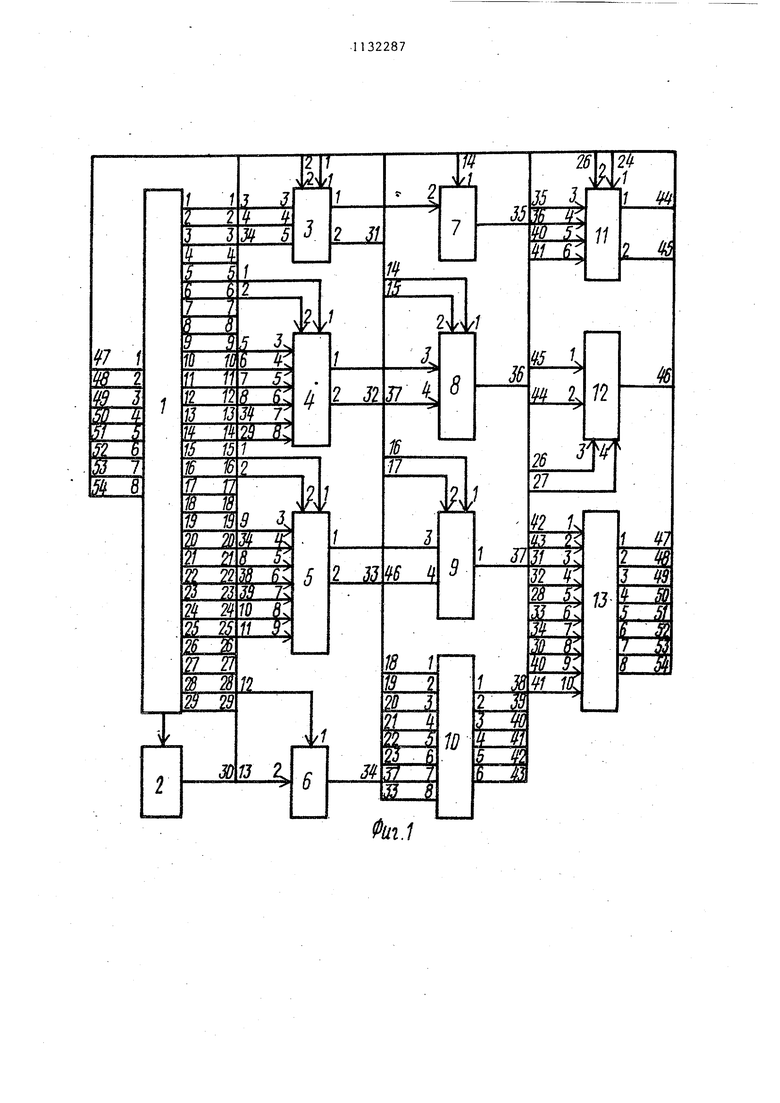

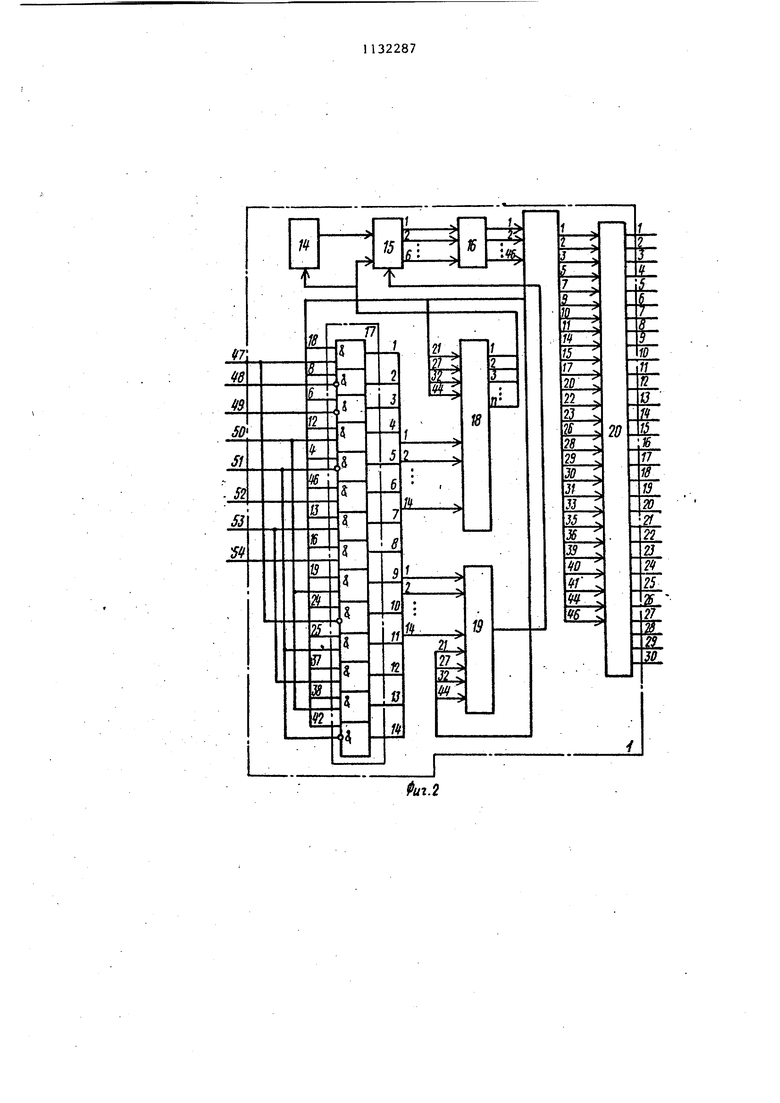

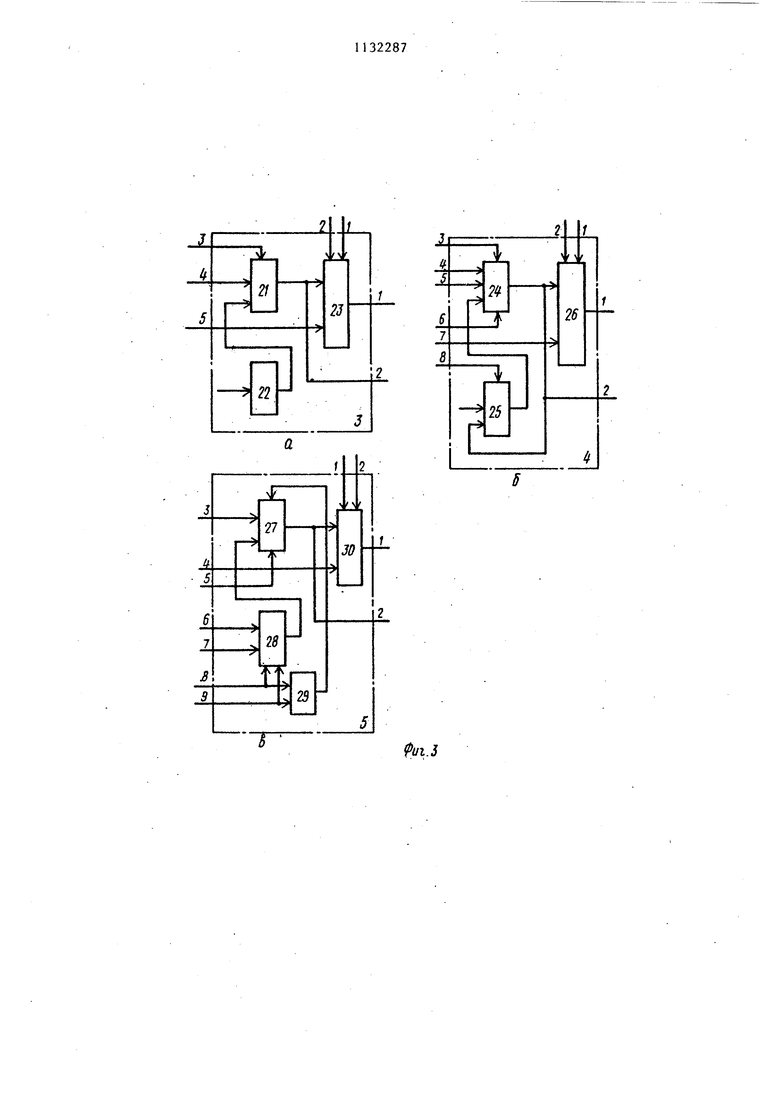

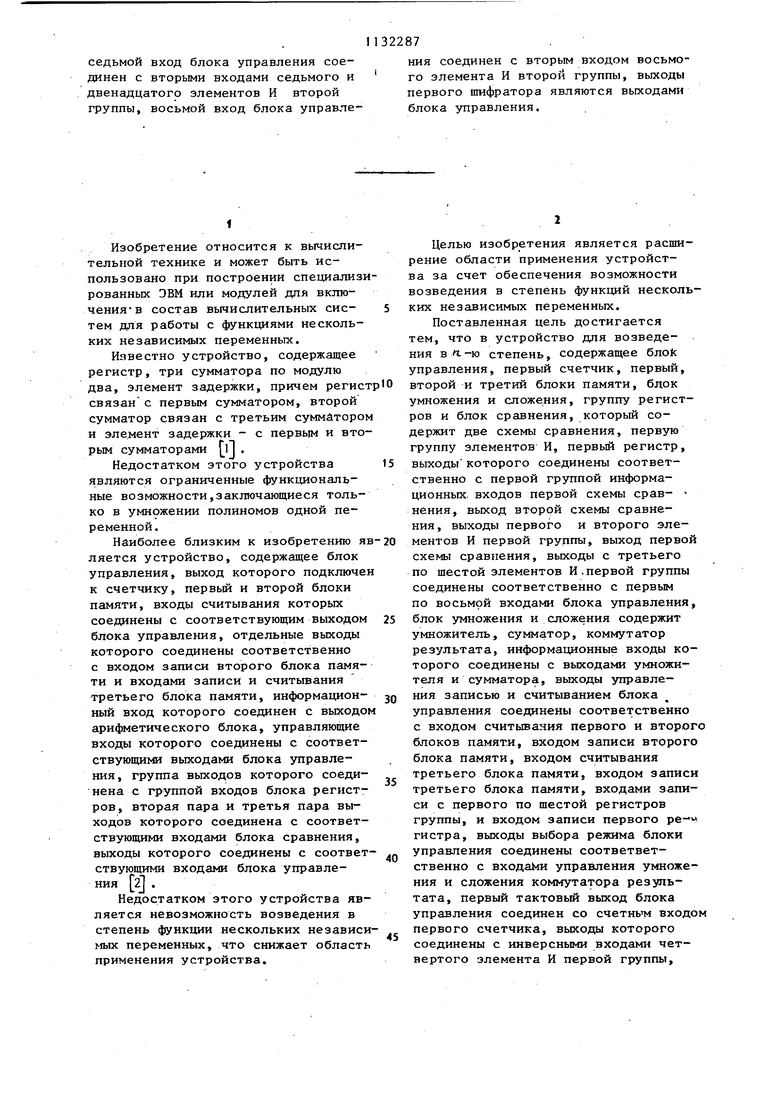

Изобретение относится к вычислительной технике и может быть использовано при построении специализ рованных ЭВМ или модулей дпя включения в состав вычислительных сиетем для работы с функциями нескольких независимых переменных. Известно устройство, содержащее регистр, три сумматора по модулю два, элемент задержки, причем регис связанс первым сумматором, второй сумматор связан с третьим суммйторо и элемент задержки - с первым и вто рым сумматорами П . Недостатком этого устройства являются ограниченные функциональные возможности,заключающиеся только в умножении полиномов одной переменной. Наиболее близким к изобретению я ляется устройство, содержащее блок управления, выход которого подключе к счетчику, первьй и второй блоки памяти, входы считывания которых соединены с соответствующим выходом блока управления, отдельные выходы которого соединены соответственно с входом записи второго блока памяти и входами записи и считьшания третьего блока памяти, информационный вход которого соединен с выходо арифметического блока, управляющие входы которого соединены с соответствующими выходами блока управления, группа выходов которого соединена с группой входов блока регистров, вторая пара и третья пара выходов которого соединена с соответствующими входами блока сравнения, выходы которого соединены с соответ ствующими входами блока управления 2J . Недостатком этого устройства является невозможность возведения в степень функции нескольких независи мых переменных, что снижает область применения устройства. Целью изобр1етения является расширение области применения устройства за счет обеспечения возможности возведения в степень функций нескольких независимых переменных. Поставленная цель достигается тем, что в устройство для возведения в п. -ю степень, содержащее блok управления, первый счетчик, первый, второй и третий блоки памяти, блок умножения и сложения, группу регистров и блок сравнения, который содержит две схемы сравнения, первую группу элементов И, первый регистр, выходы которого соединены соответственно с первой группой информационных, входов первой схемы срав- нения, выход второй схемы сравнения, выходы первого и второго элементов И первой группы, выход первой схемы сравнения, выходы с третьего по шестой элементов И.первой группы соединены соответственно с первым по восьмой входами блока управления, блок умножения и сложения содержит умножитель, сумматор, коммутатор результата, информационные входы которого соединены с выходами умножителя и сумматора, выходы управления записью и считыванием блока управления соединены соответственно с входом считывания первого и второго блоков памяти, входом записи второго блока памяти, входом считывания третьего блока памяти, входом записи третьего блока памяти, входами записи с первого по шестой регистров группы, и входом записи первого ре-« гистра, выходы выбора режима блоки управления соединены соответветственно с входами управления умножения и сложения коммутатора результата, первый тактовый выход блока управления соединен со счетньм входом первого счетчика, выходы которого соединены с инверсными входами четвертого элемента И первой группы. 3 первая и вторая группы информационных входов второй схемы сравнения соединены соответственно с выходами пятого и шестого регистров группы, информационные входы регистров группы с первого по четвертый объед нены и соединены с выходом третьего блока памяти и информационным входом второго блока памяти, информационный вход третьего блока памяти соединен с выходом коммутатора резуль тата, введены счетчик номера переменной, коммутатор операндов, первы второй и третий формирователи адреса, причем первый формирователь адреса содержит вычитакящй счетчик, второй регистр, первый коммутатор, первая группа информационных входов которого соединена соответственно с разрядными выходами вычитающего счетчика и инверсными входами первого элемента.И первой группы, вто рой формирователь адреса содержит реверсивный счетчик, третий регистр второй коммутатор, первая группа информационных входов которого соединена соответственно с разрядными выходами реверсивного счетчика, инверсными .входами второго элемента И первой группы и разрядными входами третьего регистра, третий формирователь адреса содержит второй счетчик, третий и четвертый коммутаторы, первый элемент ИЛИ, выход которого соединены с входом записи второ го счеФчика, разрядные выходы которого соединены с первой группой информационных входов третьего коммутатора, разрядными входами первого регистра, второй группой информационных входов первой схемы сравнения и информационными входами пятого и шестого регистров группы, первый и , второй управляющие входы первого, второго и третьего коммутаторов соединены с первым и вторым выходами задания адреса блока управления, выходы управления записью которого сое динены соответственно с входами записи вычитающего счетчика, реверсивного счетчика, счетчика номера переменной и третьего регистра, тактовый вход вычитакщёго счетчика, иммитирую щий вход реверсивного счетчика, вычитающий вход реверсированного счетчика, тактовый вход второго счет чика и вйчйтающий вход счетчика номера переменной соединены соответственно с группой тактовых выходов бло 87 . 4 ка управления, выход сброса которого соединен с входами сброса реверсивного счетчика и второго счетчика, выходы группы управляющих выходов блока управления соединены соответственно с первым и вторым управляющими входами четвертого коммутатора и первым и вторым управляющими входами коммутатора операнд, первый и второй управляющие входы четвертого коммутатора соединены с входами первого элемента ИЛИ, первая и вторая группы информационных входов коммутатора операндов соединены соответственно с выходами первого и второго блоков памяти, третья и четвертая группы информационных входов коммутатора операндов соединены соответственно с выходами третьего и четвертого регистров группы и инверсными входами пятого и шестого элементов И первой группы, первый и второй выходы коммутатора операндов соединены соответственно с первым и вторым входами умножителя и сумматора, выходы счетчики номера переменной соединены соответственно с второй группой информационных входов первого, второго и Третьего коммутаторов, выходы кото.рых соединены соответственно с адресными входами первого, второго и третьего блоков памяти, разрядные выходы первого и второго регистров группы соединены соответственно с первой и второй группами информационных входов четвертого коммутатора, блока управления содержит генератор импульсов, счетчик циклов, дешифратор, второй элемент ИЛИ, первьш и второй шифраторы, вторую группу элементов И,причем выход генератора импульсов соединен с тактовым входом счетчика циклов, выходы которого соединены соответственно с выходами дешифратора, выходы которого соединены соответственно с входами первого шифратора, первая группа выходов дешифратора соединена соответственно с первыми входами элементов и второй группы, выходы которых соединены соответственно с входами первой группы входов второго шифратора и первой рруппой входов второго элемента ИЖ, вторые группы входов которых соединены соответственно с выходами второй группы выходов дешифратора, выходы с первого поП-1 второго шифратора соединены соответственно с информационными входами счетчика циклов, установочный вход которого соединен с выходом второго элемента ИЛИ, П-й выход второго шифратора соединен с входом останова генератора импульсов, первый вход блока управления соединен с вторыми входами первого и инверсным Ьходом десятого элементов И второй группы, второй вход блока управления соединен с инверсным входом второго элемента И второй группы, третий вход блока управления соединен с инверсным входом третьего элемента И второй группы, четвертый вход блока управления соединен с вторыми входами четверто о, девятого и тринадцатого элементов И второй группы, пятый вхо блока управления соединен с инверсны ми входами пятого и четьфнадцатого элементов И второй группы и вторым входом одиннадцатого элемента И второй группы, шестой вход блока управления соединен с вторым входом шестого элемента И второй группы, седьмой вход блока управления соединен с вторыми входами седьмого и двенадцатого элементов И второй груп пы, восьмой вход блока управления соединен с вторым входом восьмого элемента И второй группы, выходы первого шифратора являются выходами блока управления. На фиг. представлена структурная схема устройства возведения в степень; на фиг. 2 - структурная схема блока управления; на фиг. Зй, В, В - структурные схемы формирователей адреса; на фиг. 4 - структурная схема счетчика номера переменной; на фиг. 5 - структурная схема блока сравнения; на фиг. 6 - схема блока умножения и сложения. Устройство (фиг.1) содержит блок управления, первый счетчик 2, второ и третий формирователи адреса 3,4,5 соответственно, счетчик номера пере менной 6, первый, второй и третий блоки памяти 7, 8, 9, соответственно труппу регистров 10, коммутатор one рандов 11, блок умножения и сложения 12, блок сравнения 13. Блок управления 1 (фиг.2) предна значен для вьфаботки управляющих си налов в соответствии с алгоритмом работы и содержит генератор импульсов 14, счетчик циклов 15, дешифратор 16, группу элементов И 17, шиф;7. ратор 18, элемент ИЛИ.19, шифратор 20, причем число выходов дешифратора 16 равно числу шагов алгоритма работы, порядок нумерации выходов дешифратора 16 соответствует порядку нумерации шагов алгоритма. Формирователи адреса (фиг.3q,5,1,) предназначены для формирования адресов коэффициентов и показателей степеней переменных в соответствующих блоках памяти и содержат соответственно первый формирователь адреса (фиг.3,а} - вычитающий счетчик 21, регистр 22, коммутатор 23, второй формирователь адреса (фиг.3,&) - реверсированный счетчик 24, регистр 25, коммутатор 26; третий формирователь адреса (фиг.З,Ь) - счетчик 27, коммутатор 28, элемент ИЛИ 29, коммутатор 30. Счетчик номера переменной (фиг.4) предназначен дпя хранения числа переменных и изменения номера переменной и содержит вычитающий счетчик 31 и регистр 32. Блок сравнения (фиг.5) содержит схему сравнения 33, элементы И 34, 35, регистр 36, элементы И 37-40, схему сравнения 41, причем схемы сравнения 33 и 41 предназначены для выработки сигналов при равенстве информации поступившей на первую и вторую группы входов, элементы И вырабатывают сигналы при нулевой информации на входах. I Блок умножения и сложения 12 (фиг.6) содержит, умножитель 42, сумматор 43, коммутатор результата 44. В соответствии с нумерацией выходов дешифратора 16 на его выходах вырабатываются управляющие сигналы, которые соответствуют шагам алгоритма, на которых осуществляется безусловный переход к другим шагам алгоритма, подключены к шифратору 18 и соответствующим входам элемента ИЛИ 19; выходы дешифратора 16, которые соответствуют шагам алгоритма, на которых проверяется, условие перехода к другим шагам алгоритма, соединены с соответствующими входами второй группы элементов 17, остальные выходы, которые соответствуют шагам алгоритма, на которых одновременно вырабатываются сигналы управления, подключены к шифратору 20. Переход к другому не по порядку шагу алгоритма осуществляется следующим образом. При появлении сигнала 7 на одном иэ входов шифратора 18 на его выходах формируется, код соответ ствующего номера шага, который поступает на информационный вход счет чика 15, а так как данный вход шифратора 18 соединен с соответствукщи входом элемента ИЛИ 19, то на выход элемента ИЛИ 19 появляется сигнал, который поступает на вход записи Ьчетчика 15, таким образом происходит запись кода номера шага алгорит ма, к которому необходимо сделать переход, в счетчик 15. Коммутаторы в формирователях адреса устроены таким образом, что по сигналу на входе 1 пропускается информация с первой группы входов, а по сигналу на. входе 2-е первой и с второй группы входов. Количество выходов коммутаторов равно суммарному количеству входов в первой и второй группе, В основу работы устройства положен следующий алгоритм возведения в степень полинома. Пусть необходимо возвести в степень многочлен, который представляется в виде полинома т I -|И г V -tH . р(х«,Х2,ХЗ...ХпД feCi.n Ч j ) - c.Xt......C2Xl 5(24.,. :...XnH... + c Xl x2... где С, - коэффициенты многочлена; Х; - независимые переменные; k. - показатели степеней соот ветствующих переменных; m - число слагаемых; п - число переменных; N - показатель степени многочл на. Необходимым условием выполнения алгоритма является расположение переменных в каждом слагаемом в одном и том же порядке. Количество переменных в слагаемых должно быть равным, при этом недостающие переменные добавляются с нулевыми показателями степеней, . Полино ; представляется в виде таблицы данных. 87 С 1 k,j lt,2 43 k С 2 kj, kj,j k j ,,, k С k, k k, .,. k Таблица данных исходного полинома в виде массива f С,, , i 1,m; j 1,ft записывается в первый блок памяти в виде массива CD-, ь- , i 1,9 , j 1,п во второй блок памяти; Tii . Производится умножение полиномов {с;, k-J и , , при этом по порядку, начиная с m-го слагаемого каждое слагаемое полинома Ц) 1 умножается на все слагаемые (начиная с -го) полинома {D , bj; J ; при умножении двух слагаемых коэффициенты перемножаются, а показатели степеней соответствующих переменных складываются, результирующий полином в виде массива F , Г-j, 1 1, р; j 1 ,п записывается в третий блок памяти. Производится приведение подобных слагаемых в полиноме F;,EЛ., при этом показатели степеней переменных каждого слагаемого, по порядку начиная с первого, сравниваются с показателями степени соответствующих переменных остальных слагаемых; если в двух слагаемых показатели степеней соответствующих переменных равны, то коэффициенты данных слагаемых складываются, при этом результирующий коэффициент присваивается одному из данных слагаемь1х, коэффихщент другого слагаемого обнуляется, слагаемые с нулевыми коэффициентами при выборке игнорируются, Массив данных (р, «j J ,n из третьего блока памяти переписывается на место массива {D,, Ь;|1 ,; ,n во второй блок памяти, при этом данные слагаемых с нулевьп4И коэффициентами не переписываются. Анализируется счетчик показателя степени полинома, значение которого первоначально устанавливается 9 j1-2. Если значение счетчика на ну1левое, то оно уменьшается на единицу, и осуществляется переход к шагу 3; если нулевое, устройство заканчивает работу, при этом результа возведения в степень хранится во вт ром блоке памяти. Устройство работает следующим образом. Предварительно массив данных исходного полинома как массив fcukj-L ,m; ,n заносится в блок памя ти 7 как массив fD| , , , j l,n;- m в блок памяти 8, причем адреса коэффициентов адр Cj i , ,m; адр.1),г j , i 17 адреса показателей степеней - адр. а адр.Ь, ) I 1 , В.счетчик 21 и регистр 22 заносится адр. CJ т, в счетчик 24 и регистр 25 заносится адр.1), 5 , в счетчик 31 и регистр 32 заносится значение j п, в счетчик 42 - чис . Дальнейшая работа устройства осуществляется в соответствии с шагами алгоритма работы блока управления 1; по щагам 1-10 алгорит ма происходит умножение полиномов С , D|, b;jJ с получением результирующего полинома в блоке памяти 3 причем адр. F- адр. ij, , j In. Шаг 1. Вырабатываются управляющие сигналы на выходах блока управления 1, 14, 24, 26, 9, 17, по кото , рым в формирователе адреса 5 изменяется значение счетчика 27 на +1, таким образом адр. Fj : адр. F +1 на выходах 1 формирователей 3, 4, 5 адреса устанавливаются адреса коэффициентов адр. С , адр Л , адр Fj из блоков 7 и 8 памяти считываются коэффициенты С| и D, , которы через коммутатор поступают в арифме тический блок и умножаются, результат F записьюается в блок памяти (в первом умножении адр F{ 1, адр. .С |«; адр. Г; ; F, ) . Шаг 2. Вырабатываются сигналы на выходах 2, 14; 24, 27, 17, по ко торым устанавливаются адреса адр. V;j( , адр.Ь; , aдp.6;J , из блоков 7 и 8 памяти считываются 1, иЬ , которые через коммутатор поступают в арифметический блок и складываются, результат записывается в блок памяти 9 (в первом сложении адр.1с;; mn; адр.Ь;,- Jn , aMl«-4j адр. 1 ,P-in 710 Шаг 3. Вырабатывается сигнал на выходе 13 блока управления 1, по которому изменяется значение счетчика 31 на -1 ,- таким образом j j -1 . Шаг 4.. Анализируется значение счетчика 31 и если j 0, то на вызюде 5 блока сравнения вырабатывается сигнал, по которому в блоке управления осуществляется переход к шагу 5 алгоритма, а если j 0, то к шагу 2. Шаг 5. Вырабатываются сигналы на выходах 7, 12 блока управления 1, по которым содержимое регистра 32 переписьшается в счетчик 31 , таким образом J П; значение счетчика 24 изменяется на -1, и адр. D; адр. D; -1. Шаг 6. Анализируется значение адр. 33 счетчика 24, если адр. Р{ О, то осуществляется переход к шагу 7, если адр.Г); , то к шагу 1 алгоритма. - . Шаг 7. Вырабатываются сигналы на выходах 4, 5 блока управления, по которым значение счетчика 24 уменьшается на -1, таким образом адр. С адр. с; -1, содержимое регистра 26 переписывается в счет- чик 2.4 и адр. D; 5 , Шаг 8. Анализируется значение адр. С счетчика 21, если адр. С 0, то осуществляется переход к шагу 9, если адр С. , к шагу 1 алгоритма. Шаг 9 Вырабатываются сигналы на вькодах 3, 28 блока управления, по которым содержимое регистра 22 переписьшается в счетчик 31, т.е. адр С m содержимое счетчика 27 переписывается в регистр 36, т.е. BSi,: адр. f| р. Шаг 10. Вырабатывается сигнал на выходе 8 блока управления, по которому содержимое счетчика 24 и регистра 22 обнуляется, т.е. адр. D адр.Р; 0. По шагам 11-34 алгоритма осуществляется приведение подобных слагаемых в полиноме , . Шаг 11. Выарабать&аются на выходах 9, 1, 16, 20, 18, по которым значение счетчика 27 изменяется на +1, т.е. адр, FJ адр. F,+l, устанавливается адр. Fj, по которому из блока 9 памяти считывается коэффициент F, и записывается в первый регистр группы регистров 10; значение счетчика 27 переписывается в регистр, т.е. Р1 , .Р, в первом считьш иии адр. F,, , ). Шаг 12. Анализируется равенство значений адр. F, счетчика 27 и значения р регистра 26 в блоке сравнения, если адр. F| р, то осущест вляется переход к шагу 35, если адр.; р, то к шагу 13. . Шаг 13. Анализируется значение Fj, еслиР 0, осуществляется переход к шагу 11, еслиР jO, к шагу 14 Шаг 14. Вырабатьтаются сигналы н выходах блока управления 2, 16, 22 по которым устанавливается адр. так как из блоков 9 п мяти считывается и записывается второй регистр группы регистров 10. Шаг 15.Вырабатьшаются сигналы на выходах 9, 1, 16, 21, по.KOTopWi значение счетчика 27 изменяется на +1 ; устанавливается адр. f, ; считывается F{ и записьюается в тре тий регистр группы регистров. Шаг 16. Анализируется значение FJ в третий регистр, если f 0, то осуществляется, переход к шагу 15, если F- 0, k шагу 17. : Шаг 17, Вырабатьш ают ся сигналы на выходах 2, 16, 23 блока управле ния, но которым устанавливается адр.С); 1п , так как J п; считывается Bjfl и записьшается в четве тый регистр группы регистров 10. Шаг 18. Анализируется равенство значений регистров второго и четве того; если они равны, то осуществл ется переход к шагу 22, е.сли нет, к шагу 19, т.е. сравниваются показатели степени И -ой переменной в двух слагаемых, например, и f Шаг 19. То же, что и в шаге 12, только если адр. F, И, делается переход к шагу 20, если адр. i р к шагу 15. Шаг 20. Вырабатывается сигнал н выходе 10 блока управления, по которому значению адр F, в счетчике 27 присваивается значение пятого регистра группы регистров 10. Шаг 21 переход к шагу 11. Шаг 22. Вырабатываются сигналы выходах 19, 13, 2, 16, 23. блока управления, по которым значение адр. Fj в счетчике 27 переписывает ся в шестой регистр; значение j в счетчике 31 изменяется на -1; уста навливается адр. р;; ; считьюается ,: и записывает в четвертый регистр . Шаг 23. Вырабатьшаются сигналы на выходах 1.0, 2, 16, 22 блока управления, по которым значению адр. Г{ в счетчике 27 присваивается значение первого регистра; устанавливается адр. ;: ; считьшается и записывается во второй регистр. Шаг 24. То же, что ив шаге 18, только если равенство, осуществляется переход к шагу 25, если нет, к шагу 33, т.е. если в шаге 18 то здесь анализируется /({.-(n-i} сли равенство вып.олняется, то затем анализируется Нп-а) ) Чп-Э1 «(и-Я Шаг 25. То же, что и в шаге 4, только если , осуществляется переход к шагу 38, если , к шагу 26. Шаг 26. Вйрабатьшается сигнал на выходе 11 блока управления, по которому.значению адр. F| в счетчике 27 присвается значение шестого регистра группы регистров 10. Шаг 27. Переход к шагу 22. Шаг 28. Вырабатываются сигналы на входах 25, 27, 1, 17, 12 блока управления, по которым значения первого и третьего регистров через коммутатор поступают в блок умножения и сложения и складьшаются, устанавливается адр. , по которому записьшается резупьтат сложения в блок памяти 9, содержимое регистра 32 переписьтается в счетчик 31, т.е. j; И. Шаг 29. Вьфабатываются сигналы на выходах 16, 20 блока управления по которым устанавливается адр,F; ; считывается F: и записывается в регистр группы регистров Ю. Шаг 30. Вьфабатываются сигналы на выходах 11,1, 17 блока управления,по которым значению адр Fv в счетчике 27 присваивается значение шестого регистра устанавливается адр. FJ и производится запись в блок 9 памяти, т.е. коэффициент F по адресу адр. F, обнуляется. Шаг 31; То же, что и в шаге 20. Шаг 32. Переход к шагу 14. Шаг 33. Вырабатываются сигналы на выходах II, 12 блока управления, по которым значеИию адр, F в счетчик 27 13 присвается значение шестого регистра, значению j в счетчике 31 - значение регистра 32, т.е. j W. . Шаг 34. Переход к шагу 15. Шаг 35. То же, что и в шаге 10. По шагам 36-47 алгоритма осущест вляется перезапись полинома из блока 9 памяти в блок 8 памяти на место полинома Гв-, bjl . Шаг 36. й)1рабатьгоаются сигналы н выходах 9, 1, 16, 20 блока управления, по которым значение счетчика 2 изменяется на +1, устанавливается адр. Р и считывается коэффициент F который записывается в первый регис (в первом считывании адр. F 1, Pl Fl) .Шаг 37. То же, что и в шаге 13, только если Fj 0, делается перевод к шагу 38, если F; , к шагу 39. Шаг 38. То же, что и в шаге 12, только если адр. FJ 0 , делается переход к шагу 45, если адр. э Р к шагу 36. Шаг 39. Вырабатываются сигналы на выходах 1, 16, 6, 15 блока управ ления 1, по которым значение счетчика 24 изменяется на +1, т.е. адр. Р, адр. D,., , устанавливаетс:я адр. F и адр D , из блока 9 памяти считывается Р. и записывается в блок 8 памяти. Шаг 40. Вырабатываются сигналы н выходах 2, .16,-15 блока управления 87 по которым устанавливаются адр. адр Ь ; считывается , из блока 9 и записывается в блок 4 памяти 8 IP (в первом считывании Ь ,, ; затем Ьц„.,, .,, и т.д.) . Шаг 41. То же, что и в шаге 3. Шаг 42. То же, что и в шаге 4, только если j 0, делается переход к шагу 43, j 0, к шагу 40. Шаг 43. То же, что и в шаге 12, только если адр. F D, делается переход к шагу 45, если адр. Г О, к шагу 44. Шаг 44. Вырабатывается сигнал на выходе 12 блока управления 1, по которому значению j в счетчике 31 присваивается значение регистра 32, т.е. j п. Шаг 45. Переход к шагу 36. Шаг 46. Вьфабатываются сигналы на выходах 29, 30 блока управления 1, по которым изменяется значение счетчика 2 на -1; значение адрР в счетчик 24 переписывается в регистр 25. Шаг 47. Анализируется значение счетчика 2, если оно не нулевое осуществляется переход к шагу 1, если нулевое - конец работы устройства. Введение в устройство трех формирователей адреса, коммутатора, счетчика номера переменной позволяет получить возможность возводить в степень функции нескольких независимых переменных, т.е. расширило область применения устройства.

5

иг.З

1

Фаг.if

Фиг.5

«2

iffi

7

1Л

Фиг.б

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для умножения полиномов | 1975 |

|

SU538364A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для умножения | 1978 |

|

SU742934A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-30—Публикация

1982-09-24—Подача