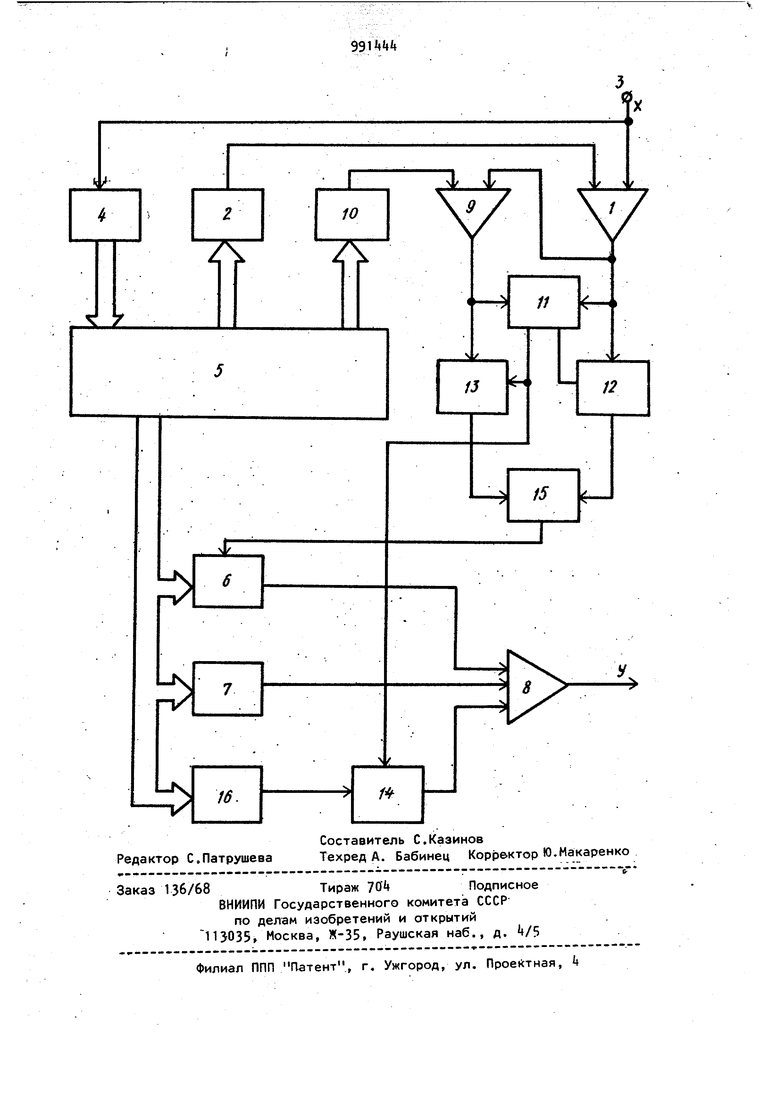

(ЗА) . УСТРОЙСТВО для ВОСПРОИЗВЕДЕНИЯ Изобретение относится к автоматике и вычислительной техинке и может найти применение при воспроизведении нелине йных функций аналоговых сигналовИзвестно устройство для воспроизведения функций, содержащее компараторы, счетчик, блок памяти, цифроаналоговые Преобразователи, множительный блок и сумматоры 13 . Известно также устройство для вос произведения функций, содержащее входной преобразователь, блок адреса ции, блок памяти, инвертор, цифроаналоговые множительные блоки и сумматор 2 . Недостатком известных устройств, является пониженная точность воспроизведения функций из-за возрастания погрешностей перемножения постоянных сигналов на малые аналоговые сигналы при значениях аргумента функции близ ких к.узловым значениям аргумента. ФУНКЦИЙ Наиболее близким к предлагаемому является устройство для воспроизведения функций, содержащее первый сумматор, соединенный первым входом с выходом первого цифро-аналогового преобразователя, а вторым входом - с шиной ввода аргумента и с входом аналогоцифрового преобразователя, подключенного выходами к адресным входам блока памяти, соединенного первой и второй группами выходов с цифровыми входами цифро-аналогового множительного блока и второго цифро-аналогового преобразователя, подключенных выходами к первому и. второму входами, второго сумматора, выход которого .является выходом- устройства, причем выход первого сумматора соединен с аналоговым входом цифро-аналогового множительного блока, а цифровые входы первого цифроаналогового преобразователя подключены к выходам аналого-цифрового преобразователя |;33 . Недостатком устройства является пониженная точность воспроизведения функций, что обусловлено наличием большой погрешности цифро-аналогового множительного блока при малых зна чениях сигнала на его аналоговом вхо де. Цель изобретения - повышение точности воспроизведения функций. Цель достигается тем, что в устро ство для воспроизведения функции, содержащее первый сумматор, соединен ным первым входом с выходом первого цифро-аналогового преобразователя, а вторым входом - с шиной ввода аргумента и с входом аналого-цифрового преобразователя, подключенного выходами к адресным входам блока памяти, соединенного первой и второй группами выходов с цифровыми входами цифро-аналогового множительного блока и второго цифро-аналогового преоб разователя, подключенных выходами к первому и второму входам второго сум матора, выход которого является выходом устройства, дополнительно введены третий и четвертый цифро-аналоговые преобразователи, ключи, блок сравнения. Рлок выделения максимума и трет.й сумматор, соединенный первы входом с выходом третьего цифро-аналогового преобразователя, вторым входом - с выходом первого сумматора первым входом блок« сравнения и с си нальным входом первого ключа, а выходом - с сигнальным входом второго ключа и с вторым входом блока сравне ния, подключенного прямым выходом к управляющему входу первого ключа, а инверсным выходом - к управляющим входам второго и третьего ключей, причем выходы первого и второго ключей соединены с входами блока выделения максимума, подключенного выходом к аналоговому входу цифро-аналог вого множительного блока, а третий вход второго сумматора соединен с вы ходом третьего ключа, подключенного сигнальным входом к выходу четвертог цифро-аналогового преобразователя, а цифровые входы первого, третьего и четвертого цифро-аналоговых.преобразователей соединены с соответствующим группами выходов блока памяти. На чертеже изображена блок-схема устройства для воспроизведения функц Устройство содержит первый сумматор 1, соединенный первым входом с выходом первого цифро-аналогового преобразователя 2, а вторым входом с шиной 3 ввода аргумента и с входом аналого-цифрового преобразователя k. Преобразователь k подключен выходами к адресным входам блока 5 памяти, соединенного первой и второй группами выходов с цифровыми входами цифроаналогового множительного блока 6 и второго цифро-аналогового преобразователя 7. Выходы блока 6 и преобразователя 7 подключены к первому и второму входам второго сумматора 8, выход которого является выходом устройства. Третий сумматор 9 соединен первым входом с выходом третьего цифро-аналогового преобразователя 10, вторым входом - с выходом сумматора 1 , первым входом блока 11 сравнения и с сигнальным входом первого ключа 12, а выход - с сигнальным входом второго ключа 13 и с вторым входом блока 11 сравнения. Блок 11 подключен прямым выходом к управляющему входу ключа 12, а инверсным выходом - к управляющим входам второго и третьего ключей 13 и 1. Выходы ключей 12 и 13 соединены с входами блока 15 выделения Максимума, подключенного выходом к аналоговому входу цифро-аналогового множительного блока 6, Третий вход сумматора 8 соединен с выходом ключа It, подключенного сигнальным входом к выходу четвертого цифро-аналогового преобразователя 16. Цифровые входы преобразователей 2, 10 и 16 роединены с соответствукщими группами выходов блока(5 памяти. Устройство работает следующим образом. Входной сигнал X преобразуется аналого-цифровым преобразователем в некоторое число i, в соответствии с которым блоком 5 памяти производится выбор значения аргумента х; в i-ом |узле аппроксимации, значения длительности I-го участка аппроксимации d значения функции F(x) в i-ом узле аппроксимации и ее максимального приращения Apf на i-OM участке аппроксимации (ДГ d-(f ) и значения тангенса d угла наклона на i-ом участке аппроксимации. Выбранные значения , ( F(), ид;.- по соответствующим выходам блока 5 передаются на цифровые входы цифро-аналоговых преобразователей 2, 10, 7, 16 и цифро-аналогового множительного блока 6, На выходе сумматора 1 образуется сигнал . ха на выходе сумматора Я . сГх| - . Сигналы с выходов сумматоров 1 , 9 поступают на входы ключей 12-13 и блока It сравнения. Если величина Л х|7ДХ; ТО на прямом выходе блока j/l .. - З11 сравнения формируется сигнал, кото .рым открывается клюм 12, а на инверсном выходе блока 11 - сигнал, которым закрываются ключи 13 и I. В этом случае сигнал на выходах ключей 13 и 1А равен нулю, а сигнал на выходе клю ча 12 равен выходному сигналу сумматора 1. Следовательно, на выход блока 15 выделения максимума передается сиг нал с выхода сумматора 1, что приводит к формированию на выходе Цифроаналогового множительного блока 6 ана логового сигнала приращения функции ду: cL . Так как на выходе ключа k сигнал .равен нулю, то на входы сумматора 8 поступают слагаемые F(x|) иду , -что приводит к появлению на его выходе сигнала У Г{х,.) +-Ду1, которым и определяется функция на Ч-ом участке аппроксимации. Следовательно, при значениях входного сигнала х, значительно боль ших граничного значения , при формировании, приращения функции произво дится умножение кода постоянной величины на аналоговый сигнал, значительно больший нуля, что позволяет получать результат с высокой точностью с помощью цифро-аналогового множительного блока 6. При значениях входного сигнала х близких к величине , сигнал на выходе сумматора 9 по модулю больше сигнала на выходе сумматора 1, Тогда сигнал с инверсного выхода блока 11 сравнения открывает цепи прохождения сигналов от сигнальных входов ключей 13 и Ti на их входы, а сигнал на прямом выходе блока 11 закрывает цепи прохождения сигналов с сигнальт ного входа на выход ключа 12. Если в качестве блока 11 сравнения использовать усилитель с большим коэффициентом усиления и дифференциальным входом, то, используя пассивные схем реализации блока 15 выделения максимума, нетрудно обеспечить передачу на выход блока 15 выделения, максимума трицательного сигнала с выхода сумматора 3 ДХ - rfx.. В этом случае на выходе цифроаналогового множительного блока 6 формируется сигнал &yf f Л 4 - oL4 который, поступая на вход сумматора 8 совместно с сигналами ГСх) с выхода: цифро-аналогового преобразователя 7 и F с выходацифро-аналогового преобразователя 16, приводит к появлению на выходе сигнала у Р{х;) + ДР ( сГ-х + F(xi) . которым определяется функция на -ом участке аппроксимации. Так как величина , то вновь при выполнении операции умножения постоянного сигнала i,-на величину О с помощыо цифрог-аналогового множительного блока 6 получается результат с высокой точностью. Таким образом, предлагаемое устройство для воспроизведения функций позволяет обеспечить высокую точность воспроизведения функций при произвольных значениях х, принадлежащих интервалам аппроксимации, 4fo и определяет технико-экономическую эффект тивность возможного применения устройства. Формула изобретения Устройство для воспроизведения функций, содержащее первый сумматор, соединенный первым входом с выходом первого цифро-аналогового преобразог, вателя а вторым входом - с шиной ввода аргумента и с входом аналогоцифрового преобразователя, подключенного выходами к адресным входам .блока Памяти, соединенного первой и второй группами выходов с цифровыми входами цифро-аналогового множительного блока и второго цифро-аналогового преобразователя, подключенных выходами к первому и второму входам второго сумматора, выход которого является выходом устройства, отличак ще6с я тем, что, с целью повышения точности воспроизведения функций в него дополнительно введен; 1 третий и четвертый цифро-аналоговые преобразователи, ключи, блок сравнения, блок выделения максимума и третий сумма7 .9 тор, соединенный первым входом с выходом третьего цифро-аналогового пре образователя, вторым входом - с выходом первого сумматора, первым входом блока сравнения и с сигнальным входом первого ключа, а выходом - с сигнальным входом второго ключа и с вторым входом блока сравнения, подкл ченного прямым выходом к управляюЧцему входу первого ключа, а инверсным выходом - к управляющим входам второго и третьего ключей, примем вы ходы первого и второго ключей соединены с входами блока выделения максимума, подключенного выходом к аналоговому входу цифро-анйлогового мно дительного блока, а третий вход второго сумматора соединен с выходом третьего ключа, подключенного сигнальным входом к выходу четвертого цифро-аналогового преобразователя, а цифровые входы первого, третьего и четвертого цифро-аналоговых преобразователей соединены с соответствующими группами выходов блока памяти. Источники информации, принятые во вниманиее при экспертизе 1.Патент США If 3373273, кл. 235-197, опубл, 1968. 2.Гинзбург С.А., Любарский Ю.Я. Функциональные преобразователи с анэлого-цифровым представлением информации. И., Энергия, 1973, с.38. 3.Корн Г., Корн Т. Электронные аналоговые и аналого-цифровые вычислительные машины. Н., Мир, 1968, т.2, с.216, рис,11.31А (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1983 |

|

SU1166147A1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1126975A1 |

| Гибридный функциональный преобразователь | 1987 |

|

SU1464180A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Гибридный функциональный преобразователь | 1982 |

|

SU1076918A1 |

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Полигональный аппроксиматор | 1981 |

|

SU1005089A1 |

| Функциональный преобразователь | 1979 |

|

SU830430A1 |

| Цифро-аналоговый функциональный преобразователь | 1980 |

|

SU895973A1 |

| Цифро-аналоговый функциональный преобразователь | 1978 |

|

SU706856A1 |

Авторы

Даты

1983-01-23—Публикация

1981-02-12—Подача