1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах программного управления исполнительными органами для преобразования числовой информации о приращениях координат в последовательность выходных управляющих импульсов.

Известен линейный интерполятор, содержащий генератор импульсов, делитель частоты, счетчики, блоки сравнения, регистры приращений, в котором в результате преобразования кодов приращений на выходах получаются унитарные коды, частоты следования импульсов которых прямо пропорциональны кодам приращений 1 ,

Недостаток этого интерполятора состоит в том, что он неоднозначно преобразует в частоту следования выходных импульсов коды большего приращения. Кроме того, он не позволяет так регулировать частоту следования выходных импульсов канала, соответствующего большему приращению, чтобы отношение частот следования импульсов осталось равным отношению кодов соответствующих приращений.

Наиболее близким по технической сущности к предлагаемому является генератор векторов, а именно его часть, включающая блок цифровой нормализации кодов приращений, входы которого соединены с выходом цифрового запоминающего устройства кодов приращений, а выходы - с цифровыми входами цифро-аналоговых преобразователей кодов приращений, и дополнительный цифро-аналоговый преобразователь, входы которого соединены с выходами блока цифровой нормализации, а выход подключен к опорным входам цифро-аналоговых преобразователей кодов приращений.

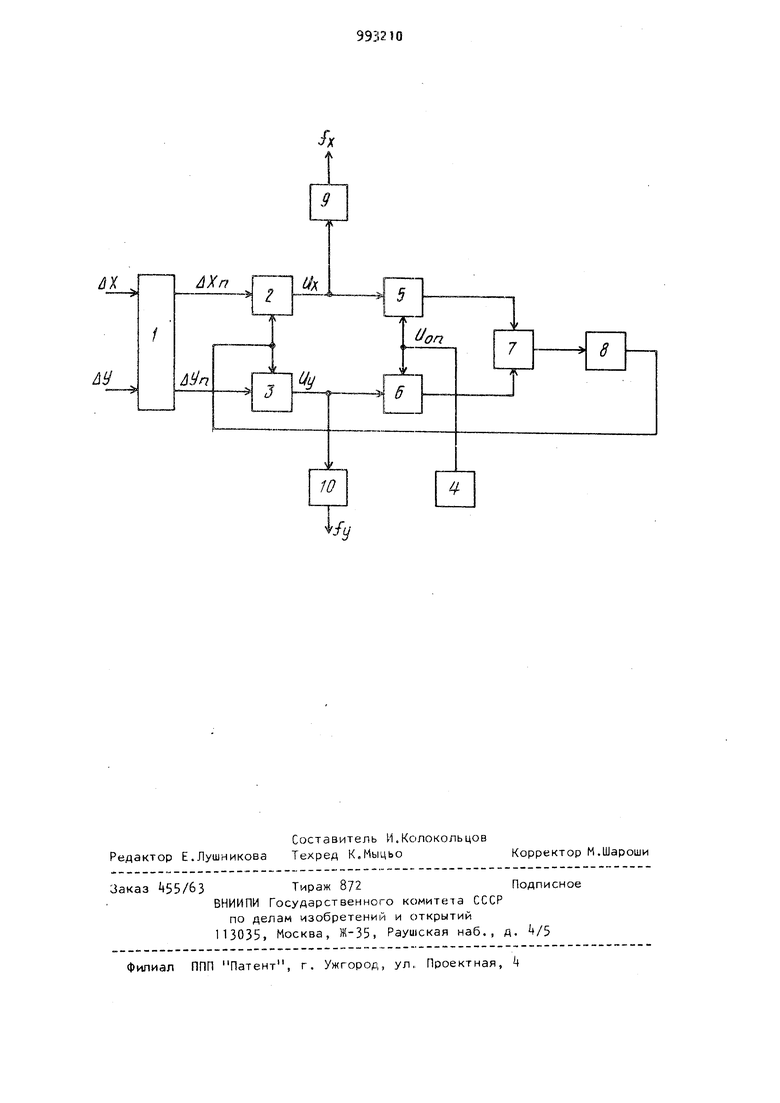

Выходные постоянные напряжения с цифро-аналоговых преобразователей устройства прямо пропорциональны отношению кодов приращений . I9 Однако устройству свойственна неоднозначность постоянного выходного напряжения с выхода-цифро-аналогового преобразователя, соответству ющего большему приращению, при различных кодах последнего. Цель изобретения - получение регулируемой и независимой от кодов большего приращения частоты следования импульсов в канале с большим при ращением, т.е. повышение точности ИНТерполя тора Поставленная цель достигается тем, что линейный интерполятор, содержащий эадатчик опорного напряжения, арифметический блок, подключенный первым выходом через первый цифро-аналоговый преобразователь к входу первого преобразователя напряжение-частота, вторым выходом - через второй цифро-аналоговый преобразователь к входу второго преобразователя напряжение-частота, содержит первый компаратор и последовател но соединенные второй компаратор, элемент ИЛИ и интегратор, подключенный выходом к вторым входам первого второго цифро-аналоговых преобразова телей,, первые входы первого и второго компараторов соединены с выходом задатчика опорного напряжения, второй вход первого компаратора подключен к выходу первого цифро-аналогового преобразователя, выход - к второму входу элемента ИЛИ, а второй вход второго компаратора соединен с выходом второго цифро-аналогового преобразователя. На чертеже представлена структур ная схема линейного интерполятора. Интерполятор содержит арифметиче кий блок 1, первый 2 и второй 3 циф ро-аналоговые преобразователи, зада чик 4 опорного нaпpяжeнияJ первый и второй компараторы 5 и 6,элемент ИЛИ интегратор 8,первый и второйпреобра и второй преобра зователи напряжение .-частота 9 и Ю. Входы блока 1 соединены с выхода ми цифрового запоминающего устройства, у которого информационная раз рядность кодов каждого из приращени равна t двоичным разрядам. Блок 1 осуществляет нормализацию кодов приращений сдвигом их в с рону старших разрядов k раз (прризводит умножение этих кодов на 2 1 1 6-W уги- Ь17и 8 -И И а гл и п - число двоичных разрядов, используемых для записи текущих коов приращений Дхиду соответственно, Коды приращений ix и ду после цифровой нормализации соответствен2 илз Ду-2Ч равны Дх.лх При этом соотношение останется равным дх/ду , а диапазон изменения кодов большего приращения уменьшится от -fHl-OAofZ Ui-.l) Преобразователи 2 и 3 преобразуют цифровые нормализованные коды приращений Дх и ду в выходные постоянные напряжения 0 и U, соответственно пропорциональные этим кодам, а следовательно, и кодам приращений Х и ду , Выходы каждого преобразователя 2 и 3 соединены с входом соответствующего ему компаратора 5 и 6 и преобразователя 9 и 10, имеющих одинаковые зависимости частоты следования выходных импульсов от входного управляющего напряжения. Вторые входы компараторов 5 и 6 соединены с задатчиком k, уровень напряжения UQ которого может быть постоянным или изменятся в процессе работы по заданному закону. Компараторы 5 и 6 сравнивают выходные напряжения с цифро-аналоговых преобразователей U и Uy с опорным напряжением U. Выходы компараторов 5 и 6 подключены к входам элемента ИЛИ, выходы которого подсоединены к входу интегратора 8. Интерполятор работает следующим образом. Из цифрового запоминающего устройства коды приращений х и ду поступают в блок 1, где нормализу преобразователи 2 и 3, опорное напряжение в исходном состоянии равно которых нулю. По сигналу включения цифро-аналоГО13ЫХ преобразователей 2 и 3 начинает работу интегратор 8, напряжение на выходе которого начинает нарастать. Это напряжение подается на опорные входы преобразователей 2 и 3, выходные напряжения которых нарастают до тех пор, пока выходное напряжение, соответствующее большему приращению, не сравняется с величиной заданного опорного напряже5

ния Uofi- После этого срабатывает соответствующий компаратор 5 и 6 и выдает сигнал на элемент ИЛИ 7 который своим выходным сигналом запрещает дальнейшее интегрирование.

Уменьшение выходного напряжения, соответствующего большему приращению на величину гистерезиса компаратора, приводит данный компаратор в исходное состояние, и элемент ИЛИ 7 включает интегратор 8.

Таким образом, напряжение на выходе преобразователя, соответствующее большему приращению, будет поддерживаться равным заданному опорному напряжению с точностью, определяемой величиной гистерезиса компаратора.

Элемент ИЛИ 7 управляет режимом работы интегратора, в зависимости от которого на выходе интегратора поддерживается уровень постоянного напряжения, являющегося опорным для преобразователей 2 и 3, таким, что еслиДх7Лу, то Uy UonUvAfi(), то и,, и,; ,

и Uy UpjjM ,т.е. выходное напряжение

соответствующее большему приращению, поддерживается равным опорному напряжению UQJ . При этом выходное напряжение, соответствующее меньшему приращению, оказывается пропорциональным отношению соответствующих кодов.

Напряжения с выходов преобразователей 2 и 3, поданные на входа преобразователей 9 и 10, преобразуются в унитарные коды, частоты следования импульсов которых f, fu пропорциональны напряжениям U и 1), а частота следования импульсов в канале большего приращения пропорциональна опорному напряжению и„-и не зависит от кода этого приращения. Частота следования импульсов в канале с меньшим приращением пропорциональна отношению соответствующих кодов. Изменение уровня опорного напряжения U дает возможность возникновения уп106

равления максимальной частотой следования управляющих импульсов

Использование предлагаемого линейного интерполятора дает возможность увеличить производительность исполнительных органов, так как частота следования управляющих импульсов по каналу большего приращения на зависит от его кодов, и обеспечить нормальный режим отработки исполнительных органов за счет изменения частоты следования импульсов в канале с большим приращением по определенному закону в начальные моменты времени.

Формула изобретения

с

Линейный интерполятор, содержащий задатчик опорного напряжения, арифметический блок, подключенный первым выходом через первый цифроаналоговый преобразователь к входу первого преобразователя, напряжение-частота вторым выходом - через второй цифро-аналоговый преобразовате к входу второго преобразователя напряжение-частота, отличающийся тем, что, с целью повышения точности интерполятора, он содержит первый компаратор и последовательно соединенные второй компаратор, элемент ИЛИ и интегратор, подключенный выходом к вторым входам первого и второго цифро-аналоговых преобразователей, первые входы первого и второго компараторов соединены с выходом задатчика опорного напряжения, второй вход первого компаратора подключен к выходу первого цифро-аналогового преобразователя, выход - к второму входу элемента ИЛИ, а второй вход второго компаратора соединен с выходом второго цифроаналогового преобразователя.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 551611, кл. G 05 В 19/18, 1975.

2.Авторское свидетельство СССР № +325 3, кл. G 05 В 19/18, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1987 |

|

SU1550475A1 |

| Устройство для вычисления частной производной | 1983 |

|

SU1105913A1 |

| Преобразователь код-частота гармонического сигнала | 1984 |

|

SU1195449A2 |

| Генератор векторов | 1981 |

|

SU1019483A2 |

| Аналого-цифровое устройство для управления токарным станком | 1980 |

|

SU947830A1 |

| Устройство для считывания графической информации | 1973 |

|

SU667976A1 |

| Устройство для измерения импульсной мощности оптического излучения | 1980 |

|

SU918798A1 |

| Преобразователь частоты следования импульсов в напряжение постоянного тока | 1984 |

|

SU1250977A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1980 |

|

SU940213A1 |

| Линейный интерполятор | 1986 |

|

SU1416940A1 |

Авторы

Даты

1983-01-30—Публикация

1979-10-23—Подача