Изобретение относится к вычислительной технике и автоматике} в частности к устройствам отображения графической информации на ЭЛТ«

По основному авте св. № известен генератор векторов, содержащий цифро-аналоговые преобразователи кодов приращений, выходы каждого из которых через соответствующий интегрирующий усилитель подключены к соответствующим входам компаратора, выход которого соединен с управляющими входами интегрирующ х усилителей, цифро-аналоговые преобразователи кодов координат конечной точки вектора, цифровые входы которых соединены с выходами цифровых сумматоров кодов приращений координат, а выходы подключены к входам установки начальных условий интегрирующих усилителей, цмфровой блок нормализации кодов приращений, входы которого соединены с входами кодов приращений.генератора , а выходы - с цифровыми входами цифро-аналоговых преобразователей кодов приращений, и дополнительный цифро-аналоговый .преобразователь, вход которого соединен с управляющим входом блока нормализации кодов приращений, а выход подключен к опорным входам цифро-аналоговых преобразователей кодов приращенийj l

Недостатком такого генератора является трудность обеспечения высокой (порядка 0,1 и Е7ыше) точности изображения векторов в широком диапазоне измения климатических условий. Это объясняется невозможностью обеспечения и поддержс,.)ия равенства постоянных интегрирования каналов генератора векторов из-за разброса номиналов, неточности и нестабильности резисторов и конденсаторов интегрирующих усилителей особенно в том случае, когда величины постоянных интегрирования малы, что имеет место в быстродействующих генераторах.

Разница постоянных интегрирования в каналах X и У приводит к появлению ошибки на стыках векторов, которая увеличивается с увеличением скорости отображения векторов и его длины. Это требует проведения калибровки и подстройки каналов, что обыч но проводится вручную.

Цель изобретения - повышение точности работы генератора векторов

Поставленная цель достигается , тем, что генератор векторов содержит суммирующий усилитель, эталонный и компенсирующий цифро-аналоговые преобразователи, реверсивный счетчик, первый и второй элементы И, первый и второй триггеры, первый к второй элементы задержки и элемент ИЛИ, входы которого соединены с одними из выхо10. дон компаратора, другие выходы которого соединены с одними из входов первого и второго триггеров, другие входы которых соединены с выходом первого элемента задержки и входом

15 второго элемента задержки, выход которого соединен с одним из входов первого и второго элементов И, другие входы которых соединены с выходами первого и второго триггеров,

20.а выходы соединены с входами реверсивного счетчика, выход которого сое™ динён с входом компенсирующего цифроаналогового преобразователя, выход которого соединен с одним из входов

25 суммирующего усилителя, выход которого соединен с управляющим входом цифро-аналогового преобразователя кода приращения по одной из координат, а другой вход - соединен с управляющим входом цифро-ана30 i логового преобразователя по другой из координат и с выходом эталонного, цифро-аналогового преобразователя, вход которого соединен с соответствующим выходом блока нормализации кодов приращений, выход элемента ИЛИ соединен с входом перво- го элемента задержки.

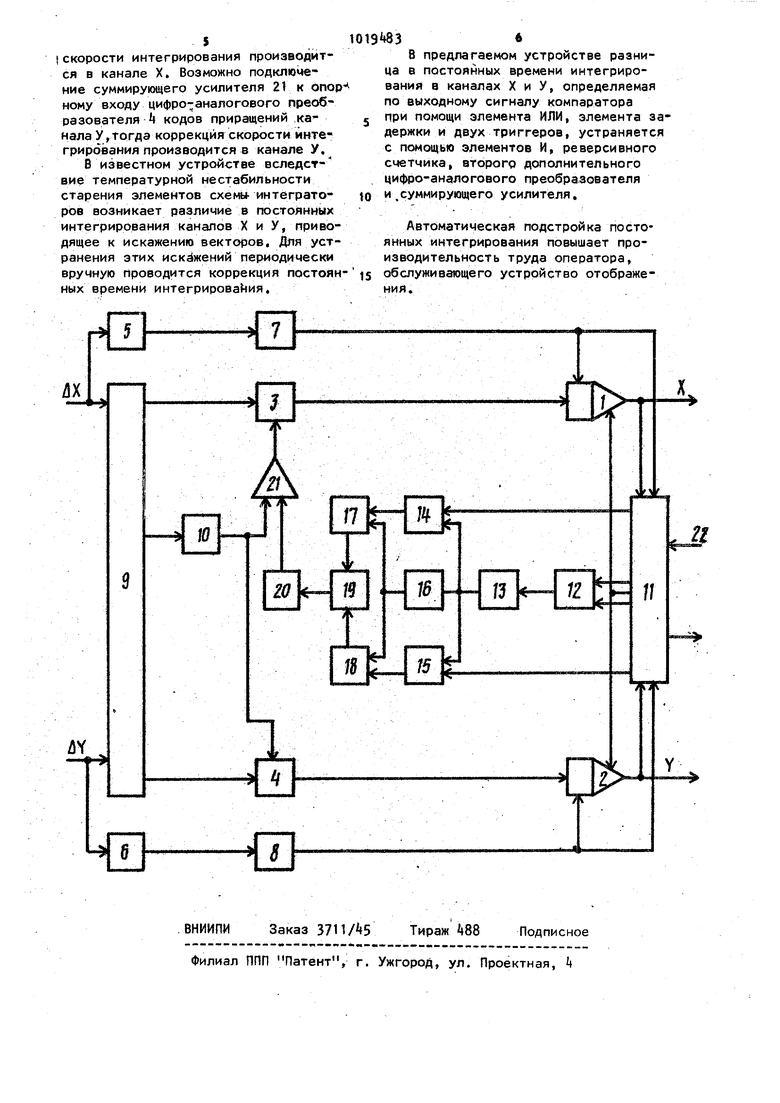

На чертеже представлена структур- ная схема генератора векторов,

40 Генератор векторов содержит интегрирующие усилители 1 и 2, цифро-аналоговые преобразователи 3 и 4 кодов приращений, сумматоры 5 и 6 приращений, цифро-аналоговые преобразова45 тёли 7 и 8 кодов координат конечных точек, блок 9 нормализации приращений, эталонный цифро-аналоговый преобразователь 10, компаратор 11, элемент ИЛИ 12, первый элемент задерж50. ки 13, .триггеры и 15, второй элемент задержки 16, элементы И 17 и 18, реверсивный счетчик 19, компен- сирующий цифро-аналоговый преобразователь 20, суммирующий усилитель

55 21, шину 22 пуска интегирования.

Устройство работает следующим об;разом. Из цифрового запоминающего устройства (не показано) поступают коды приращений X и У одновременно . на блок 9 нормализации и сумматоры 5 и 6 накапливающего типа. После отработки кодов в блоке 9 нормализации и преобразования их в цифро-аналоговых п(зёобразователей 3 k и 10 происходит занесение кодов и сумматоров 5 и 6 в цифро-акалоговые преобразователи 7 и 8, Одновременно по шине 22 Пуск интегрирования по ступает импульс, в результате кбторого компаратор 11 переводит интегрирующие усилители 1 и 2 в режим ин тегрирования, В этом режиме на выхо дах усилителей 1 и 2 формируются пи лообразные напряжения, направлениег скорость которых определяется веяичиной и знаком напряжений, поступаю щих с. выходов цйфро-аналоговых преобразователей 3 и Л,- После того, как величина напряже ний на выходе интегрирующих УСИЛЙ-; телей 1 и 2 сравняется с величиной напряжения соответствующего цифроаналогового преобра зователя 7 i 8 кЬмпаратор 11 сформирует сигнал, проводящий интегрирующие усилители 1 и 2 в режим начальных условий. Одновременно компаратрр 11 выдает сигналы на триггеры 1 и 15, элемент ИЛИ 12 и далее через элемент . задержки 13 на вторые входы тригтеров 1 и 15. При различных постоянных интегрирования в каналах X к У моменты выдачи сигналов с .компаратора 11 на триггеры 14 и 15 отличаются. Наличи различий в постоянных интегрирования в каналах X и У вызывает появле ние ошибки на стыках векторов, оШиб будет тем больше, чем выше напряже ние на выходе цифро-аналоговых пре:образЪвателей 3 и 4 кодов прирщцени Первый элемент задерхжки 13 определяет чувствительность схе№й,т,е ту минимальную разницу в моментах появления выходных сигналов компара тора 11, которую может обнаружить схема, и формирует импулъсы счета. Если скорость интегрирования в к нале Х(У) выше чем в канале У(Х), то сигнал с компаратора 11 на триггер И (15) .выдается раньше чем на триггер 15 (И). При этом если вре мя между моментами появления выходных сигналов компаратора 11 больше чем время, определяемое первым элементом задержки 13 то сигнал с выхода компаратора 11 устанавливает триггер Н (15) в состояние, которое обеспечивает закрытие первого элемента И 17 (18), а триггер 15 (И) в состояние, которое обеспечивает открытие второго элемента И 18 (17) Импульс счета с выхода второго элемента 16 задержки через открыть|й второй элемент И I8il7) поступает на счетный вход реверсивного счетчика 19 и изменяет код, содержащийся в нем. Второй элемент задержки Ш служит для повышения надежности выделения импульсов счета. Изменившееся состояние кода на выходе реверсивного счетчика 19 вызывает изменение напряжения на выходе второго дополнительного цифроаналогового преобразователя 20 и соответственно на выходе суммирующего усилителя 21, подключенного к опорзному входу цйфрово-аналогового преобразователя 3 кодов приращений канала X, что приводит к изменению уровня напряжения на входе интегрирующего усилителя 1и к уменьшению различий меаду скоростями интегрирования каналов X и у. Коррекция скорости .интегриррвания производится до тех пор, пока сигналы с выхода компаратора 11 поступают на входы триггеров 14 и 15 с интервалом меньшим чем время, определяемое первым элементам задержки ЛЗ, При этом элементы И 17 и 18 закрываются, блокируя прохождение сигна-; лов на счетчик 16 импульса счета с выхода второго элемента задерж- ; ки 1-6, : : - ,.,;,; . Напряжение на опорном входе цифро-аналогового преобразователя 3 кодов приращений остается постоянным до тех пор, пока постоянные интегрирования каналов X и У равны. Автоматическая коррекция скорости интегрирования канала X производится периойичееки в начале kiaiflP регенерации. Цифровое запоминанйчее устройство (не показано) выдает информацию для отображения векторе с максимальными приращения. Если скорости интегрирования в каналах X и У различны, то включается вхама коррекции. .t . На схеме суммирующий уо(литель 21 подключен к опорному вхОду цифроаналогового преобразователя 3 кодов приращений канала X, и коррекция

t скорости интегрирования производится в канале X. Возможно подключение суммирующего усилителя 21 к опорному входу цифро-аналогового преобразователя кодов приращений канала У , тогда коррекция скорости интегрирования производится в канале У, В известном устройстве вследствие температурной нестабильности старения элементов схемы- интеграторов возникает различие в постоянных интегрирования каналов X и У, приводящее к искажению векторов. Для устранения этих искажений периодически вручную Проводится коррекция постоянных времени интегрирования.

В предлагаемом устройстве разница в постоянных времени интегрирования в каналах X и У, определяемая по выходному сигналу компаратора при помощи элемента ИЛИ, элемента здержки и двух триггеров, устраняетс с помощью элементов И, реверсивного счетчика, второго дополнительного ци(|чэо-аналогового преобразователя и , суммирующе го у силителя.

Автоматическая подстройка постоянных интегрирования повышает производительность труда оператора, обслуживающего устройство отображения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор векторов | 1984 |

|

SU1257698A1 |

| Устройство для измерения энергии | 1987 |

|

SU1575120A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1985 |

|

SU1304014A1 |

| Многоканальный цифроаналоговый преобразователь | 1984 |

|

SU1269269A1 |

| Устройство для измерения флуктуационной составляющей частоты сигналов с линейно-частотной модуляцией | 1988 |

|

SU1631456A1 |

| ГЕНЕРАТОР ВЕКТОРОВ | 1972 |

|

SU432543A1 |

| Функциональный преобразователь | 1987 |

|

SU1462369A1 |

ГЕНЕРАТОР векторов по авт св. № , отличаю щ и йс я тем, чтоj с цёлыо псвышения томности j он содержит cyfWHpyffl iKfi усилитель эталсжи и компеисирующий цифро-анапоговы е гтреобраэбватепи, реверсивный счетчик первый и второй элементы М, первый и второй триггеры, первый и второй элементы задержки и элемент ИЯЙ, входа которого .соединены с сздмими из выходов компаратора, другие выходы которого соединены с одними из Входов перворо и второго триггеров, другие входы которых соединены с выходом первого элемента задержки и входом второго элемента задержки, выход которого соединен с одними из входов первого и второго элементов И, другие входы котсфых соединены с выходами первого и BToP roTpnrrejpbia, а выходы соединены с входами реверсивного счетчика, выход которого соединен с входом кЬмпёйсйрующего цифроаналогового npie образе аТеля выход которого соединен с одним из входов cyм в4pyю гo усилителя, выход которого соединен су оравяящи MB ходом цифро-аналогового прё : аэОвателя кода прйрейчений по одной из координат, а другой вход соездинён с управляющим хйяс цифро-аналогового преобразователя по другой из коордиУ НаТ и с выходом эталонного цифро: аналогового преобразователя, вхой которого )еоединен с соответствующим выходом нормализации кодов приращений, выход элемента ИДИ соединен с первого элемента задержки. Ф |« 90 &д;

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство ССеР ,, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-05-23—Публикация

1981-10-09—Подача