Изобретение относится к автоматике и вычислительной технике и может быть использовано в графических терминальных устройствах для построения отрезков прямых с приращениями йХ О и uY 0.

Цель изобретения - повышение быст- родействия интерполятора.

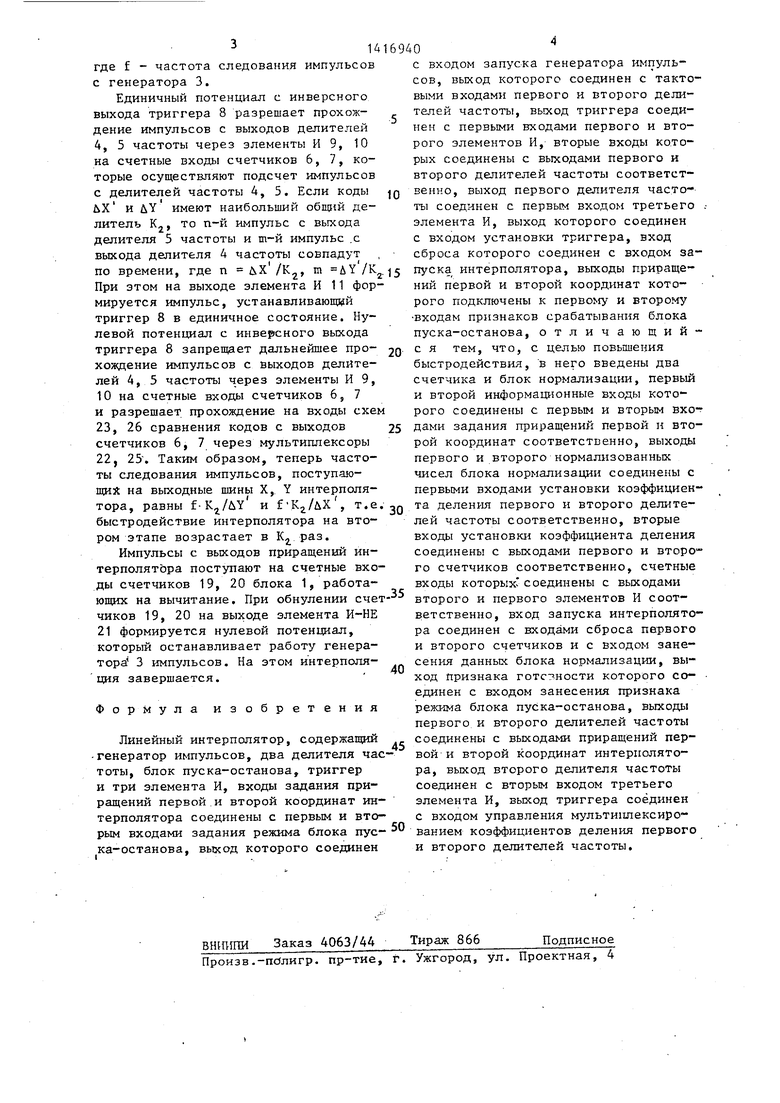

На чертеже приведена функциональ- ная схема линейного интерполятора.

Линейный интерполятор содержит блок 1 нормализации, блок 2 пуска- останова, генератор 3 импульсов, де- ители 4, 5 частоты, счетчики 6, 7, триггер 8, элементы И 9 - 11.

Блок 1 нормализации, осуществляющий нормализацию двоичных кодов приращений ДХ, iY путем одновременного сдвига этих кодов вправо до тех пор, пока хотя бы один младший разряд не будет единичным, может быть реализован, например, на сдвиговых регистрах 12, 13, к выходам младших разря- дов которых подключены входы элемента ИЛИ 14, выход которого через элеент НЕ 15 подключен к входам элемента 2 И-ИЛИ 16 и к выходу признака готовности блока 1 нормализации, выход элемента 2И-ИЛИ 16 через элемент 17 задержки подключен к одному из входов элемента 2И-ИЛИ 16 и к входам . управления сдвигом регистров 12, 13, ругой вход элемента 2И-ИЛИ 16 через элемент 18 задержки подключен к входам записи регистров 12, 13 и к вхоу занесения данных блока 1 нормали- зации.

Блок 2, осуществляющий управление генератором 3 импульсов, может быть реализован, например, на счетчиках 19, 20 и элементе 21.

Делитель 4 частоты может быть выполнен, например, на мультиплексоре 22, схеме 23 сравнения и счетчике 24 аналогично делитель 5 - на мультиплексоре 25, схеме 26 сравнения и счетчике 27.

Интерполятор работает следующим образом.

Перед началом интерполяции счетчики 24, 27 делителей частоты 4, 5, счетчики 19,20 блока 2 установлены в нулевое состояние, а на входах задания приращений выставлены двоичные кодыйХ 0, . Импульс, приходящий на вход запуска Z интерполятора, устанавливает в нулевое состояние счетчики 6, 7, триггер 8 и произ0

5

0

5

0

5

0

5

0

5

водит запись информации в сдвигов1)1е регистры 12, 13 блока 1. Если младшие разряды iX и uY нулевые, то единичный потенциал с вьосода элемента НЕ 15 разрешает прохождение импульса запуска интерполятора, задержанного на элементе 18 задержки, через элемент 2И-Ш1И 16 на входы управления сдвигом регистров 12, 13. Информация сдвигается на один разряд вправо. Если вновь младщие разряды регистров 12, 13 нулевые, то импульс с выхода элемента 2И-ИЛИ 16, задержанный на элементе 17 задержки, вновь поступает на входы управления сдвигом регистров 12, 13. Информация сдвигается еше на один разряд вправо. Это продолжается, пока по крайней мере один из младших разрядов регистров 12, 13 не.будет единичным. В этом случае на выходе элемента ИЖ 14 устанавливается единичный потенциал, а на выходе элемента НЕ 15 - нулевой, который запрещает прохождение импульсов через элемент 2И-ИЛИ 16. Таким образом, осуществляется преобразование кодов приращений 6Х, fiY в нормализованные коды ЛХ , uY путем деления кодов ЛХ, Y на наибольший общий делитель К (, кратный степени 2: К, 2, что приводит к повьщ1ению быстродействия интерполятора на начальном этапе, Из;ченение состояния выхода элемента ИЛИ 14 из О в 1, поступающее на входы записи информации счетчиков 19, 20 блока 2, заносит кодыЛХ, uY в счетчики 19, 20, что приводит к появлению единичного потенциала на выходе элемента И-НЕ 21, которьм запускает генератор 3 импульсов. Импульсы с выхода генератора 3 поступают на тактовые входы делителей частоты 4, 5, при этом единичный потенциал с инверсного выхода триггера 8, посту- 1паюм;ий на управляющие входы мультиплексоров 22, 25, разрешает прохождение на входы схем сравнения 23, 26 кодов ЛХ , UY с выходов блока 1 . При совпадении кодов йХ или uY с кодами на выходах счетчиков 24 или 27 на выходе схемы 23 или 26 сравнения появляется импульс, который устанавливает соответствующий счетчик в нулевое состояние и поступает на выход соответствующего делителя часто- ты. Таким образом, на первом этапе на выходы X, Y интерполятора поступают импульсы с частотами f/uY и f/fiX ,

10

где f - частота следования импульсов с генератора 3.

Единичный потенциал с инверсного выхода триггера 8 разрешает прохождение импульсов с выходов делителей 4, 5 частоты через элементы И 9, 10 на счетные входы счетчиков 6, 7, которые осуществляют подсчет импульсов с делителей частоты 4, 5. Если коды ЛХ и uY имеют наибольший общш делитель Kj,, то п-й импульс с выхода делителя 5 частоты и т-й импульс .с выхода делителя 4 частоты совпадут по времени, где п ЛХ /К„, m „. , . При этом на выходе элемента И 11 формируется импульс, устанавливающий триггер 8 в единичное состояние. Нулевой потенциал с инверсного выхода триггера 8 запрещает дальнейшее прохождение импульсов с выходов делителей 4, 5 частоты через элементы И 9, 10 на счетные входы счетчиков 6, 7 и разрешает прохождение на входы схем 23, 26 сравнения кодов с выходов счетчиков 6, 7 через мультиплексоры 22, 25, Таким образом, теперь частоты следования импульсов, поступающих на выходные шины X, Y интерполятора, равны и f Kj/uX , т.е. OQ быстродействие интерполятора на втором этапе возрастает в Kj раз.

Импульсы с выходов приращений интерполятора поступают на счетные входы счетчиков 19, 20 блока 1, работас входом запуска генератора импульсов, выход которого соединен с тактовыми входами первого и второго делителей частоты, выход триггера соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с выходами первого и второго делителей частоты соответственно, выход первого делителя частоты соединен с первым входом третьего . элемента И, выход которого соединен с входом установки триггера, вход сброса которого соединен с входом за- &Y/K,j. 5 пуска интерполятора, выходы прираще

20

25

НИИ первой и второй координат которого подключены к первому и второму входам признаков срабатывания блока пуска-останова, отличающий- с я тем, что, с целью повышения быстродействия, в него введены два счетчика и блок нормализации, первый и второй информационные входы которого соединены с первым и вторым вхо- дами задания приращений первой и второй координат соответственно, выходы первого и второго нормализованных чисел блока нормализации соединены с первыми входами установки коэффициента деления первого и второго делителей частоты соответственно, вторые входы установки коэффициента деления соединены с выходами первого и второго счетчиков соответственно, счетные входы которых соединены с выходами

ющих на вычитание. При обнулении счет- - второго и первого элементов И соот10

OQ

5

НИИ первой и второй координат которого подключены к первому и второму входам признаков срабатывания блока пуска-останова, отличающий- с я тем, что, с целью повышения быстродействия, в него введены два счетчика и блок нормализации, первый и второй информационные входы которого соединены с первым и вторым вхо- дами задания приращений первой и второй координат соответственно, выходы первого и второго нормализованных чисел блока нормализации соединены с первыми входами установки коэффициента деления первого и второго делителей частоты соответственно, вторые входы установки коэффициента деления соединены с выходами первого и второго счетчиков соответственно, счетные входы которых соединены с выходами

второго и первого элементов И соот

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейный интерполятор | 1986 |

|

SU1397881A1 |

| Устройство для программного управления | 1985 |

|

SU1280571A1 |

| Функциональный интерполятор | 1986 |

|

SU1383301A1 |

| Интерполятор | 1985 |

|

SU1413600A1 |

| Линейный интерполятор | 1975 |

|

SU543922A1 |

| Линейный интерполятор | 1989 |

|

SU1695267A1 |

| Линейный интерполятор | 1984 |

|

SU1249537A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1709269A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для графического построения отрезков прямых с положительными приращениями. При этом повышается быстродействие интерполятора за счет уменьшения коэффициентов деления делителей 4, 5 частоты в число раз, равное наибольшему общему делителю заданных приращений йХ и ДУ. Интерполятор содержит блок 2 пуска-останова, генератор 3 импульсов, счетчики 6, 7, триггер 8, элементы И 9 - 11, блок 1 нормализации, 1 ил.

чиков 19, 20 на выходе элемента И-НЕ 21 формируется нулевой потенциал, который останавливает работу генератора 3 импульсов. На этом интерполяция завершается.

Формула изобретения Линейный интерполятор, содержащий

45

-генератор импульсов, два делителя частоты, блок пуска-останова, триггер и три элемента И, входы задания приращений первой и второй координат интерполятора соединены с первым и втоветственно, вход, запуска интерполятора соединен с входа.ми сброса первого и второго счетчиков и с входом занесения данных блока нормализации, выход признака готсзности которого со- единен с входом занесения признака режима блока пуска-останова, выходы первого и второго делителей частоты соединены с выходами приращений первой и второй координат интерполятора, выход второго делителя частоты соединен с вторым входом третьего элемента И, выход триггера соединен с входом управления мульти1шексирорым входами задания режима блока пус- ванием коэффициентов деления первого ка-останова, выход которого соединен и второго делителей частоты.

ветственно, вход, запуска интерполятора соединен с входа.ми сброса первого и второго счетчиков и с входом занесения данных блока нормализации, выход признака готсзности которого со- единен с входом занесения признака режима блока пуска-останова, выходы первого и второго делителей частоты соединены с выходами приращений первой и второй координат интерполятора, выход второго делителя частоты соединен с вторым входом третьего элемента И, выход триггера соединен с входом управления мульти1шексированием коэффициентов деления первого и второго делителей частоты.

| Линейный интерполятор | 1976 |

|

SU637788A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Линейный интерполятор | 1984 |

|

SU1249537A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-15—Публикация

1986-11-17—Подача