(54) ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР

| название | год | авторы | номер документа |

|---|---|---|---|

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| Динамический регистр сдвига | 1988 |

|

SU1671047A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ С ВРЕМЕННОЙ ЗАДЕРЖКОЙ И НАКОПЛЕНИЕМ СИГНАЛОВ С МНОГОЭЛЕМЕНТНЫХ ФОТОПРИЕМНИКОВ ИНФРАКРАСНОГО ИЗЛУЧЕНИЯ | 2012 |

|

RU2498456C1 |

| Регистр сдвига | 1987 |

|

SU1476535A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2542913C1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Управляющий регистр для буферного запоминающего устройства | 1984 |

|

SU1231536A1 |

| Ячейка памяти для регистра сдвига на МДП-транзисторах | 1988 |

|

SU1612802A1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

-1

Изобретение относется к автоматике и вычислительной технике.

Известен динамический сдвиговый регистр, содерясаишй нечетяью и четные ячейки, соединенные соответственно с шинами первой и второй фазы, каждая ячейка которсмго содержит 2 МДП--тра&зистора и МДП-«арактор fl

Недостатком указаннохч) устройства 51вляетсз низкое быстродействие, обуспав ленное тем, что разряд узловой емкости ; ячейки осуществляется токами утечки и передачей зар5ша данной емкости в истО- ковухо емкость предыдущей ячейки.

Наиболее близким к предлагаемому по технической сущности является дина мический сдвиговь1й регистр, содержащий нечетные и четные ячейки, соединенные соответственно с шинами первой и второй фазы, каждая ячейка которого содержит МДП-«арактор в три МДП-транзис- тора, причем диффузионная обкладка ва« рактора, сток первого транзистора и сток второго транзистора соединены с шиной

соответствующей фазы, МДПнварактор служит для формирования на затворе второго транзютора (при условии, что к моменту дейстмга фазового импульса на входе ячейки установлена логическая ) напряжения, прёвыщающего фазовое 2 .

Недостатком известного динамического сдвигового регистра является низкое быстродействие, обусловленное необходимостью заканчивать разряд выходной емкости ячейки до прихода фазового импульса, соответствующего предыдущей ячейке.

Цель изобретения - повышение быстродействия динамического сдвигового региорра.

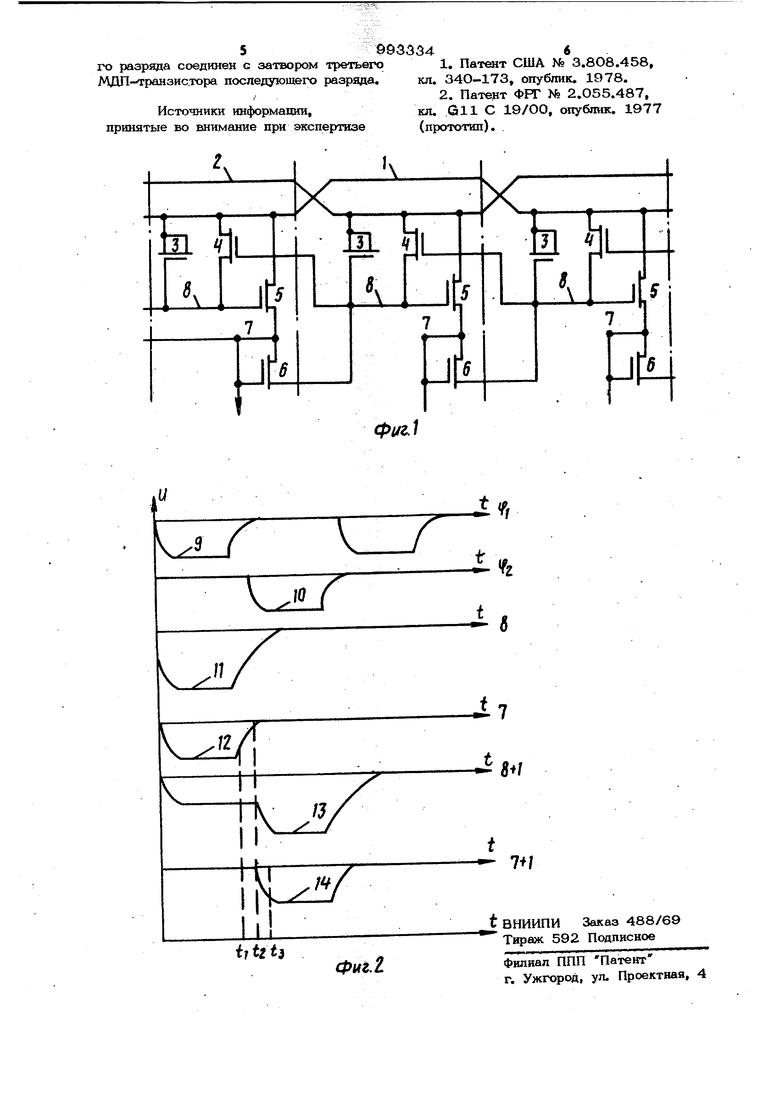

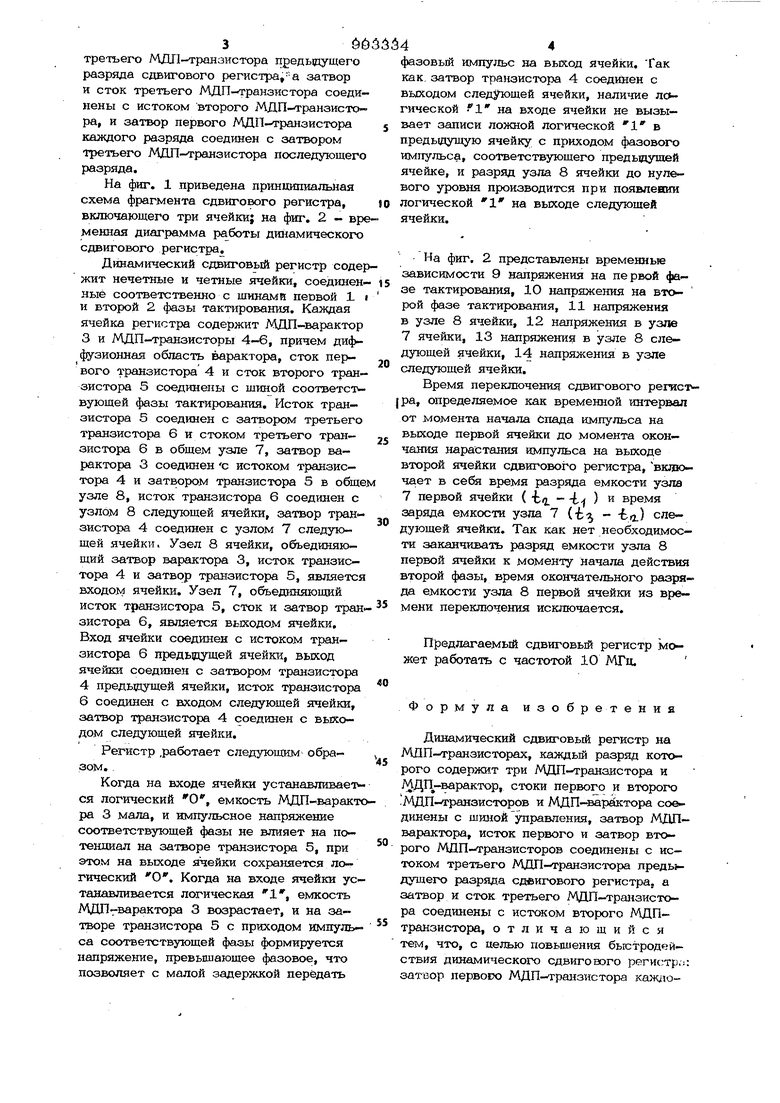

Поставленная цель достигается тем, что динамический сдвиговый регистр на МДП-транзнсторах,каждый разряд которого содержит три МДП-транзистора и МДП-варактор, стоки первого и второго МДП-транзисторов и МДП-варактора соединены с шиной управления, затвор МДПварактора, исток первого и затвор второго АЩП- гранзисторов соединены с истоком третьего МДГ1-транзистора предьщущего разряда сдвигового регистра, а затвор и сток третьего МДП-транзистора соединены с истоком второго МЯП-о-ранзистора, и затвор первого МДП-транзистора каждого разр5ада соединен с затвором третьего МДП-транзистора последующего разряда. На фиг. 1 приведена приншшиальная схема фрагмента сдвигового регистра, включающего три ячейки; на фиг. 2 - вр менная диаграмма работы динамического сдвигового регистра Динамический сдвиговьй регистр содер жит нечетные и четные 5гчейки, соединен ныё соответственно с шинами первой 1 и второй 2 фазы тактирования. Каждая ячейка регистра содержит МДП-варактор 3и МДП-транзисторы 4-6, причем диффузионная область варактора, сток первого транзистора 4 и сток второго транзистора 5 соединены с шиной соответствующей фазы тактирования. Исток транзистора 5 соединен с затвором третьего транзистора 6 и стоком третьего транзистора 6 в общем узле 7, затвор варактора 3 соединен с истоком транзистора 4 и затвором транзистора 5 в обще узле 8, исток транзистора 6 соединен с узлом 8 следующей ячейки, затвор транзистора 4 соединен с узлом 7 следующей ячейки. Узел 8 ячейки, объединяющий затвор ;варактора 3, исток транзистора 4 и затвор транзистора 5, является входом ячейки. Узел 7, объединяющий исток транзистора 5, сток и затвор тран зистора 6, является выходом ясчейки. Вход ячейки соединен с истоком транзистора 6 предыдущей ячейки, выход ячейки соединен с затвором транзистора 4предьщущей ячейки, исток транзистора 6 соединен с входом следующей ячейки, затвор транзистора 4 соединен с выходом следующей ячейки. Регистр .работает следующим- образом. Когда на входе ячейки устанавливает ся логический О, емкость МДП-варакт ра 3 мала, и импульсное напр5ш:ение соответствующей фазы не влияет на потешшал на затворе транзистора 5, при этом на выходе ячейки сохраняется логический О. Когда на входе ячейки устанавливается логическая 1, емкость МДПт-варактора 3 возрастает, и на затворе транзистора 5 с приходом импульса соответствующей фазы формируется напряжение, превышающее фазовое, что позволяет с малой задержкой передать азовый импульс на выход ячейки. Так как. затвор транзистора 4 соединен с выходом след5 тощей ячейки, наличие лоической на входе ячейки не вызывает записи ложной логической I в редыдущую ячейку с приходом фазового импульса, соответствующего предыдущей ячейке, и разряд узла 8 ячейки до нулевого уровня производится при появлегога огической 1 на выходе следующей ячейки. На фиг. 2 представлены временные зависимости 9 напряжения на первой фазе тактирования, 10 напряжения на второй фазе тактирования, 11 напряжения в узле 8 ячейки, 12 напряжения в узле 7 ячейки, 13 напряжения в узле 8 следующей ячейки, 14 напряжения в узле следующей ячейки. Время переключения сдвигового регастpa, определяемое как временной интервал от момента начала Спада импульса на выходе первой ячейки до момента окончания нарастания импульса на выходе второй ячейки сдвигового регистра, включает в себя время разряда емкости узла 7 первой ячейки ( -t - -t ) и время заряда емкости узла 7 (t- - -ta) следующей ячейки. Так как нет необходимости заканчивать разряд емкости узла 8 первой 51чейки к моменту начала действия второй фазы, время окончательного разряда емкости узла 8 первой ячейки из времени переключения исключается. Предлагаемый сдвиговьй регистр может работать с частотой 10 МГц. Формула изобретения Динамический сдвиговый регистр на МПП-транзисторах, каждьй разряд которого содержит три МДП-транзистора и МДП -варактор, стоки первого и второго .МДП-/гранзисторов и МДП-варйктора соединены с шиной управления, затвор МДП- варактора, исток первого и затвор второго МДП-транзисторов соединены с истоком третьего МДП-транзистора предь дущего разряда сдвигового регистра, а затвор и сток третьего МДП-транзистора соединены с истсжом второго МДПтранзистора, отличающийся тем, что, с целью повышения бьгстродействия динамического сдвигового регистр.-:: загеор nepBotxj МДП-транзистора кажлого разряда соединен с затвором третьего МДП-транзис.тора последующего разряда.

1Источники информашга, принятые во внимание при экспертаее

ср1/г.1

Авторы

Даты

1983-01-30—Публикация

1981-01-07—Подача