1

Изобретение-относится к вычислительной технике и может быть использовано в качестве сдвигового регистра или распределителя импульсов в устройствах обработки данных (например, при обработке изображения).

Цель изобретения - повышение надежности устройства при увеличении его быстродействия путем соединения четырех МДП-транзисторов„по схеме квазистатического триггера, выход которого является выходом ячейки сдвигового регистра, а вход которого управляется от динамического запоминающего элемента. Использование квазистатического режима работы триггера как элемента хранения и передачи информации в регистре и использование регенеративного процесса переключения обеспечивают повышение надежности устройства при работе на более высокой частоте.

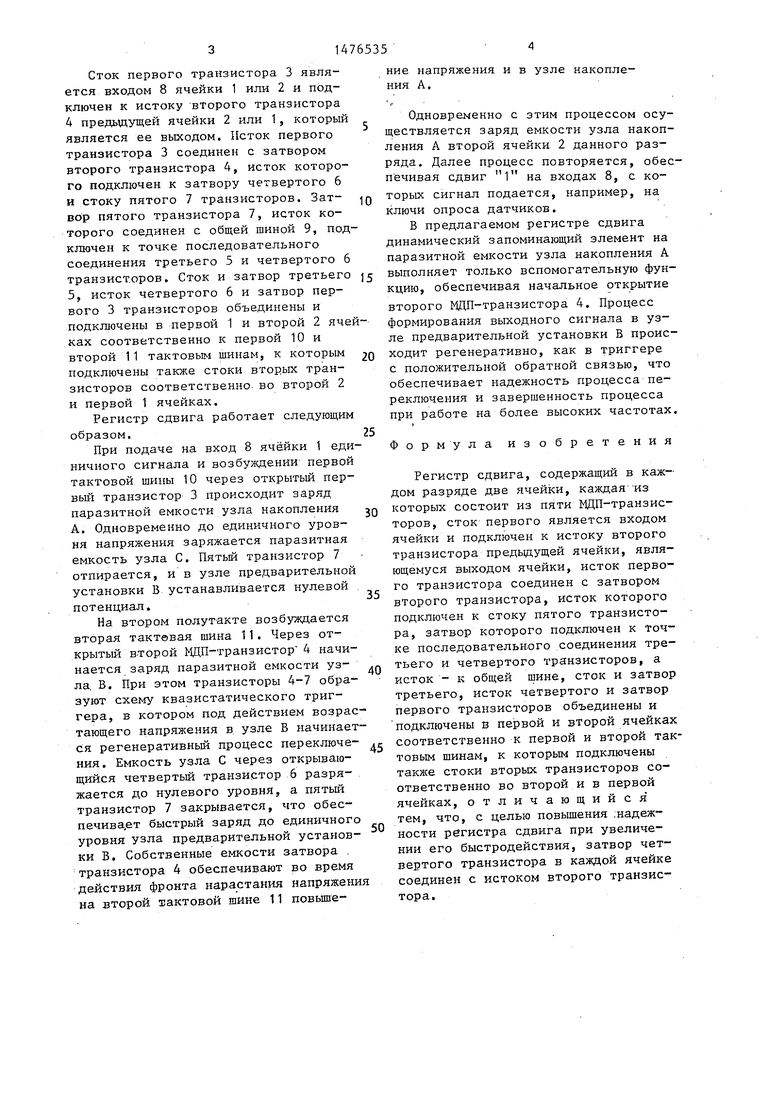

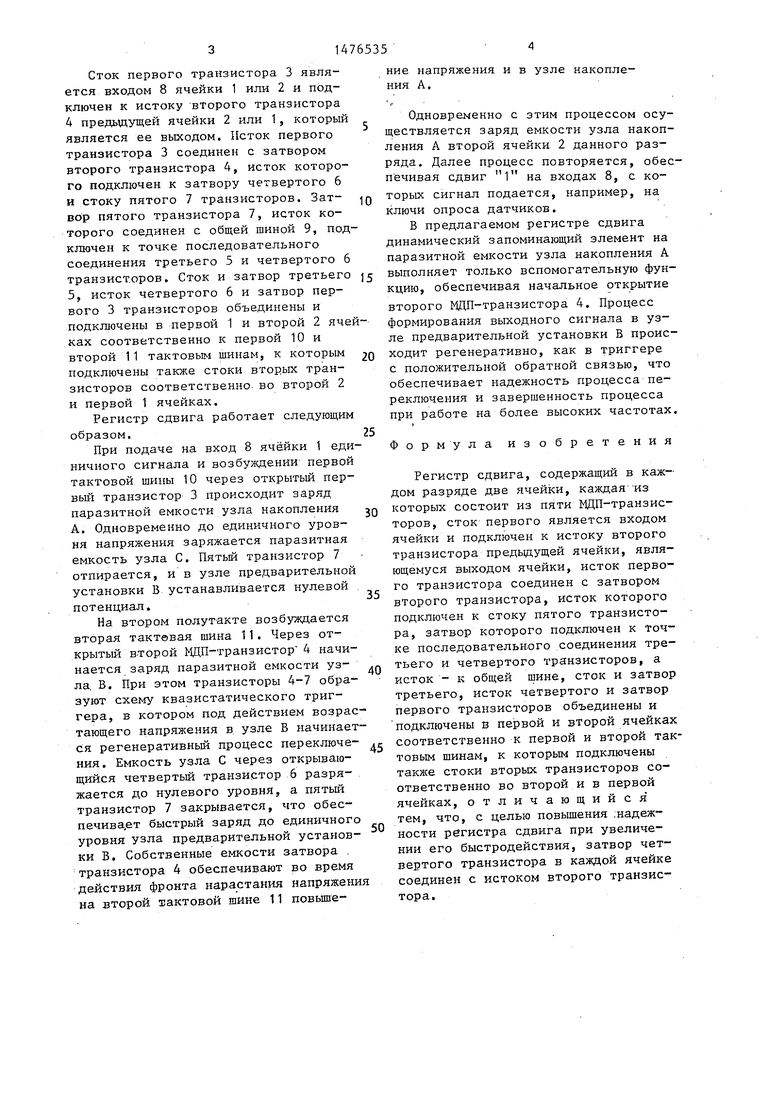

На чертеже приведена принципиальная схема регистра сдвига.

Регистр сдвига содержит в каждом разряде первую 1 и вторую 2 ячейки, каждая из которых содержит пять МДП- транзисторов 3-7.

Ј vj

О

сл

00

сл

314

Сток первого транзистора 3 является входом 8 ячейки 1 или 2 и подключен к истоку второго транзистора 4 предьщущей ячейки 2 или 1, который является ее выходом. Исток первого транзистора 3 соединен с затвором второго транзистора 4, исток которого подключен к затвору четвертого 6 и стоку пятого 7 транзисторов. Затвор пятого транзистора 7, исток которого соединен с общей шиной 9, подключен к точке последовательного соединения третьего 5 и четвертого 6

ние напряжения ния А.

и в узле накопле

Одновременно с этим процессом осуществляется заряд емкости узла накопления А второй ячейки 2 данного разряда. Далее процесс повторяется, обеспечивая сдвиг 1 на входах 8, с которых сигнал подается, например, на ключи опроса датчиков.

В предлагаемом регистре сдвига динамический запоминающий элемент на паразитной емкости узла накопления А

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| СДВИГОВЫЙ РЕГИСТР (ВАРИАНТЫ) | 2013 |

|

RU2530271C1 |

| ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2542913C1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Регистр сдвига | 1975 |

|

SU550678A1 |

| Квазистатическое счетное устройство на МДП-транзисторах | 1986 |

|

SU1319255A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве сдвигового регистра или распределителя импульсов в устройствах обработки данных, например устройствах формирования сигналов при обработке изображений. Целью изобретения является повышение надежности устройства при увеличении его быстродействия. Для достижения поставленной цели в устройстве, содержащем в каждом разряде две последовательно соединенные ячейки из пяти МДП-транзисторов, первый и второй транзисторы соединены по схеме динамического элемента хранения, а второй, третий, четвертый и пятый МДП-транзисторы образуют квазистатический триггер, вход которого управляется от элемента хранения, для чего затвор четвертого МДП-транзистора соединен с истоком второго МДП-транзистора. За счет квазистатического режима работы образованного триггера, выход которого является выходом ячейки или разрядным выходом, достигается повышение надежности при работе устройства на более высокой частоте. 1 з.п. ф-лы, 1 ил.

транзисторов. Сток и затвор третьего |$ выполняет только вспомогательную функцию, обеспечивая начальное открытие второго МДП-транзистора 4. Процесс формирования выходного сигнала в узле предварительной установки В происходит регенеративно, как в триггере с положительной обратной связью, что обеспечивает надежность процесса переключения и завершенность процесса при работе на более высоких частотах.

20

25

30

5, исток четвертого 6 и затвор первого 3 транзисторов объединены и подключены в первой 1 и второй 2 ячейках соответственно к первой 10 и второй 11 тактовым шинам, к которым подключены также стоки вторых транзисторов соответственно во второй 2 и первой 1 ячейках.

Регистр сдвига работает следующим образом.

При подаче на вход 8 ячейки 1 единичного сигнала и возбуждении первой тактовой шины 10 через открытый первый транзистор 3 происходит заряд паразитной емкости узла накопления А. Одновременно до единичного уровня напряжения заряжается паразитная емкость узла С. Пятьй транзистор 7 отпирается, и в узле предварительной установки В устанавливается нулевой потенциал.

На втором полутакте возбуждается вторая тактввая шина 11. Через открытый второй МДП-транзистор 4 начинается заряд паразитной емкости узла В. При этом транзисторы 4-7 образуют схему квазистатического триггера, в котором под действием возрастающего напряжения в узле В начинается регенеративный процесс переключе- ,с ния. Емкость узла С через открывающийся четвертый транзистор 6 разряжается до нулевого уровня, а пятый транзистор 7 закрывается, что обеспечивает быстрый заряд до единичного уровня узла предварительной установки В. Собственные емкости затвора транзистора 4 обеспечивают во время действия фронта нарастания напряжения на второй тактовой шине 11 повыше35

40

50

Формула изобретения

Регистр сдвига, содержащий в каждом разряде две ячейки, каждая из которых состоит из пяти МДП-транзис- торов, сток первого является входом ячейки и подключен к истоку второго транзистора предыдущей ячейки, являющемуся выходом ячейки, исток первого транзистора соединен с затвором второго транзистора, исток которого подключен к стоку пятого транзистора, затвор которого подключен к точке последовательного соединения третьего и четвертого транзисторов, а исток - к общей шине, сток и затвор третьего, исток четвертого и затвор первого транзисторов объединены и подключены в первой и второй ячейках соответственно к первой и второй тактовым шинам, к которым подключены также стоки вторых транзисторов соответственно во второй и в первой ячейках, отличающийся тем, что, с целью повышения надежности регистра сдвига при увеличении его быстродействия, затвор четвертого транзистора в каждой ячейке соединен с истоком второго транзистора.

0

с

5

0

0

Формула изобретения

Регистр сдвига, содержащий в каждом разряде две ячейки, каждая из которых состоит из пяти МДП-транзис- торов, сток первого является входом ячейки и подключен к истоку второго транзистора предыдущей ячейки, являющемуся выходом ячейки, исток первого транзистора соединен с затвором второго транзистора, исток которого подключен к стоку пятого транзистора, затвор которого подключен к точке последовательного соединения третьего и четвертого транзисторов, а исток - к общей шине, сток и затвор третьего, исток четвертого и затвор первого транзисторов объединены и подключены в первой и второй ячейках соответственно к первой и второй тактовым шинам, к которым подключены также стоки вторых транзисторов соответственно во второй и в первой ячейках, отличающийся тем, что, с целью повышения надежности регистра сдвига при увеличении его быстродействия, затвор четвертого транзистора в каждой ячейке соединен с истоком второго транзистора.

Т

Л

et7

Ч

10

-j-i-i 4i1-u.

j

71

j1

| Патент США № 3935474, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Полупроводниковые формирователи сигнала изображения/Под ред | |||

| П.Йес- перса | |||

| М.: Мир, 1979, с | |||

| Способ обделки поверхностей приборов отопления с целью увеличения теплоотдачи | 1919 |

|

SU135A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-04-30—Публикация

1987-07-10—Подача