Изобретение относится к автоматике и вычислительной технике н может быть использовано для хранения и сдвига информации.

Целью изобретения является расширение области применения регистра за счет возможности выполнения реверсивного сдвига.

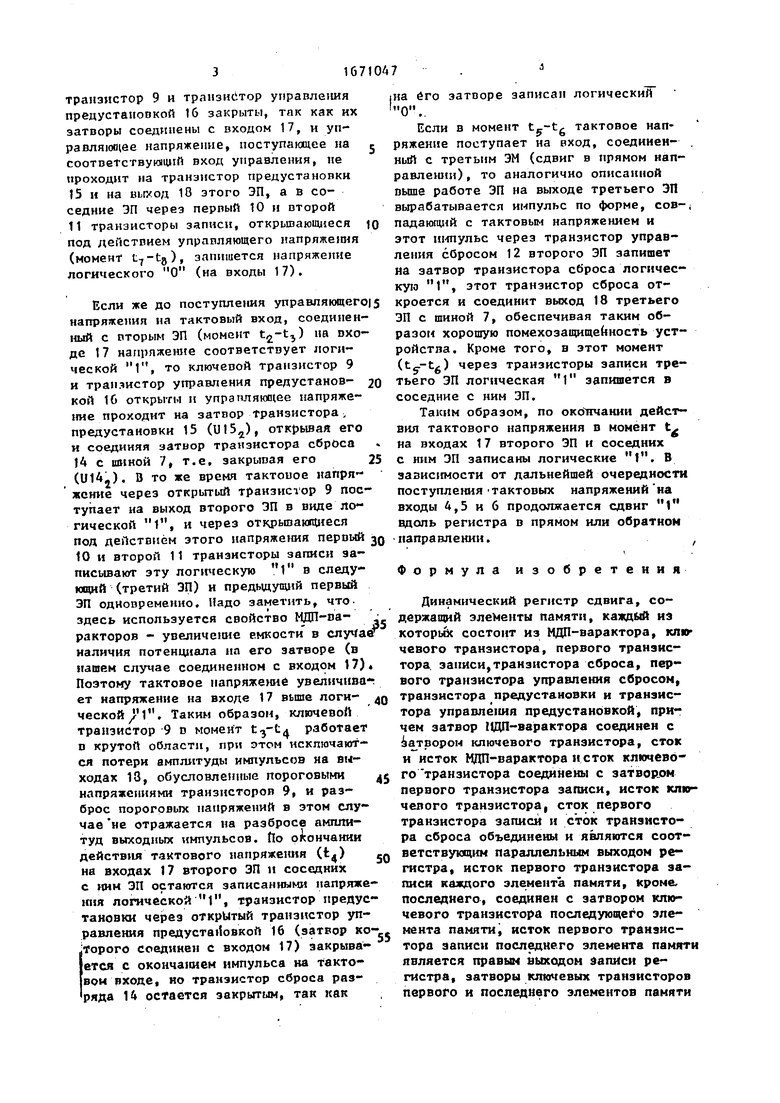

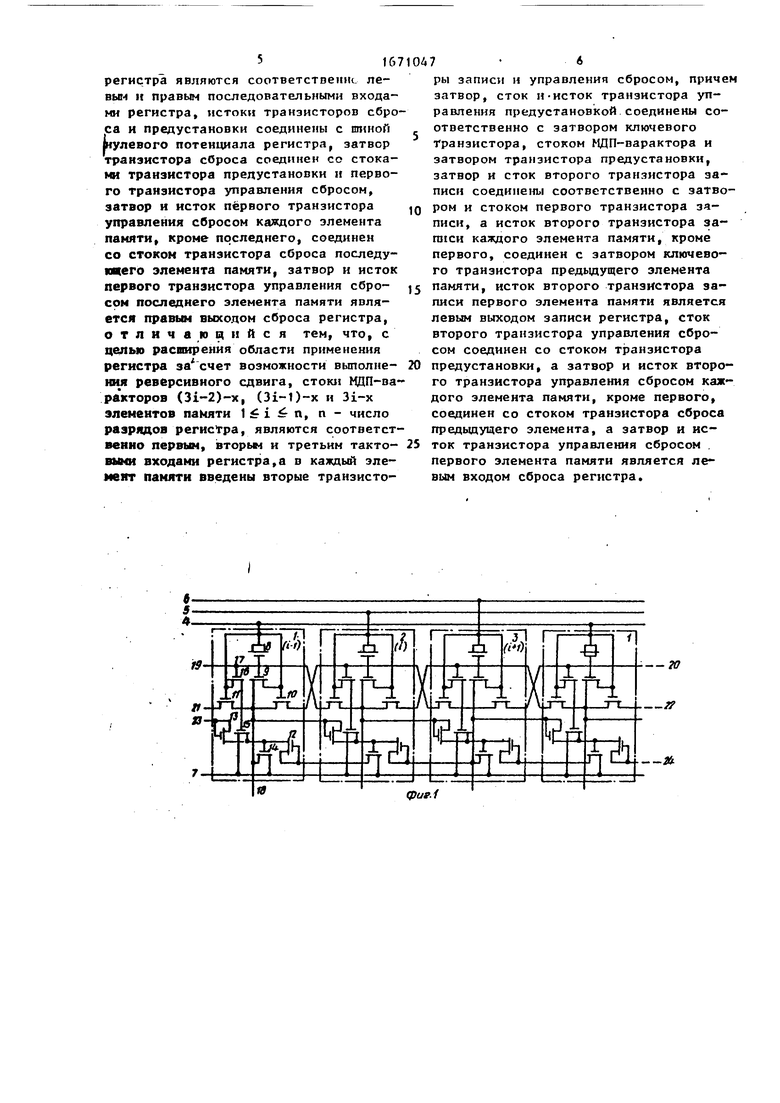

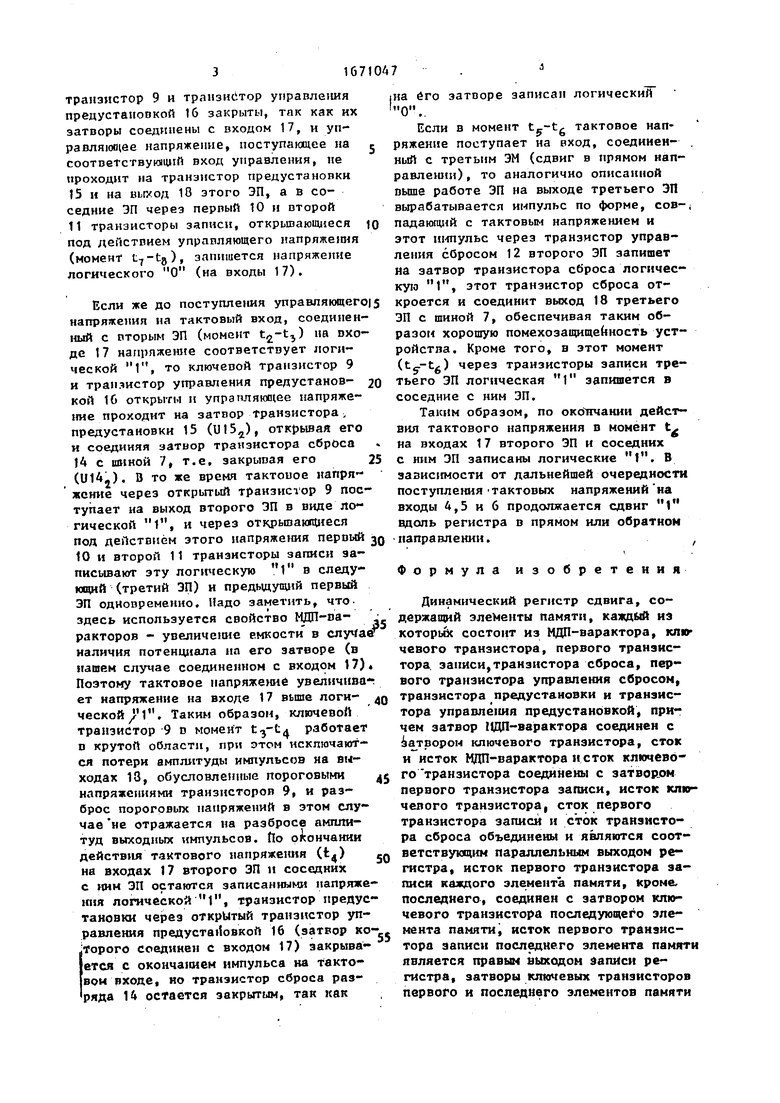

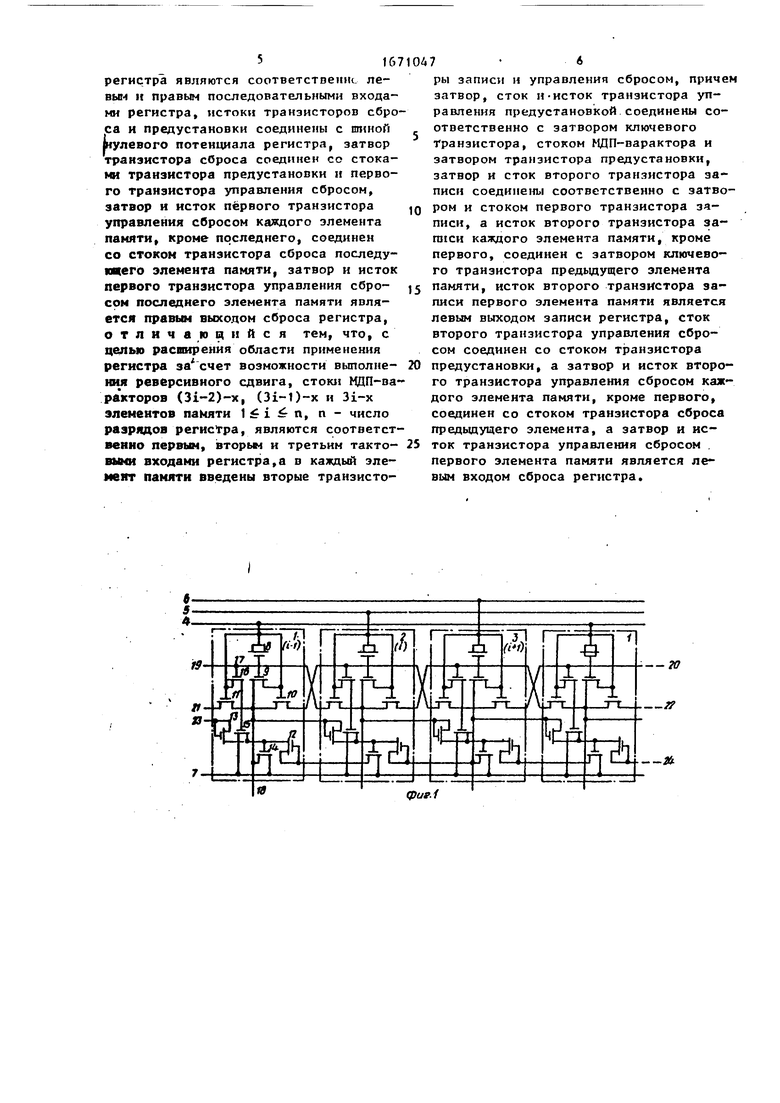

На фиг. 1 приведена принципиальная электрическая схема регистра; на фиг. 2 - временные диаграммы напряжений при сдвиге вправо и влево.

Регистр содержит элементы памяти 1,2,3, Имеющие соответственно тактовые входы 4,5,6 и подключенные к шине нулевого потенциала 7. Каждый элемент памяти (ЭП) состоит из МДП-варактора 8, ключевого транзистора 9, первого 10 и второго 11 транзисторов записи, первого 12 и второго 13 транзисторов управления сбросом, транзистора сброса 14, транзистора предустановки 15

и транзистора управления предустановкой 16. Каждый ЭП имеет вход 17 и выход 18. На фиг. 1 показаны также левый 19 и правый 20 последовательные входы регистра, левый 21 и правый 22 выходы записи, левый 23 и правый 24 входы сброса регистра.

На Фиг. 2 показаны следующие напряжения: U4, U5, U6 - на тактовых входах 4,5, - на входе 18 1-го ЭП, i 1,4; U15 - на затворе транзистора 15 1-го ЭП; U14;- на затво- ре транзистора 14 i-ro ЭП; U10; - на выходе 1-го ЭП.

Описание работы устройства дано на примере четырех последовательно соединенных ЭП (фиг. 1). Если до поступления управляющего напряжения на тактовый вход 4, соединенный с первым ЭП, на входе 17 напряжение соответствует логическому О (на фиг.2 эта ситуация в момент tg-t7 на входе первого ЭП), то в этом ЭП ключевой

«

(Л

о

Јь J

транзистор 9 и транзистор управления предустановкой 16 закрыты, так как их затворы соединены с входом 17, и управляющее напряжение, поступающее на соответствующий вход управления, не проходит на транзистор предустановки 15 и на выход 10 этого ЭП, а в соседние ЭП через первый 10 и второй 11 транзисторы записи, открывающиеся ю под действием управляющего напряжения (момент t7-t8), запишется напряжение логического О (на входы 17).

Если же до поступления управляющего напряжения на тактовый вход, соединенный с вторым ЭП (момент ) на входе 17 напряжение соответствует логической 1, то ключевой транзистор 9 и транзистор управления предустанов- 20 кой 16 открыты и управляющее напряжение проходит на затвор транзистора , предустановки 15 (Ш52), открывая его и соединяя затвор транзистора сброса J4 с шиной 7, т.е. закрывая его 25 (U14,). В то же время тактовое напря- жение через открытый транзистор 9 поступает на выход второго ЭП в виде логической 1, и через открывающиеся под действием этого напряжения первый эд 10 и второй 11 транзисторы записи записывают эту логическую 1 в следующий (третий ЭП) и предыдущий первый ЭП одновременно. Надо заметить, что- здесь используется свойство МДП-ва- ракторов - увеличение емкости в наличия потенциала на его затворе (в нашем случае соединенном с входом 17)« Поэтому тактовое напряжение увеличивает напряжение на входе 17 выше логи- ческой/М. Таким образом, ключевой транзистор 9 в момент работает в крутой области, при этом исключаются потери амплитуды импульсов на выходах 13, обусловленные пороговыми д напряжениями транзисторов 9, и разброс пороговых напряжений в этом случае не отражается на разбросе амплитуд выходных импульсов. По окончании действия тактового напряжения (t) C на входах 17 второго ЭП и соседних с ним ЭП остаются записанными напряжения логической 1, транзистор предустановки через открытый транзистор управления предустановкой 16 (затвор торого соединен с входом 17) закрывается с окончанием импульса на тактовом входе, но транзистор сброса разряда 14 остается закрытым, так как

J

ю

2025 эд« 0д$ CQ

5

(На его затворе записан логический .

Если в момент tc-tg тактовое напряжение поступает на вход, соединенный с третьим ЭМ (сдвиг в прямом направлении) , то аналогично описанной выше работе ЭП на выходе третьего ЭП вырабатывается импульс по форме, сов-, падающий с тактовым напряжением и этот импульс через транзистор управления сбросом 12 второго ЭП запишет иа затвор транзистора сброса логическую 1, этот транзистор сброса откроется и соединит выход 18 третьего ЭП с шиной 7, обеспечивая таким образом хорошую помехозащищенность устройства. Кроме того, в этот момент (ty-tg) через транзисторы записи третьего ЭП логическая 1 запишется в соседние с ним ЭП.

Таким образом, по окончании действия тактового напряжения в момент t на входах 17 второго ЭП и соседних с ним ЭП записаны логические 1. В зависимости от дальнейшей очередности поступления тактовых напряжений на входы 4,5 и б продолжается сдвиг 1 вдоль регистра в прямом или обратном направлении.

Формула изобретения

Динамический регистр сдвига, содержащий элементы памяти, каждый из которых состоит из МДП-варактора, ключевого транзистора, первого транзистора записи,транзистора сброса, первого транзистора управления сбросом, транзистора предустановки и транзистора управления предустановкой, причем затвор 11ДП-варактора соединен с затвором ключевого транзистора, сток и исток МДП-варактора исток ключевого транзистора соединены с затвором первого транзистора записи, исток ключевого транзистора, сток первого транзистора записи и сток транзистора сброса объединены и являются соответствующим параллельным выходом регистра, исток первого транзистора записи каждого элемента памяти, кроме, последнего, соединен с затвором ключевого транзистора последующего элемента памяти, исток первого транзистора записи последнего элемента памяти является правым выходом записи регистра, затворы ключевых транзисторов первого и последнего элементов памяти

регистра являются соответствен левым н правым последовательными входами регистра, истоки транзисторов сброса и предустановки соединены с шиной пулевого потенциала регистра, затвор транзистора сброса соединен со стоками транзистора предустановки н первого транзистора управления сбросом, затвор и исток первого транзистора управления сбросом каждого элемента памяти, кроме последнего, соединен со стоком транзистора сброса последующего элемента памяти, затвор и исток первого транзистора управления сбросом последнего элемента памяти является правым выходом сброса регистра, отличающийся тем, что, с целью расширения области применения регистра за счет возможности выполнения реверсивного сдвига, стоки МДП-ва ра хторов (3i-2)-x, (3i-1)-x и 3i-x элементов памяти 1 Ј i Ј n, n - число разрядов регистра, являются соответственно первым, вторым и третьим такто- выми входами регистра,а в каждый элемент памяти введены вторые транзисто

0

5

ры записи и управления сбросом, причем затвор, сток и-исток транзистора управления предустановкой соединены соответственно с затвором ключевого Транзистора, стоком МДП-варактора и затвором транзистора предустановки, затвор и сток второго транзистора записи соединены соответственно с затвором и стоком первого транзистора записи, а исток второго транзистора записи каждого элемента памяти, кроме первого, соединен с затвором ключевого транзистора предыдущего элемента 5 памяти, исток второго транзистора записи первого элемента памяти является левым выходом записи регистра, сток второго транзистора управления сбросом соединен со стоком транзистора предустановки, а затвор и исток второго транзистора управления сбросом каждого элемента памяти, кроме первого, соединен со стоком транзистора сброса предыдущего элемента, а затвор и исток транзистора управления сбросом . первого элемента памяти является левым входом сброса регистра.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига на МДП-транзисторах | 1988 |

|

SU1612802A1 |

| Управляющий регистр для буферного запоминающего устройства | 1984 |

|

SU1231536A1 |

| Динамический сдвиговый регистр | 1981 |

|

SU993334A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1980 |

|

SU868834A1 |

| Усилитель считывания (его варианты) | 1983 |

|

SU1137923A1 |

Изобретемте относится к автоматике и вычислительной технике и может быть использовано для хранения и сдвига информации. Цель изобретения - расширение области применения регистра за счет возможности выполнения реверсивного сдвига. Регистр содержит эле- ментм памяти, разбитые на три группы, в каждый элемент памяти дополнительно введены второй транзистор записи и второй транзистор управления сбросом. 2 ил.

20

Я

(pue.f

Фиг. г

| Шило В.П | |||

| Популярные цифровые микросхемы | |||

| - М.: Радио н связь, 1987, с | |||

| Реверсивный дисковый культиватор для тросовой тяги | 1923 |

|

SU130A1 |

| Авторское свидетельство СССР 1146731, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-09-23—Публикация

1988-12-05—Подача