Изобретение относится к вычисли- ;тельной технике н может быть использовано при построении синхронных буферньпс запоминающих устройств (ЗУ)

Цель изобретения - упрощение и повьшение быстродействия регистра.

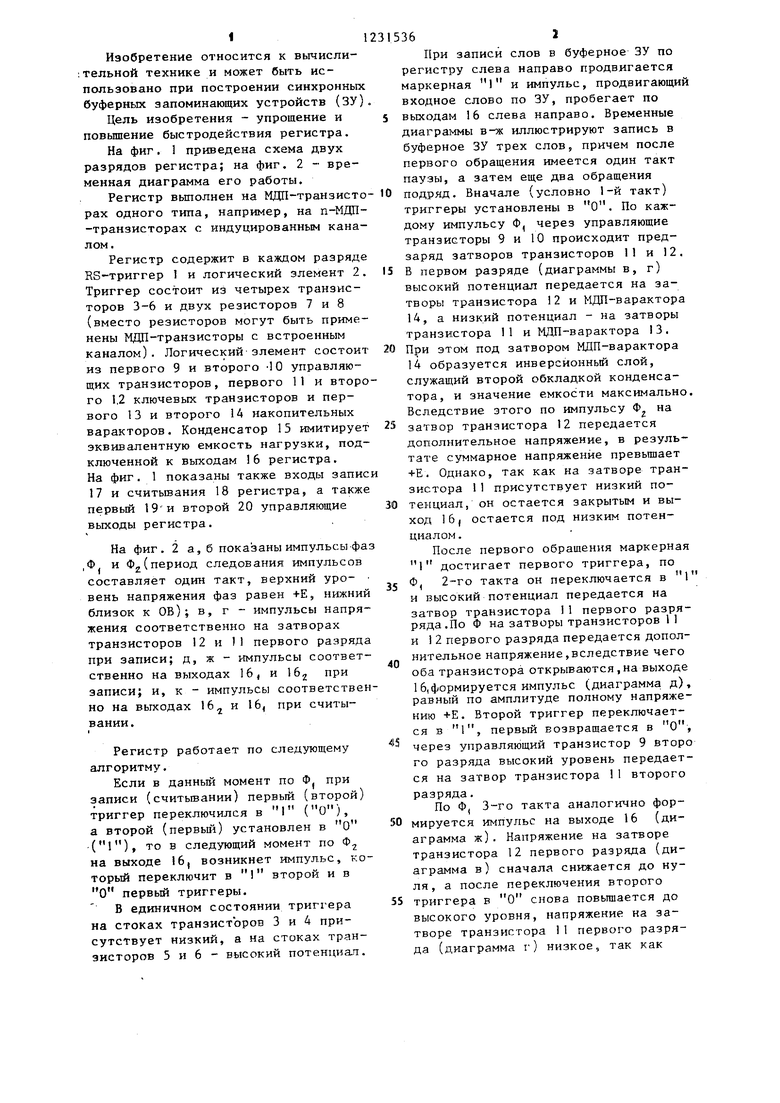

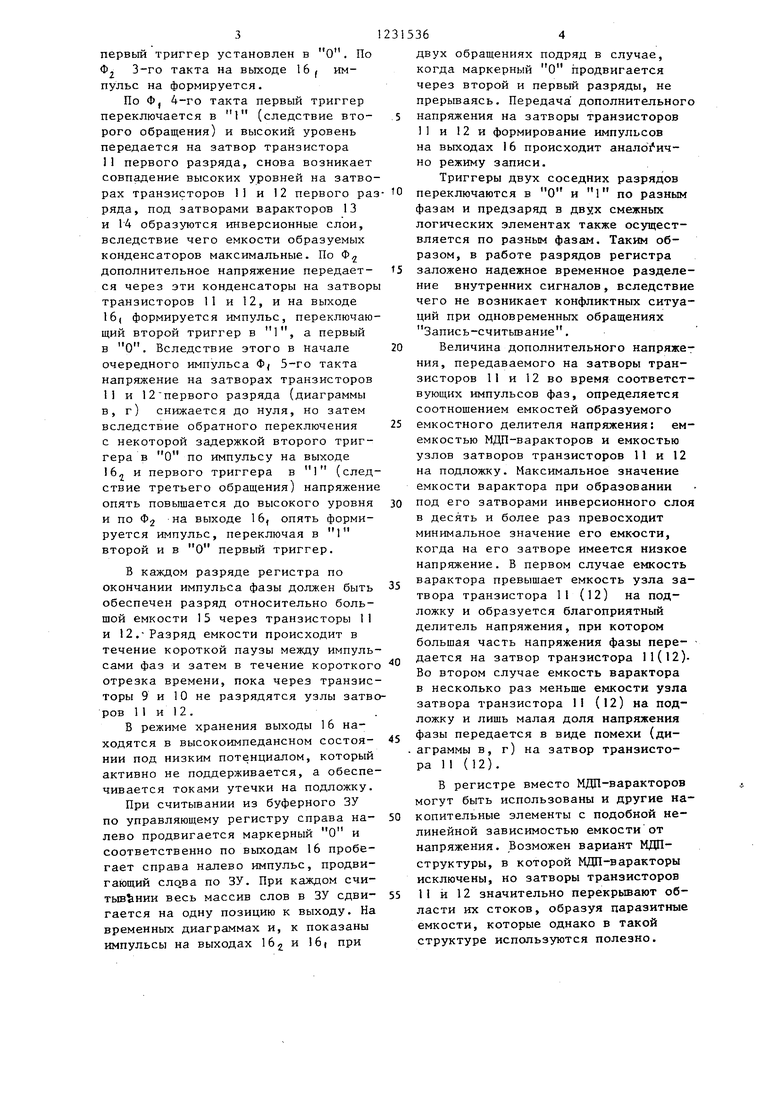

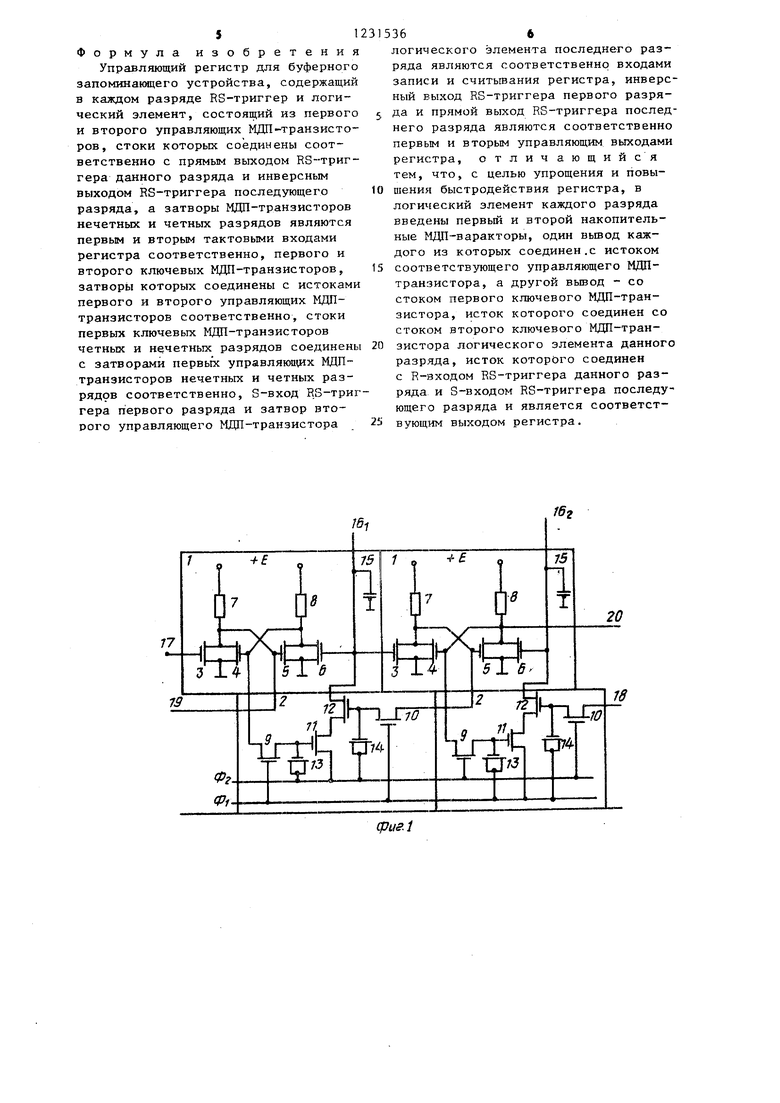

На фиг. 1 приведена схема двух разрядов регистра; на фиг. 2 - временная диаграмма его работы.

Регистр вьшолнен на МДП-транзисто pax одного типа, например, на п-МДП- -транзисторах с индуцированным каналом.

Регистр содержит в каждом разряде RS-триггер 1 и логический элемент 2. Триггер состоит из четырех транзисторов 3-6 и двух резисторов 7 и 8 (вместо резисторов могут быть применены МДП-транзисторы с встроенным каналом). Логический элемент состоит из первого 9 и второго 10 управляющих транзисторов, первого П и второго 1.2 ключевых транзисторов и первого 13 и второго 14 накопительных варакторов. Конденсатор 15 имитирует эквивалентную емкость нагрузки, подключенной к выходам 6 регистра, На фиг. 1 показаны также входы запис 17 и считьшания 18 регистра, а также первый 19 и второй 20 управляющие выходы регистра.

На фиг. 2 а, б показаны импульсы фаз ,Ф| и Ф2(период следования импульсов составляет один такт, верхний уро- вень напряжения фаз равен +Е, нижний близок к ОБ); в, г - импульсы напряжения соответственно на затворах транзисторов 12 и ) первого разряда при записи; д, ж - импульсы соответственно на выходах 16, и 16 при записи; и, к - импульсы соответственно на выходах 16 и 16, при считывании.

Регистр работает по следующему алгоритму.

Если в данный момент по Ф| при записи (считывании) первый (второй) триггер переключился в I (О), а второй (первьй) установлен в О (1), то в следующий момент по Ф на выходе 16, возникнет импульс, который переключит в второй и в О первый триггеры.

В единичном состоянии триггера на стоках транзисторов 3 и 4 присутствует низкий, а на стоках транзисторов 5 и 6 - высокий потенциап.

36J

При записи слов в буферное ЗУ по регистру слева направо продвигается маркерная 1 и импульс, продвигающий входное слово по ЗУ, пробегает по выходам 16 слева направо. Временные диагра1чмы в-ж иллюстрируют запись в буферное ЗУ трех слов, причем после первого обращения имеется один такт паузы, а затем еще два обращения подряд. Вначале (условно 1-й такт) триггеры установлены в О. По каждому импульсу Ф, через управляющие транзисторы 9 и 10 происходит пред- заряд затворов транзисторов 11 и 12, В первом разряде (диаграммы в, г) высокий потенциал передается на затворы транзистора 12 и МДП-варактора 14, а низкий потенциал - на затворы транзистора 11 и МДП-варактора 13. При этом под затвором МДП-варактора 14 образуется инверсионный слой, служащий второй обкладкой конденсатора, и значение емкости максимально. Вследствие этого по импульсу Ф на затвор транзистора 12 передается дополнительное напряжение, в результате суммарное напряжение превышает +Е. Однако, так как на затворе транзистора 11 присутствует низкий потенциал, он остается закрытым и выход 16| остается под низким потенциалом.

После первого обращения маркерная 1 достигает первого триггера, по

5

0

5

0

5

Ф, 2-го такта он переключается в

Т

и высокий потенциал передается на

затвор транзистора 1 первого разря- ряда.По Ф на затворы транзисторов I 1

и 1 2 первого разряда передается дополнительное напряжение,вследствие чего оба транзистора открываются , на выходе 1 6,формируется импульс (диаграмма д) , равный по амплитуде полному напряжению +Е. Второй триггер переключается в 1, первый возвращается в О, через управляющий транзистор 9 второ го разряда высокий уровень передается на затвор транзистора 11 второго

разряда.

По Ф, 3-го такта аналогично формируется импульс на выходе 16 (диаграмма ж). Напряжение на затворе транзистора 12 первого разряда (диаграмма в) сначала снижается до нуля , а после переключения второго триггера в О снова повьпиается до высокого уровня, напряжение на затворе транзистора 11 первого разряда (диаграмма г) низкое, так как

3

первый триггер установлен в О. По Ф 3-го такта на выходе 16, импульс на формируется.

По Ф, 4-го такта первый триггер переключается в 1 (следствие вто- рого обращения) и высокий уровень передается на затвор транзистора 11 первого разряда, снова возникает совпадение высоких уровней на затворах транзисторов П и 12 первого раз ряда, под затворами варакторов 13 и 14 образуются инверсионные слои, вследствие чего емкости образуемых конденсаторов максимальные. По Ф дополнительное напряжение передает- ся через эти конденсаторы на затворы транзисторов 11 и 12, и на выходе 16, формируется импульс, переключающий второй триггер в 1, а первый в О, Вследствие этого в начале очередного импульса Ф 5-го такта напряжение на затворах транзисторов 11 и 12 первого разряда (диаграммы в, г) снижается до нуля, но затем вследствие обратного переключения с некоторой задержкой второго триггера в О по импульсу на выходе 16 и первого триггера в 1 (следствие третьего обращения) напряжение опять повышается до высокого уровня и по Ф на выходе 16, опять формируется импульс, переключая в 1 второй и в О первый триггер.

В каждом разряде регистра по окончании импульса фазы должен быть обеспечен разряд относительно большой емкости 15 через транзисторы 11 и 12.-Разряд емкости происходит в течение короткой паузы между импульсами фаз и затем в течение короткого отрезка времени, пока через транзисторы 9 и 10 не разрядятся узлы затворов 1 1 и 1 2 .

В режиме хранения выходы 16 находятся в высокоимпедансном состоя- НИИ под низким потенциалом, который активно не поддерживается, а обеспечивается токами утечки на подложку.

При считывании из буферного ЗУ по управляющему регистру справа на- лево продвигается маркерный О и соответственно по выходам 16 пробегает справа налево импульс, продвигающий сло.ва по ЗУ. При каждом счи- тьшЬнии весь массив слов в ЗУ сдви- гается на одну позицию к выходу. На временных диаграммах и, к показаны импульсы на выходах 162 и 6| при

364

двух обращениях подряд в случае, когда маркерный О продвигается через второй и первый разряды, не прерываясь. Передача дополнительного напряжения на затворы транзисторов 11 и 12 и формирование импульсов на выходах I6 происходит анало ич- но режиму записи.

Триггеры двух соседних разрядов переключаются в О и 1 по разным фазам и предзаряд в двух смежных логических элементах также осуществляется по разным фазам. Таким образом, в работе разрядов регистра заложено надежное временное разделение внутренних сигналов, вследствие чего не возникает конфликтных ситуаций при одновременных обращениях Запись-считьшание.

Величина дополнительного напряжения, передаваемого на затворы транзисторов 11 и 12 во время соответствующих импульсов фаз, определяется соотношением емкостей образуемого емкостного делителя напряжения: ем- емкостью МДП-варакторов и емкостью узлов затворов транзисторов 11 и 12 на подложку. Максимальное значение емкости варактора при образовании под его затворами инверсионного слоя в десять и более раз превосходит минимальное значение его емкости, когда на его затворе имеется низкое напряжение. В первом случае емкость варактора превышает емкость узла затвора транзистора 11 (12) на подложку и образуется благоприятный делитель напряжения, при котором большая часть напряжения фазы пере- дается на затвор транзистора 11(12)- Во втором случае емкость варактора в несколько раз меньше емкости узла затвора транзистора II (12) на подложку и лишь малая доля напряжения фазы передается в виде помехи (ди- аграммы в, г) на затвор транзистора 11 (12).

В регистре вместо МДП-варакторов могут быть использованы и другие накопительные элементы с подобной нелинейной зависимостью емкости от напряжения. Возможен вариант МДП- структуры, в которой МДП-варакторы исключены, но затворы транзисторов 11 и 12 значительно перекрьшают области их стоков, образуя паразитные емкости, которые однако в такой структуре используются полезно.

51

Формула изобретения Управляющий регистр для буферного запоминающего устройства, содержащий в каждом разряде RS-триггер и логический элемент, состоящий из первого и второго управляющих МДП-транзисто- ров, стоки которых соединены соответственно с прямым выходом RS-триг- гера данного разряда и инверсным выходом RS-триггера последующего разряда, а затворы МДП-транзисторов нечетных и четных разрядов являются первым и вторым тактовыми входами регистра соответственно, первого и второго ключевых МДП-транзисторов, затворы которых соединены с истоками первого и второго управляющих МДП- транзисторов соответственно, стоки первых ключевых МДП-транзисторов четных и нечетных разрядов соединены с затворами первьгх управляюиуих МДП- транзисторов нечетных и четных раз- рядрв соответственно, З-вход RS-триг гера первого разряда и затвор второго управляющего МДП-транзистора

315366

логического элемента последнего разряда являются соответственно входами записи и считьдаания регистра, инверсный выход RS-триггера первого разря- 5 да и прямой выход RS-триггера последнего разряда являются соответственно первым и вторым управляющим выходами регистра, отлич ающийся тем, что, с целью упрощения и повы10 шения быстродействия регистра, в логический элемент каждого разряда введены первый и второй накопительные МДП-варакторы, один вьшод каждого из которых соединен.с истоком

15 соответствующего управляющего МДП- транзистора, а другой вывод - со стоком первого ключевого МДП-транзистора, исток которого соединен со стоком второго ключевого МДП-тран20 зистора логического элемента данного разряда, исток которого соединен с R-входом RS-триггера данного разряда и S-входом RS-триггера последующего разряда и является соответст5 вующ:нм выходом регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр для буферного запоминающего устройства | 1984 |

|

SU1170511A1 |

| Динамический регистр сдвига | 1988 |

|

SU1671047A1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Динамический сдвиговый регистр | 1981 |

|

SU993334A1 |

| ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2542913C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

Изобретение относится к вычислительной технике. Целью изобретения является упрощение и повышение быстродействия регистра, предназначенно-- го для управления работой буферного запоминающего устройства. Каждый разряд регистра состоит из RS-триг- гераи логического элемента. Поставленная цель достигается введением в каждый логичес :ий элемент двух накопительных МДП-варакторов, позво- лякяцих получать надежное временное разделение внутренних сигналов и создавать дополнительные напряжения на затворах ключевых транзисторов логического элемента во время действия тактовых импульсов. 2 ил.

20

1танг , 2тант , Зтант . 4гамт. 5 тан т. бгонт

| Автоматика, 979, № 2, с | |||

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микроэлектроника, 1982, т | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-15—Публикация

1984-06-19—Подача