Изобретение относится к радиотехнике и может быть использовано в радиоприемных устройствах для формирования частот в гетеродинах.

Цель изобретения - уменьшение шага сетки частот при сохранении быстродействия.

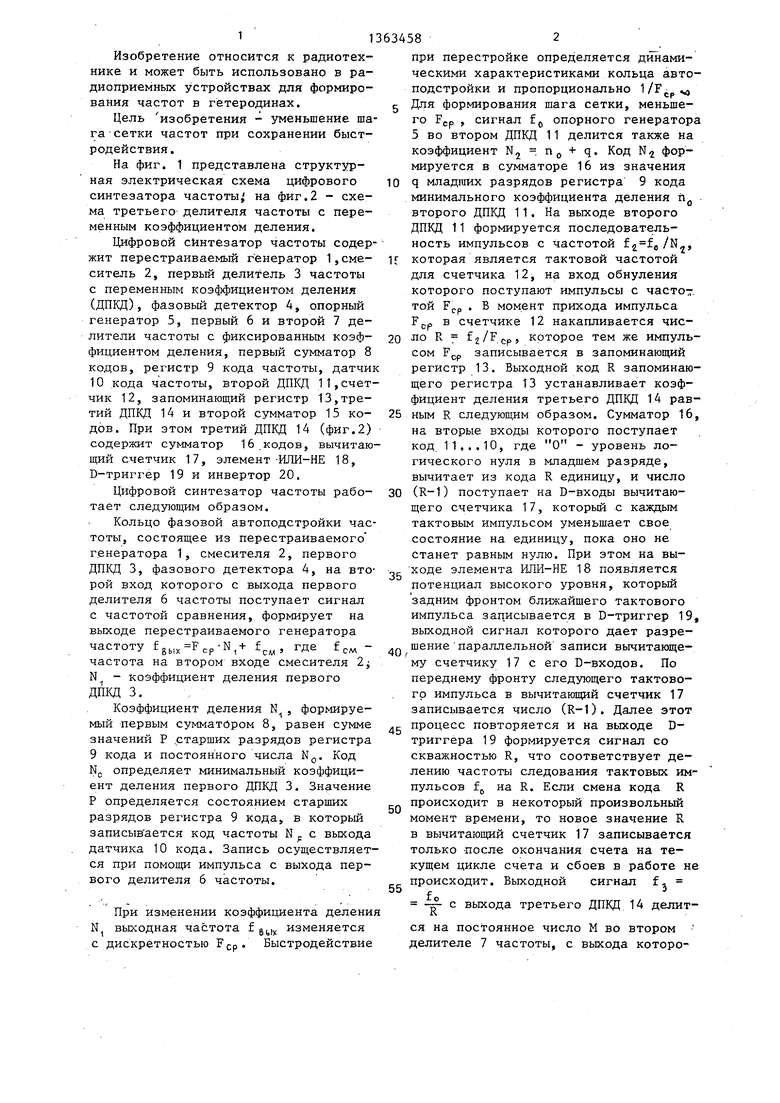

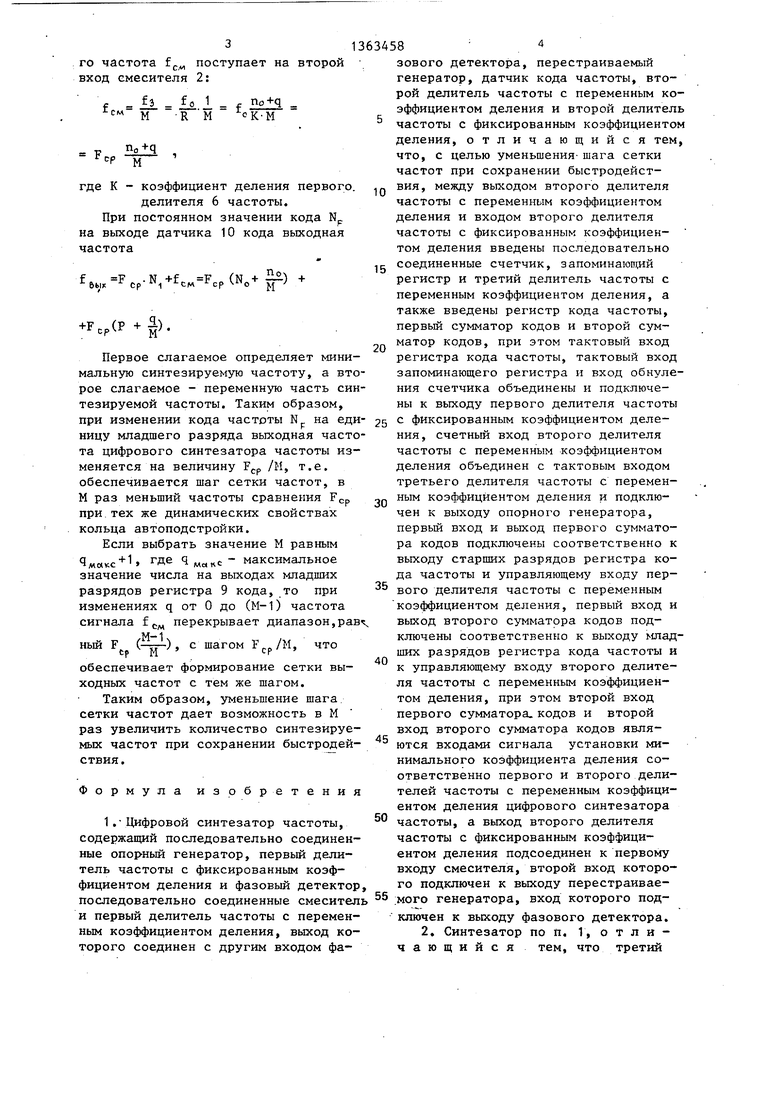

На фиг. 1 представлена структурная электрическая схема цифрового синтезатора частоты, на фиг.2 - схема третьего делителя частоты с переменным коэффициентом деления.

Цифровой синтезатор частоты содер- жит перестраиваемый генератор 1,смеситель 2, первый делитель 3 частоты с переменным коэффициентом деления (ДПКД), фазовый детектор 4, опорный генератор 5, первый 6 и второй 7 делители частоты с фиксированньш коэффициентом деления, первый сумматор 8 кодов, регистр 9 кода частоты, датчик 10 кода частоты, второй ДПКД 11,счетчик 12, запоминающий регистр 13,третий ДПКД 14 и второй сумматор 15 кодов. При этом третий ДПКД 14 (фиг.2) содержит сумматор 16 кодов, вычитающий счетчик 17, элемент -ИЛИ-НЕ 18, D-триггер 19 и инвертор 20,

Цифровой синтезатор частоты работает следующим образом.

Кольцо фазовой автоподстройки частоты, состоящее из перестраиваемого генератора 1, смесителя 2, первого ДПКД 3, фазового детектора 4, на второй вход которого с выхода первого делителя 6 частоты поступает сигнал с частотой сравнения, формирует на выходе перестраиваемого генератора

fR,,,F

N,+

-см

где

ем

2i

частота на втором входе смесителя N - коэффициент деления первого ДПКД 3.

Коэффициент деления N, формируемый первым сумматором 8, равен сумме значений Р ртарших разрядов регистра 9 кода и постоянного числа N,. Код Ng определяет минимальный коэффициент деления первого ДПКД 3. Значение Р определяется состоянием старших разрядов регистра 9 кода, в который записыв ается код частоты N с выхода датчика 10 кода. Запись осуществляется при помощи импульса с выхода первого делителя 6 частоты.

При изменении коэффициента деления

N выходная частота

6 их

изменяется

с дискретностью Fcp. Быстродействие

при перестройке определяется динамическими характеристиками кольца автоподстройки и пропорционально 1/F10

СР 5 Для формирования шага сетки, меньшего Fgp , сигнал fjj опорного генератор 5 во втором ДПКД 11 делится также на коэффициент Nj . п + q. Код N формируется в сумматоре 16 из значения q младших разрядов регистра 9 кода минимального коэффициента деления второго ДПКД 11. На выходе второго ДПКД 11 формируется последовательность импульсов с частотой f2 fe/Nj, которая является тактовой частотой для счетчика 12, на вход обнуления которого поступают импульсы с часто-, той . В момент прихода импульса в счетчике 12 накапливается чисU

20

ср ло R

f,/F

ср

30

35

которое тем же импульсом F записывается в запоминающий регистр 13. Выходной код R запоминающего регистра 13 устанавливает коэффициент деления третьего ДПКД 14 рав- 25 ным R следующим образом. Сумматор 16, на вторые входы которого поступает код 11... 10, где О - уровень логического нуля в младшем разряде, вычитает из кода R единицу, и число (R-1) поступает на D-входы вычитающего счетчика 17, которьй с каждым тактовым импульсом уменьшает свое состояние на единицу, пока оно не станет равным нулю. При этом на выходе элемента ИЛИ-НЕ 18 появляется потенциал высокого уровня, который задним фронтом ближайшего тактового импульса зацисывается в D-триггер 19, выходной сигнал которого дает разрешение параллельной записи вычитающему счетчику 17 с его D-входов. По переднему фронту следующего тактового импульса в вычитающий счетчик 17 записывается число (R-1). Далее этот процесс повторяется и на выходе D- триггера 19 формируется сигнал со скважностью R, что соответствует делению частоты следования тактовых импульсов f на R. Если смена кода R происходит в некоторый произвольный момент времени, то новое значение R в вычитаюш51й счетчик 17 записывается только после окончания счета на текущем цикле счета и сбоев в работе не происходит. Выходной сигнал

40

45

50

55

3

JLo

-: с выхода третьего ДПКД 14 делит- к

ся на постоянное число М во втором делителе 7 частоты, с выхода которого частота f поступает на второй вход смесителя 2:

ll io 1 - М -R М

t - /-о - f

ТГ ТГ 77 1по+q

«К-М

Пр+д

ср М

где К - коэффициент деления первого.

делителя 6 частоты. При постоянном значении кода Np на выходе датчика 10 кода выходная частота

«

f6b,.Fcp-N fcM Fcp(Nc) +

F.pCP

Первое слагаемое определяет минимальную синтезируемую частоту, а второе слагаемое - переменную часть синтезируемой частоты. Таким образом, при изменении кода частоты N на еди- ницу младшего разряда выходная частота цифрового синтезатора частоты изменяется на величину F(,p /М, т.е. обеспечивается шаг сетки частот, в М раз меньший частоты сравнения при тех же динамических свойствах кольца автоподстройки.

Если выбрать значение М равным + 1 где максимальное значение числа на выходах младших разрядов регистра 9 кода, то при изменениях q от О до (М-1) частота сигнала t перекрывает диапазон,рав

ный F (-jT-) с шагом F /М, что

ср и г

обеспечивает формирование сетки выходных частот с тем же шагом.

Таким образом, уменьшение шага сетки частот дает возможность в М раз увеличить количество синтезируемых частот при сохранении быстродей- ствия.

Формула изобретения

1. Цифровой синтезатор частоты, содержащий последовательно соединенные опор-ный генератор, первый делитель частоты с фиксированным коэффициентом деления и фазовый детектор, последовательно соединенные смеситель и первый делитель частоты с переменным коэффициентом деления, выход которого соединен с другим входом фа0

5

0

5 Q

зового детектора, перестраиваемый генератор, датчик кода частоты, второй делитель частоты с переменным коэффициентом деления и второй делитель частоты с фиксированным коэффициентом деления, отличающийся тем, что, с целью уменьшения- шага сетки частот при сохранении быстродействия, между выходом второго делителя частоты с переменным коэффициентом деления и входом второго делителя частоты с фиксированным коэффициентом деления введены последовательно соединенные счетчик, запоминаюпц й регистр и третий делитель частоты с переменным коэффициентом деления, а также введены регистр кода частоты, первый сумматор кодов и второй сумматор кодов, при этом тактовый вход регистра кода частоты, тактовый вход запоминающего регистра и вход обнуления счетчика объединены и подключены к выходу первого делителя частоты с фиксированным коэффициентом деления, счетный вход второго делителя частоты с переменным коэффициентом деления объединен с тактовым входом третьего делителя частоты с переменным коэффициентом деления и подключен к выходу опорного генератора, первьш вход и выход первого сумматора кодов подключены соответственно к выходу старших разрядов регистра кода частоты и управляющему входу первого делителя частоты с переменным коэффициентом деления, первый вход и выход второго сумматора кодов подключены соответственно к выходу младших разрядов регистра кода частоты и к управляющему входу второго делителя частоты с переменным коэффициентом деления, при этом второй вход первого сумматора, кодов и второй вход второго сумматора кодов являются входами сигнала установки минимального коэффициента деления соответственно первого и второго делителей частоты с переменным коэффициентом деления цифрового синтезатора частоты, а выход второго делителя частоты с фиксированным коэффициентом деления подсоединен к первому входу смесителя, второй вход которого подключен к выходу перестраиваемого генератора, вход которого подключен к выходу фазового детектора. 2. Синтезатор по п. 1, о т л и - чающийся тем, что третий

делитель частоты с переменным коэффициентом, деления содержит последовательно соединенные сумматор кодов, вычитающий счетчик, элемент ИЛИ-НЕ и D-триг гер, а также инвертор, выход которого подключен к тактовому входу D-триггера, выход которого соединен с выходом разрешения параллельной записи вычитающего счетчика и является выходом третьего делителя частоты с переменньм коэффициентом дет л;ения, вход инвертора объединен с тактовым входом вычитающего счетчика и является тактовым входом третьего

Лог.

h

Составитель Ю.Ковалев Редактор А.Огар Техред М.Дидык Корректор А.Обручар

Заказ 6379/53 Тираж 900.Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 11303 5, Москва, Ж-35, Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4.

делителя частоты с переменным коэффициентом деления, выход переноса сумматора кодов соединен с входом звена сумматора кодов, первый кодовый вход которого является управляющим входом третьего делителя частоты с переменным коэффициентом деления, младший разряд второго кодового входа сумматора кодов является входом логического нуля сумматора кодов, остальные разряды второго кодового входа объединены и являются входом логической единицы сумматора кодов.

D Г7

i8 I ±

г- г

IS

г- С

20

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты | 1986 |

|

SU1356222A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1234966A1 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Цифровой синтезатор частоты | 1984 |

|

SU1172011A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой синтезатор частот | 1987 |

|

SU1494215A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

Изобретение относится к радиотехнике и м.б. использовано в радиоприемных устр-вах формирования частот в гетеродинах. Целью изобретения является уменьшение шага сетки частот при сохранении быстродействия. Цифровой синтезатор частоты содержит перестраиваемый генератор 1, смеситель 2, два делителя частоты с переменным коэф. деления (ДПКД) 3, 11, фазовый детектор 4, опорньй генератор 5, два делителя частоты с фиксированньм коэф. деления, датчик кода частоты 10. Для достижения цели введены сумматоры кодов 8, 15, регистр кода частоты 9, счетчик 12, запоминающий регистр 13, третий ДПКД 14. При изменении кода частоты N на единицу младшего разряда выходная частота циф- . рового синтезатора частоты изменяется на величину F /М, т.е. обеспечивается шаг сетки частот, в М раз меньший частоты сравнения F при тех же динамических св-вах кольца автоподстройки. За счет уменьшения шага сетки частот возможно в М раз уве- {личить кол-во синтезируемых частот при сохранении быстродействия. 2 ил. i (Л л./,

| Цифровой синтезатор частоты | 1982 |

|

SU1109912A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Манассевич В | |||

| Синтезаторы частот | |||

| Теория и проектирование | |||

| М.: Связь, 1979, с | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

Авторы

Даты

1987-12-30—Публикация

1986-06-10—Подача