ел

С

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2021632C1 |

| Устройство для деления | 1991 |

|

SU1784974A1 |

| Устройство для деления | 1990 |

|

SU1721603A1 |

| Устройство для деления | 1989 |

|

SU1633395A1 |

| Асинхронное матричное устройство для деления | 1982 |

|

SU1022157A1 |

| Устройство для деления чисел | 1989 |

|

SU1711151A1 |

| Устройство для контроля делительного блока | 1983 |

|

SU1115056A1 |

| Устройство для деления | 1983 |

|

SU1151955A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| УСТРОЙСТВО ДЛЯ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2013 |

|

RU2559771C2 |

Изобретение относится к автоматике и вычислительной технике и может использоваться при построении арифметических устройств. Цель изобретения - повышение достоверности результата вычислений устройства. Устройство содержит группу M сумматоров 1, узлы 2 - 5 свертки по модулю два, узлы 6, 7 сравнения. Цель изобретения достигается путем сравнения полученной и предсказанной четности. Предсказанная четность формируется из сигналов четности делимого и делителя и четности внутренних межразрядных сигналов переноса сумматоров группы 1 узлом 2 свертки по модулю два. Полученная четность формируется узлом 3 свертки по модулю два. Сравнение осуществляется узлом 6 сравнения. 5 ил.

о о

4

О -ч|

is

17

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении арифметических устройств.

Целью изобретения является повыше- ние достоверности результата вычислений устройства.

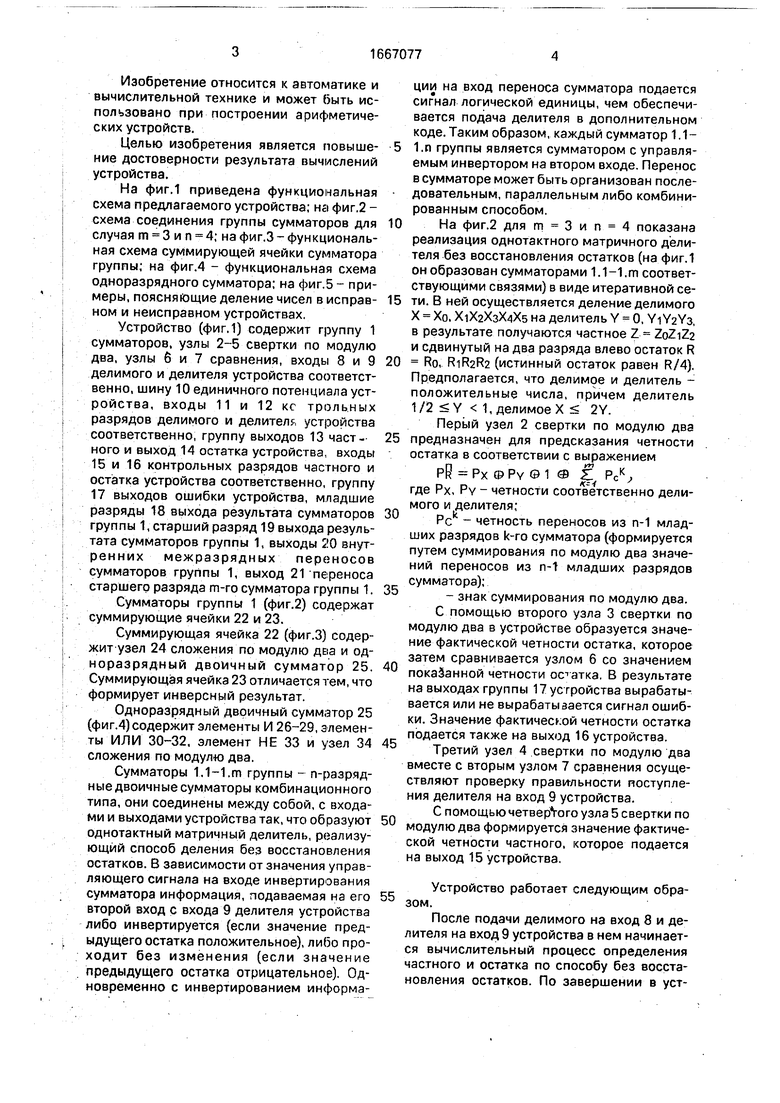

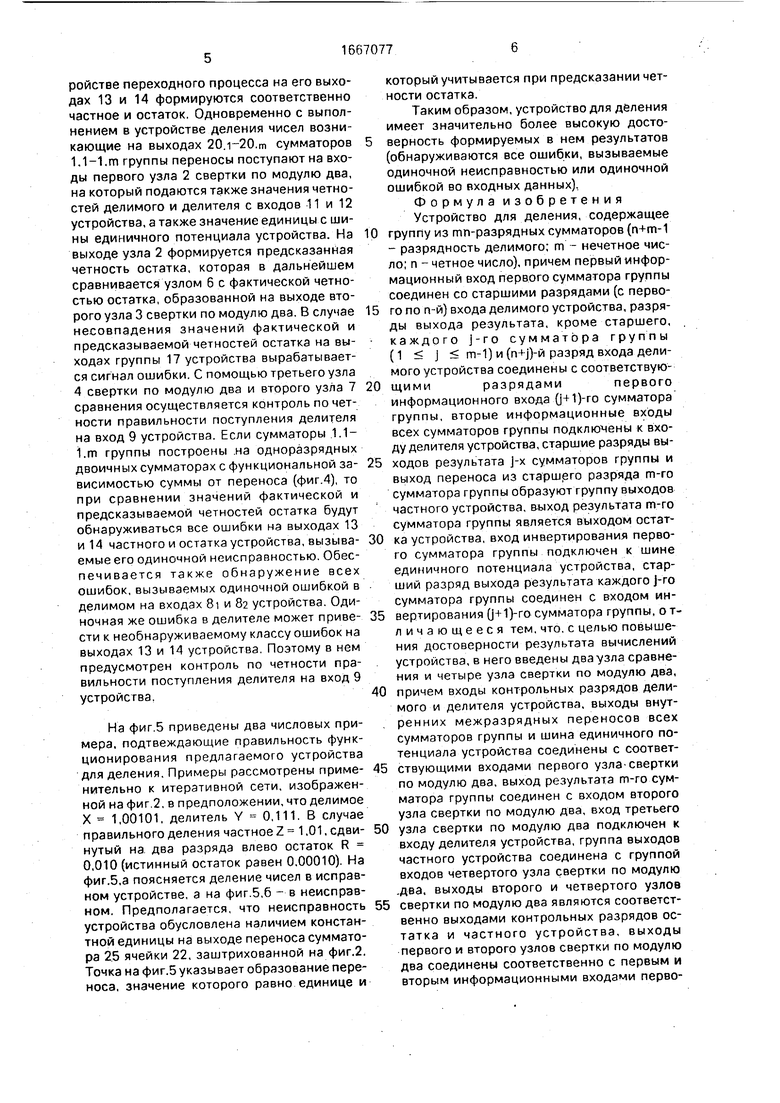

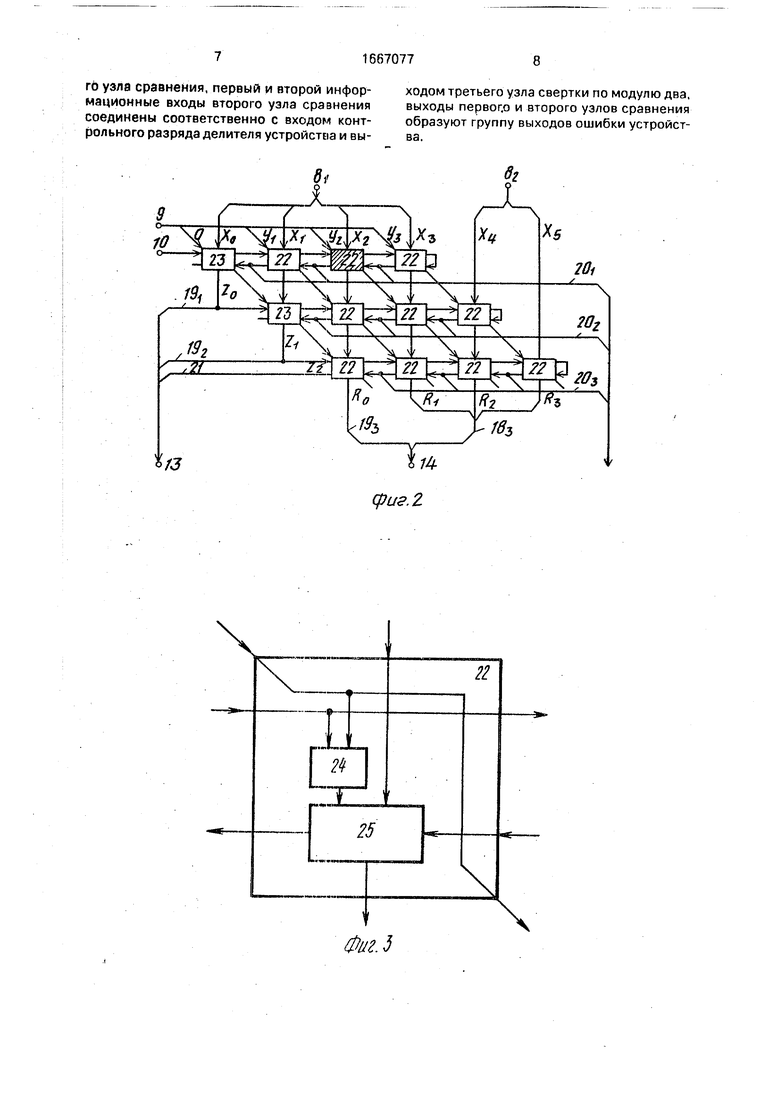

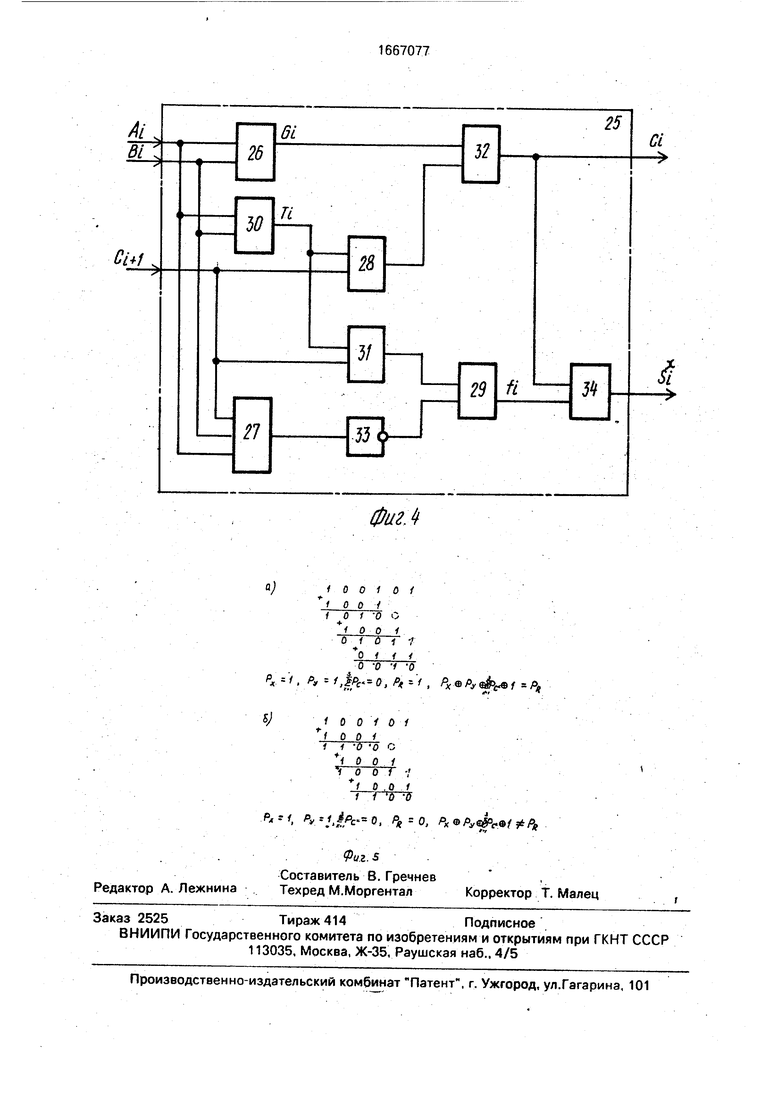

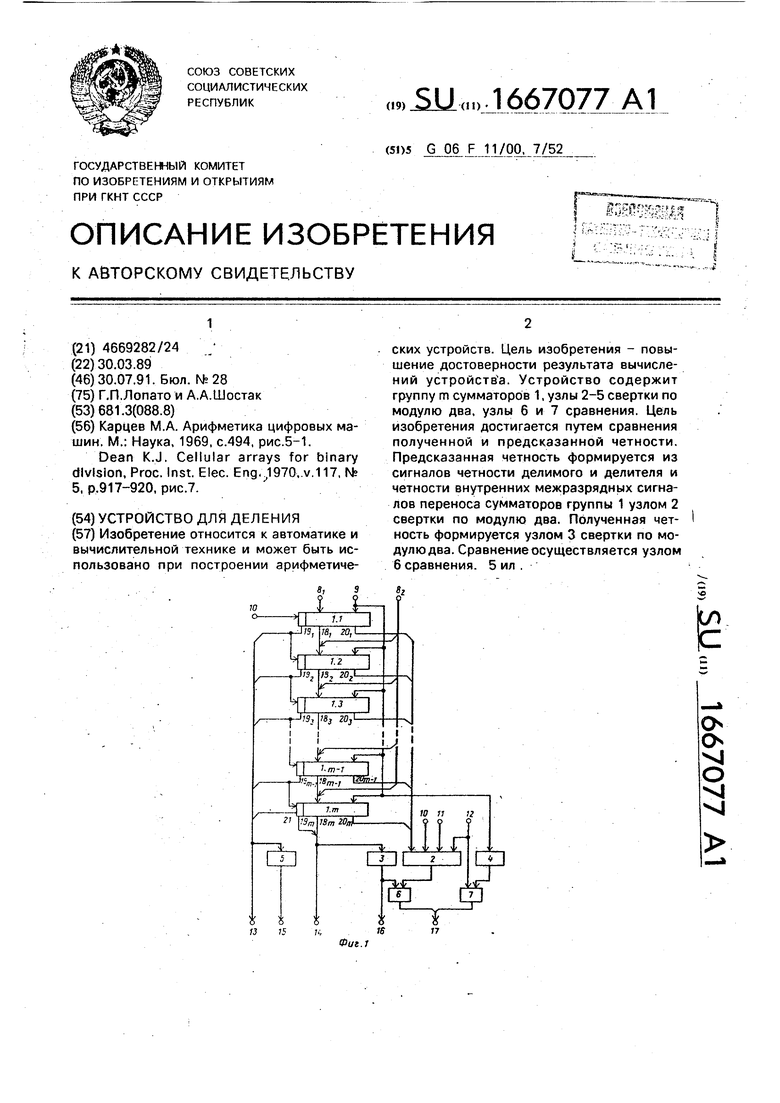

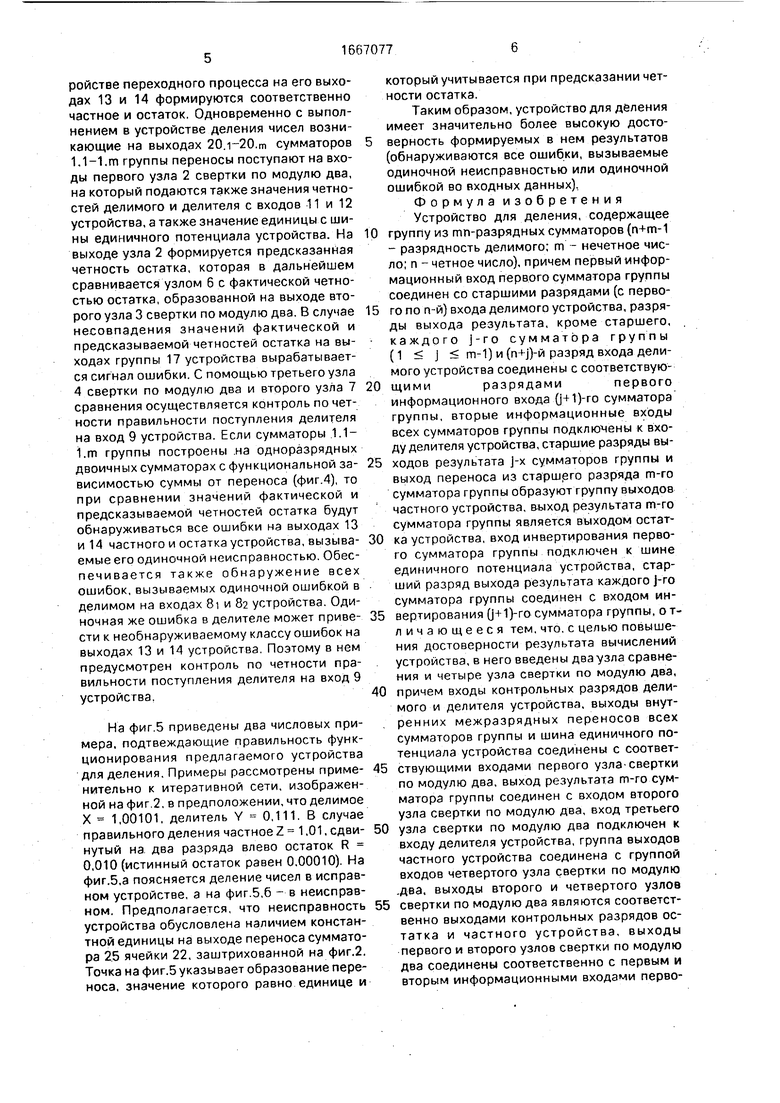

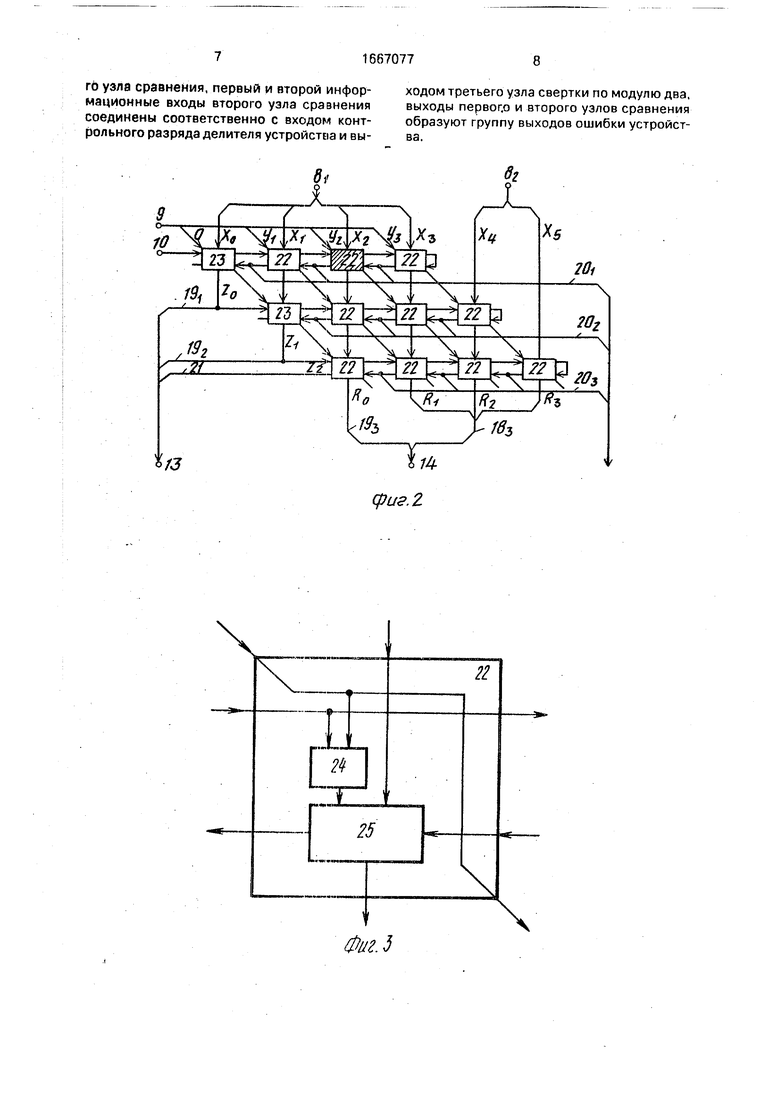

На фиг.1 приведена функциональная схема предлагаемого устройства; на фиг.2 - схема соединения группы сумматоров для случая m 3 и п 4; на фиг.З - функциональная схема суммирующей ячейки сумматора группы; на фиг.4 - функциональная схема одноразрядного сумматора; на фиг.5 - примеры, поясняющие деление чисел в исправ- ном и неисправном устройствах.

Устройство (фиг.1) содержит группу 1 сумматоров, узлы 2-5 свертки по модулю два, узлы 6 и 7 сравнения, входы 8 и 9 делимого и делителя устройства соответственно, шину 10 единичного потенциала устройства, входы 11 и 12 кс трольных разрядов делимого и делителя устройства соответственно, группу выходов 13 част- ного и выход 14 остатка устройства, входы 15 и 16 контрольных разрядов частного и остатка устройства соответственно, группу 17 выходов ошибки устройства, младшие разряды 18 выхода результата сумматоров группы 1, старший разряд 19 выхода результата сумматоров группы 1, выходы 20 внутренних межразрядных переносов сумматоров группы 1, выход 21 переноса старшего разряда т-го сумматора группы 1,

Сумматоры группы 1 (фиг.2) содержат суммирующие ячейки 22 и 23.

Суммирующая ячейка 22 (фиг.З) содержит узел 24 сложения по модулю два и одноразрядный двоичный сумматор 25. Суммирующая ячейка 23 отличается тем, что формирует инверсный результат.

Одноразрядный двоичный сумматор 25 (фиг.4) содержит элементы И 26-29, элементы ИЛИ 30-32, элемент НЕ 33 и узел 34 сложения по модулю два.

Сумматоры 1.1-1.т группы - п-разряд- ные двоичные сумматоры комбинационного типа, они соединены между собой, с входами и выходами устройства так, что образуют однотактный матричный делитель, реализующий способ деления без восстановления остатков. В зависимости от значения управляющего сигнала на входе инвертирования сумматора информация, подаваемая на его второй вход с входа 9 делителя устройства либо инвертируется (если значение предыдущего остатка положительное), либо проходит без изменения (если значение предыдущего остатка отрицательное). Одновременно с инвертированием информации на вход переноса сумматора подается сигнал логической единицы, чем обеспечивается подача делителя в дополнительном коде. Таким образом, каждый сумматор 1.1- 1.п группы является сумматором с управляемым инвертором на втором входе. Перенос в сумматоре может быть организован последовательным, параллельным либо комбинированным способом.

На фиг.2 для m 3 и п 4 показана реализация однотактного матричного делителя без восстановления остатков (на фиг.1 он образован сумматорами 1.1-1.т соответствующими связями) в виде итеративной сети. В ней осуществляется деление делимого X Хо. Х1Х2ХзХ4Х5 на делитель Y 0, YiY2Y3. в результате получаются частное Z ZoZiZ2 и сдвинутый на два разряда влево остаток R Ro, RiR2R2 (истинный остаток равен R/4). Предполагается, что делимое и делитель - положительные числа, причем делитель 1/2 Y 1, делимое X 2Y.

Перый узел 2 свертки по модулю два предназначен для предсказания четности

остатка в соответствии с выражением

-S

PR Рх Ф PY © 1 « SY PC где РХ, PY - четности соответственно делимого и делителя;

Pck - четность переносов из п-1 младших разрядов k-го сумматора (формируется путем суммирования по модулю два значений переносов из п-1 младших разрядов сумматора);

- знак суммирования по модулю два.

С помощью второго узла 3 свертки по модулю два в устройстве образуется значение фактической четности остатка, которое затем сравнивается узлом 6 со значением показанной четности остатка. В результате на выходах группы 17устройства вырабатывается или не вырабатывается сигнал ошибки. Значение фактической четности остатка подается также на выход 16 устройства.

Третий узел 4 свертки по модулю два вместе с вторым узлом 7 сравнения осуществляют проверку правильности поступления делителя на вход 9 устройства.

С помощью четвертого узла 5 свертки по модулю два формируется значение фактической четности частного, которое подается на выход 15 устройства.

Устройство работает следующим образом.

После подачи делимого на вход 8 и делителя на вход 9 устройства в нем начинается вычислительный процесс определения частного и остатка по способу без восстановления остатков. По завершении в устройстве переходного процесса на его выходах 13 и 14 формируются соответственно частное и остаток. Одновременно с выполнением в устройстве деления чисел возни кающие на выходах 20.i-20.m сумматоров 1.1-1.т группы переносы поступают на входы первого узла 2 свертки по модулю два, на который подаются также значения четно- стей делимого и делителя с входов 11 и 12 устройства, а также значение единицы с шины единичного потенциала устройства. На выходе узла 2 формируется предсказанная четность остатка, которая в дальнейшем сравнивается узлом 6 с фактической четностью остатка, образованной на выходе второго узла 3 свертки по модулю два. В случае несовпадения значений фактической и предсказываемой четностей остатка ня выходах группы 17 устройства вырабатывается сигнал ошибки. С помощью третьего узла 4 свертки по модулю два и второго узла 7 сравнения осуществляется контроль по четности правильности поступления делителя на вход 9 устройства. Если сумматоры 1.1- 1.т группы построены на одноразрядных двоичных сумматорах с функциональной зависимостью суммы от переноса (фиг 4). то при сравнении значений фактической и предсказываемой четностей остатка будут обнаруживаться все ошибки на выходах 13 и 14 частного и остатка устройства, вызываемые его одиночной неисправностью Обес- печивается также обнаружение всех ошибок, вызываемых одиночной ошибкой в делимом на входах 8i и 82 устройства Одиночная же ошибка в делителе может привести к необнаруживаемому классу ошибок на выходах 13 и 14 устройства. Поэтому в нем предусмотрен контроль по четности правильности поступления делителя на вход 9 устройства.

На фиг 5 приведены два числовых примера, подтвеждающие правильность функционирования предлагаемого устройства для деления. Примеры рассмотрены применительно к итеративной сети, изображенной на фиг 2, в предположении, что делимое X 1.00101, делитель Y - 0.111. В случае правильного деления частное Z 1,01,сдвинутый на два разряда влево остаток R 0,010 (истинный остаток равен 0.00010) На фиг.5,а поясняется деление чисел в исправном устройстве, а на фиг 5,6 - в неисправном. Предполагается, что неисправность устройства обусловлена наличием константной единицы на выходе переноса сумматора 25 ячейки 22, заштрихованной на фиг.2. Точка на фиг.5 указывает образование переноса, значение которого равно единице и

который учитывается при предсказании четности остатка.

Таким образом, устройство для деления имеет значительно более высокую достоверность формируемых в нем результатов (обнаруживаются все ошибки, вызываемые одиночной неисправностью или одиночной ошибкой во входных данных).

Формула изобретения Устройство для деления, содержащее

0 группу из mn-разрядных сумматоров (n-f-m-1 - разрядность делимого; m - нечетное число; п - четное число), причем первый информационный вход первого сумматора группы соединен со старшими разрядами (с перво5 го по n-й) входа делимого устройства, разряды выхода результата, кроме старшего, каждого j-ro сумматора группы (1 j m-1) и (mj)-H разряд входа делимого устройства соединены с соответствую0 щимиразрядамипервого

информационного входа (j-M)-ro сумматора группы, вторые информационные входы всех сумматоров группы подключены к входу делителя устройства, старшие разряды вы5 ходов результата j-x сумматоров группы и выход переноса из старшего разряда т-го сумматора группы образуют группу выходов частного устройства, выход результата т-го сумматора группы является выходом остат0 ка устройства, вход инвертирования первого сумматора группы подключен к шине единичного потенциала устройства, старший разряд выхода результата каждого J-ro сумматора группы соединен с входом ин5 вертирования Q+1)-ro сумматора группы, о т- личающееся тем, что. с целью повышения достоверности результата вычислений устройства, в него введены два узла сравнения и четыре узла свертки по модулю два,

0 причем входы контрольных разрядов делимого и делителя устройства, выходы внутренних межразрядных переносов всех сумматоров группы и шина единичного потенциала устройства соединены с соответ5 ствующими входами первого узла свертки по модулю два. выход результата т-го сумматора группы соединен с входом второго узла свертки по модулю два, вход третьего

0 узла свертки по модулю два подключен к входу делителя устройства, группа выходов частного устройства соединена с группой входов четвертого узла свертки по модулю два, выходы второго и четвертого узлов

5 свертки по модулю два являются соответственно выходами контрольных разрядов остатка и частного устройства, выходы первого и второго узлов свертки по модулю два соединены соответственно с первым и вторым информационными входами первого узла сравнения, первый и второй информационные входы второго узла сравнения соединены соответственно с входом контрольного разряда делителя устройства и выходом третьего узла свертки по модулю два, выходы первог.о и второго узлов сравнения образуют группу выходов ошибки устройства.

Фиг. 3

Ai

Bl

26

Gi

W

П

21

100101

I С 1 О О

% 0 0 f О f (Г 1 /

о

о -о / -о

рд - , - tJPC sO, , Рх в/в,

0 0 1 0 1

о о 1 f -о -о о

00 /

5 о -/ о о

52

25

a

29

ft

tt

jf

-

534фигЛ

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М.: Наука, 1969, с.494, рис.5-1 | |||

| Dean K.J | |||

| Cellular arrays for binary division, Proc | |||

| Inst | |||

| Elec | |||

| Eng.,1970, v.117, № 5, p.917-920, рис.7. |

Авторы

Даты

1991-07-30—Публикация

1989-03-30—Подача