Изобр€(тенне отнсхгится к вычислительной технике и может быть применено в специализированных цифровых вычислителях..

Известно устройство для вычисле.ния квадратного корня из суммы квадратов .двух чисел, содержащее сумматор и коммутатор ij.

Недостатками этого устройства являются низкая точйость вычисления и относительно низкое быстродействие.

НёШболеё близки 4 к предлагаемому по технической сущности является устройствЬв для вычисления квадратно го корня йэ суммы квадратов двух чисел, содержащее коммутатор и сумматор, причем первые и вторые входы коммутатора подключены- соответственно ко входным шинаМ величин хи у, а выход - ко входу сумматора. Цикл вычислений состоит из девяти тактов, задаваемых управляющими сигналами, формируемыми с помощью распределителя импульсов. Операции вычитания, сдвига и сложения кодов выполняются последовательно причем используется одна схема суммирования, что связано с усложнением .схемы управления и коммутации, а также с необхо - . -. iS

димостью запоминания промежутдчных результатов П2.

Недостатками этого устройства являются повышенная сложность структуры и относительно низкое быстродействие, которые являются следствием последовательной организации процесса вычислений. Вр0«4я вычисле- ния определяется выражением

10

и;

г,/эг,

.в

где Т - время выполнения одной

onepai H cyivtteipoBaHHH чи15сел; , - время записи одного числа

в сумматор или регистр Тцц - время инвертирования кода; J - время сдвига числа на

20

САЛ5 один разряд. Цель изобретения - упрощение и повышение быстродействия устройства.

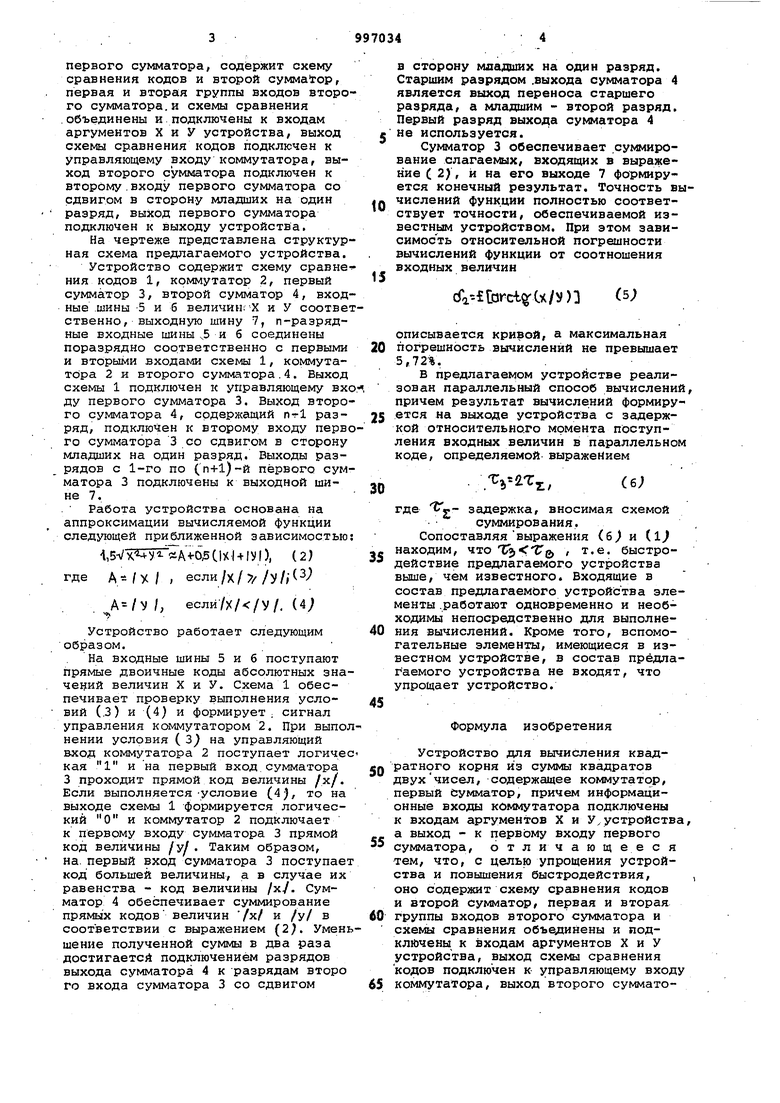

Поставленная цель достигается . тем, что устройство для вычисления

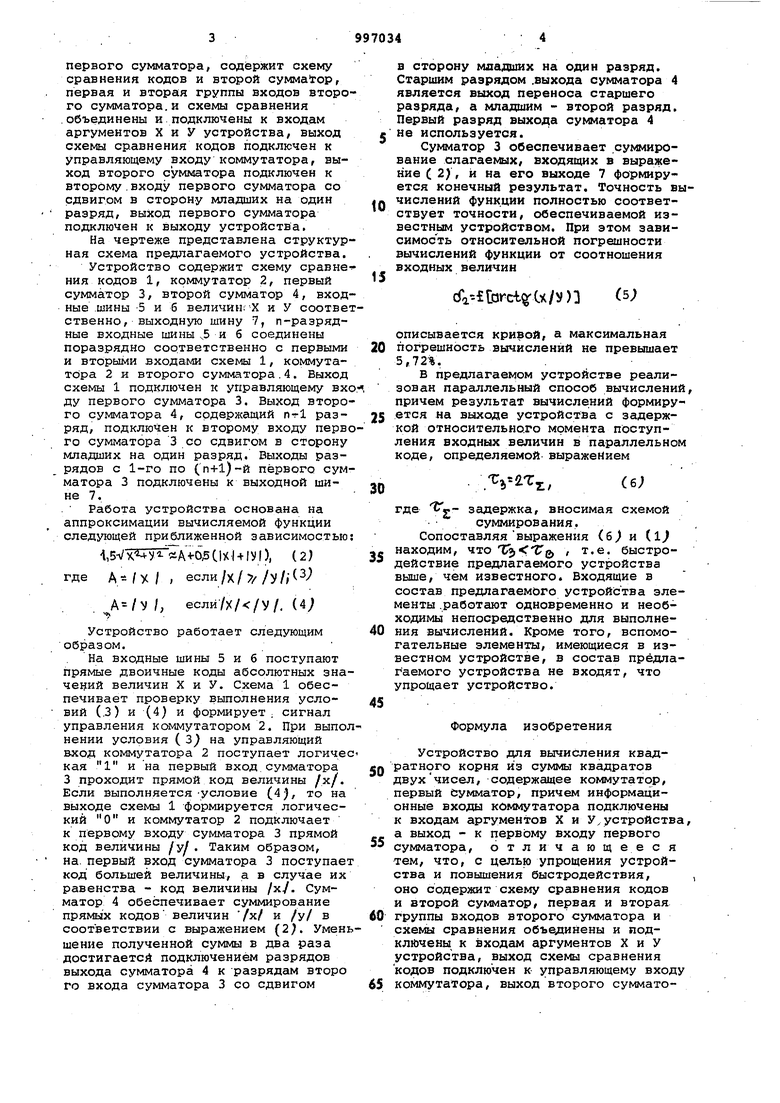

25 квадратного корня из суммы квадра-тов двух чисел, содержащее коммутатор, первый сумматор, причем информационные входы коммутатора подключены к входам аргументов X и У уст30ройства, а выход - к первому входу первого сумматора, содержит схему сравнения кодов и второй сумматор, первая и вторая группы входов второ го сумматора.и схемы сравнения .объединены и подключены к входам аргументов X и У устройства, выход схемы сравнения кодов подключен к управляющему входу коммутатора, выход второго сумматора подключен к второму.входу первого сумматора со сдвигом в сторону младших на один разряд, выход первого сумматора подключен к выходу устройства. На чертеже представлена структур ная схема предлагаемого устройства. Устройство содержит схему сравне ния кодов 1, коммутатор 2, первый cyNMaTop 3, второй сумматор 4, вход ные .шины -5 и б величин; Х и У соотве ственно, выходную шину 7, п-раэрядные входные шины 5 и 6 соединены поразрядно сортветственно с первыми и вторыми входа ли схемы 1, коммутатора 2 и второго сумматора.4. Выход схемы 1 подключен к управляющему вх ду первого сумматора 3. Выход второ го сумматора 4, содержащий п-г1 разряд, подключен к второму входу перв го сумматора 3 со сдвигом в сторону младших на один разряд. Выходы разрядов с 1-го по (п+1)-й первого сум матора 3 подключены к выходной шине 7. . Работа устройства основана на аппроксимации вычисляемой функции следующей приближенной зависимостью iBVx TyT A -d ClXl-HVl), (2) где Ati/X/ , если/х/ //У/,-(3 /, если/Х/ /У/, (4; Устройство работает следующим Образом. . На входные шины 5 и б поступают прямые двоичные коды абсолютных зна чений величин X и У. Схема 1 обеспечивает проверку выполнения уелоВИЙ (.3) и (4) и формирует, сигнал управления коммутатором 2. При выпо нении условия ( 3 на управляющий вход коммутатора 2 поступает логиче кая 1 и на первый вход сумматора 3 проходит прямой код величины /х/. Если выполняется-условие (4J, то на выходе схемы 1 формируется логический О и коммутатор 2 подключает к первому входу сумматора 3 прямой код величины /у/ . Таким образом, на. первый вход сумматора 3 поступае код большей величины, а в случае их равенства - код величины /х/. Сумматор 4 обеспечивает суммирование прямых кодов величин fx.f и /у/ в соответствии с выражением (2. Умен шение полученной суммы в два раза достигаетсй подключением разрядов выхода сумматора 4 к разрядам второ го входа сумматора 3 со сдвигом в сторону младших на один разряд. Старшим разрядом .выхода сумматора 4 является выход переноса старшего разряда, а младшим - второй разряд. Первый разряд выхода сумматора 4 не используется. Сумматор 3 обеспечивает .суммирование слагаемых, входящих в выражение ( 2J, и на его выходе 7 формируется конечный результат. Точность вычислений функции полностью соответствует точности, обеспечиваемой известным устройством. При этом зависимость относительной погрешности вычислений функции от соотношения входных величин cfa-.ftorct U/V) (5; описывается кривой, а максимальная погрешность вычислений не превышает 5,72%. в предлагаемом устройстве реализован параллельный способ вычислений, причем результат вычислений формируется на выходе устройства с задержкой относительного момента поступления входных величин в параллельном коде, определяемой выражением .. где vy- задержка, вносимая схемой суммирования. Сопоставляявыражения (б и (ij находим, что ) , т.е. быстродействие предлагаемого устройства выше, чем известного. Входящие в состав предлагаемого устройства элементы .работают одновременно и необходимы непосредственно для выполнения вычислений. Кроме того, вспомогательные элементы, имеющиеся в известном устройстве, в состав предлагаемого устройства не входят, что упрощает устройство. Формула изобретения Устройство для вычисления квадратного корня из суммы квадратов двухчисел, содержащее коммутатор, первый Сумматор, причем информационные входы коммутатора подключены к входам аргументов X и У,устройства, а выход - к первому входу первого сумматора, отличающееся тем, что, с целью упрощения устройства и повышения быстродействия, , оно содержит схему сравнения кодов и второй сумматор, первая и вторая группы входов второго сумматора и cxeivttj сравнения объединены и иодклйчены к входам аргументов X и У устройства, выход схемы сравнения кодов подключен к управляющему входу коммутатора, выход второго сумматоpa подключен к второмувходу первого сумматора со сдвигом в сторону младших наодин разряд, выход первого сум-, матора подключен к выходу устройства

Источники информации, принятые во внимание при экспертизе

1.Патент ОНА 3829671, кл. 235-158, опублик. 1970.

2.Авторское свидетельство СССР 627477, кл. Q06|f 7/552, 1977 (прототип). , .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Устройство для вычисления квадратного корня | 1976 |

|

SU642706A1 |

| Устройство для извлечения квадратного корня | 1980 |

|

SU957209A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для извлечения квадратного корня | 1986 |

|

SU1381497A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Устройство для вычисления выражения @ | 1985 |

|

SU1260950A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

1C Д1

Авторы

Даты

1983-02-15—Публикация

1981-07-06—Подача