Изобретение относится к вычислительной технике и предназначено для формирования суммы квадратов трех величин и извлечения квадратного корня.

Цель изобретения - расширение функциональных возможностей за счет дополнительного вычисления корня квадратного из суммы квадратов трех величин.

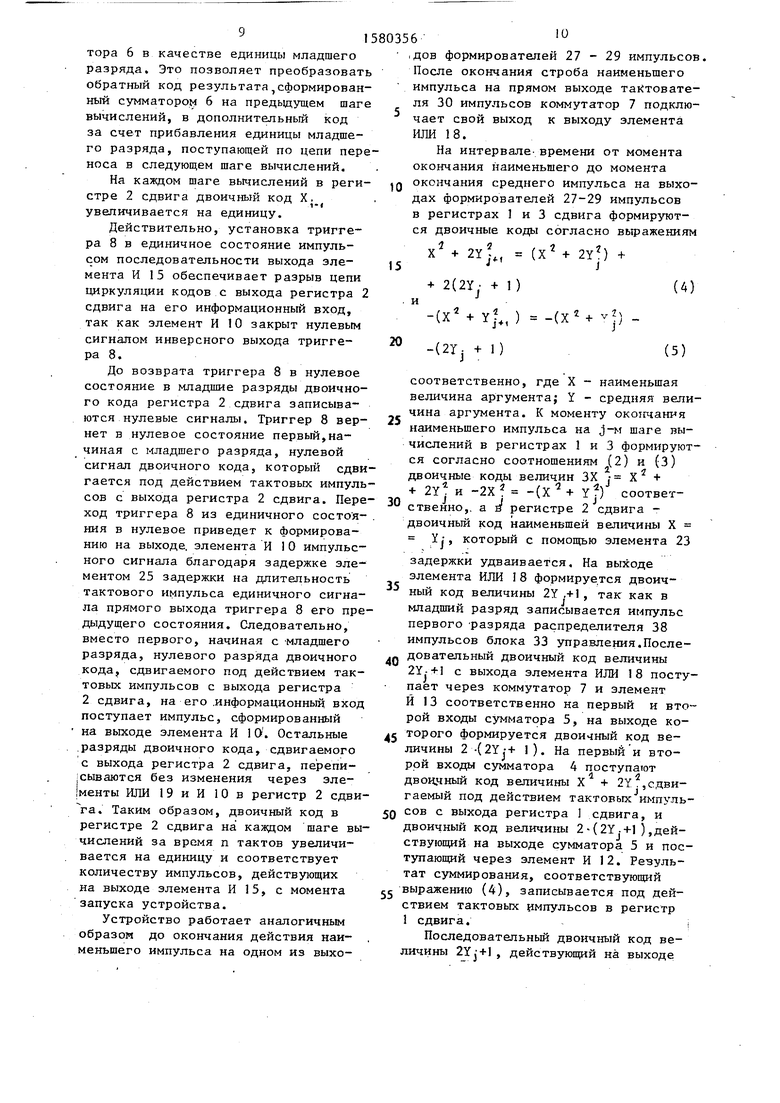

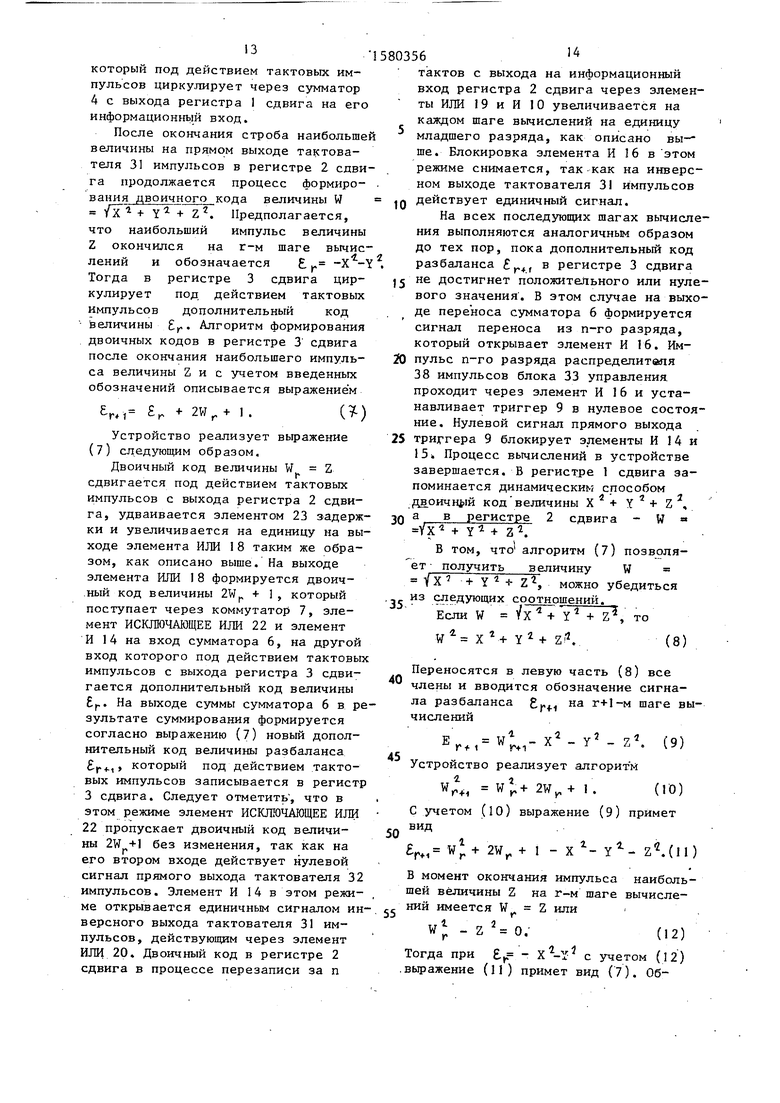

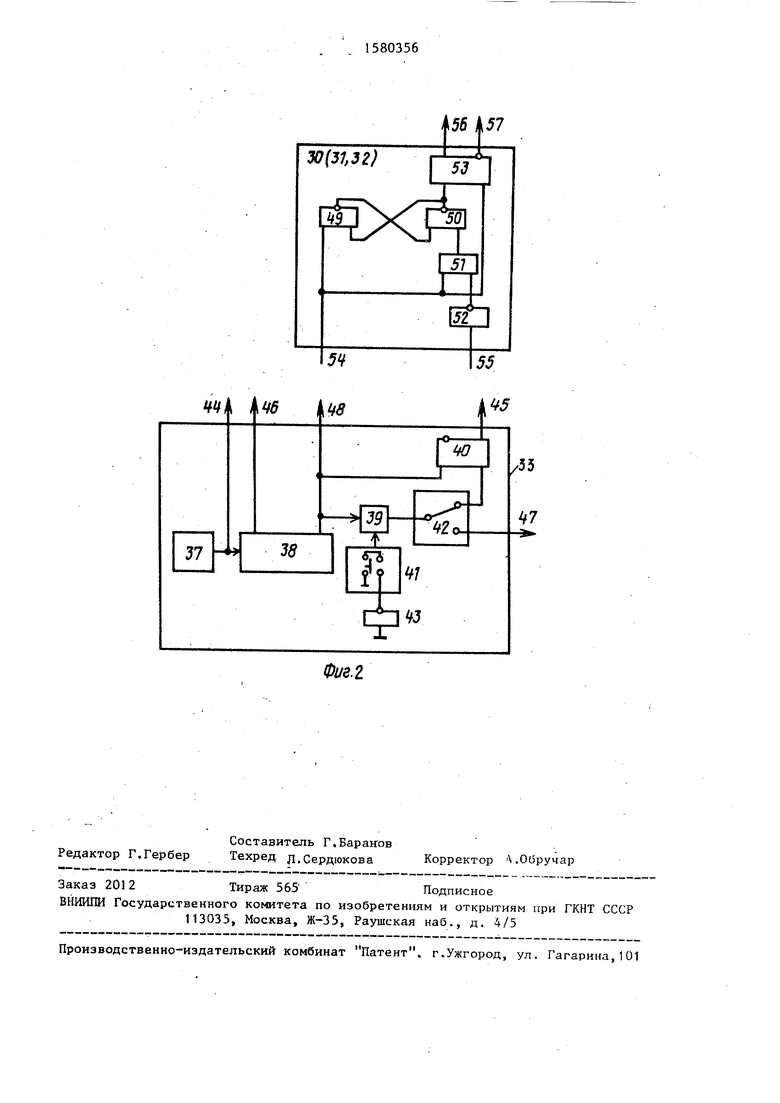

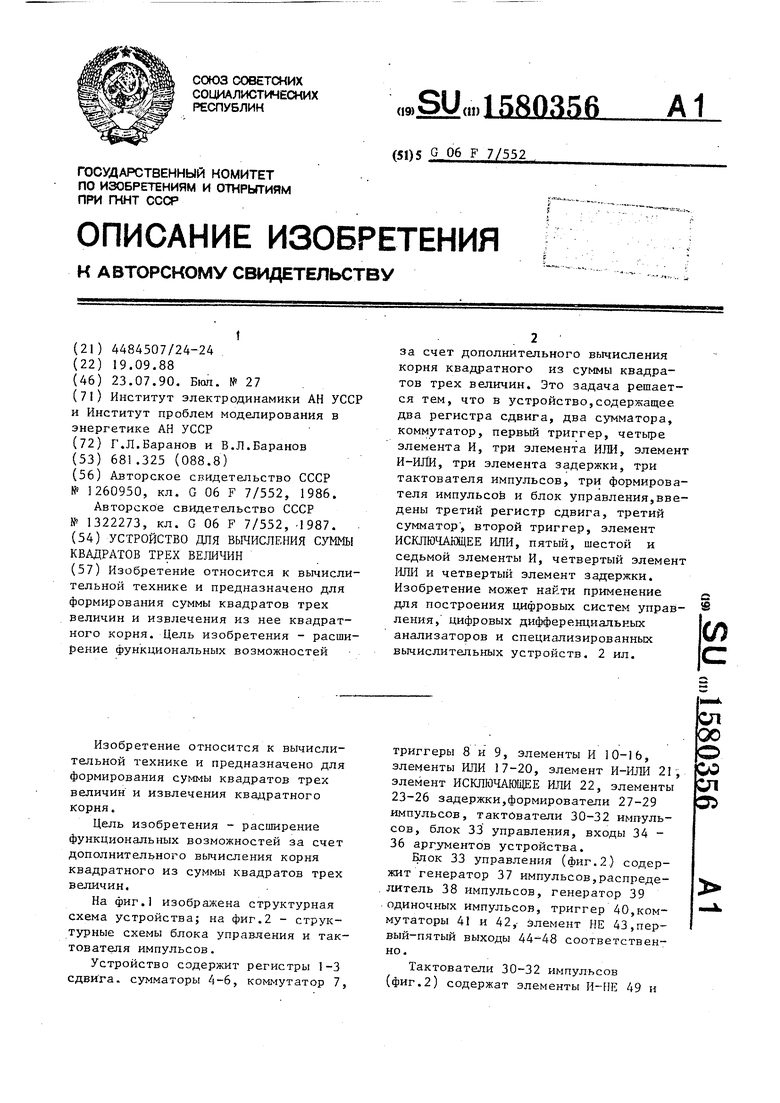

На фиг.1 изображена структурная схема устройства; на фиг.2 - структурные схемы блока управления и тактователя импульсов.

Устройство содержит регистры 1-3 сдвига, сумматоры 4-6, коммутатор 7,

триггеры 8 и 9, элементы И 10-16, элементы ИЛИ 17-20, элемент И-ИЛИ 21, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 22, элементы 23-26 задержки,формирователи 27-29 импульсов, тактователи 30-32 импульсов, блок 33 управления, входы 34 - 36 аргументов устройства.

Блок 33 управления (фиг. 2.) содержит генератор 37 импульсов,распределитель 38 импульсов, генератор 39 одиночных импульсов, триггер 40,коммутаторы 41 и 42,- элемент НЕ 43,пер- вый-пятый выходы 44-48 соответственно.

Тактователи 30-32 импульсов (фиг.2) содержат элементы И-НЕ 49 и

С71

00

о.

СлЭ

СЛ

&

50, элемент ИЛИ 51, элемент НЕ 52, триггер 53, тактовый вход 54, управляющий вход 55, прямой 56 и инверсный 57 выходы.

Устройство работает следующим образом.

В исходном состоянии коммутатором 42 блока 33 управления подключают выход генератора 39 одиночных импульсов к информационному входу триггера 40. Генератор 37 импульсов блока 33 управления формирует последовательность тактовых импульсов, из которых п-раз- рядный распределитель 38 импульсов формирует п последовательностей импульсов длительностью 1/f,периодом Т n/f и сдвинутых друг относительно друга на время t 1/f, где f - частота тактовых импульсов генератора 37 импульсов, п - количество разрядов регистров 1 - 3 сдвига. Коммутатором 41 подают сигнал логической единицы с выхода элемента НЕ 43 на управляющий вход генератора 39 одиночных импульсов, на выходе которого выделяется одиночный импульс из последовательности п-го разряда распределителя 38 импульсов. Выходной импульс генератора 39 одиночных импульсов через .коммутатор 42 посту- пает на информационный вход триггера 40, устанавливая его в единичное состояние. Сигнал логической единицы прямого выхода триггера 40 поступает на управляющие входы регистров 1 и 2 tсдвига, которые под действием тактовых импульсов, поступающих с выхода 44 блока 33 управления, устанавливаются в нулевое состояние, так как на их установочных входах действует сигнал логического нуля.

В регистр 3 сдвига под действием тактовых импульсов генератора 37 импульсов и единичного сигнала прямого выхода триггера 40 блока 33 управления записывается единица младшего разряда, так как на установочном вхо де регистра 3 сдвига действует последовательность импульсов первого разряда распределителя 38 импульсов бло ка 33 управления.

Триггер 8 устанавливается в нулевое состояние нулевым сигналом,сдвигаемым с выхода регистра 2 сдвига на инверсный вход сброса триггера 8. Триггер 9 находится в нулевом состоянии, в которое он устанавливается в предыдущем цикле работы устройст

5

0

5

0

0

5

0

5

5

ва. В исходном состоянии при нулевом сигнале на управляющем входе коммутатор 7 подключает свой выход к выходу элемента ИЛИ 18. На выходах формирователей 27 - 29 импульсов э исходном режиме действуют нулевые сигналы.

Элемент И 12 блокируется нулевым сигналом прямого выхода тактователя 31 импульсов. Элементы И 14 и 15 в исходном режиме блокируются нулевым сигналом прямого выхода триггера 9. Блокировку элемента И 13 осуществляет нулевой сигнал прямого выхода тактователя 32 импульсов.

Режим вычислений устанавливается коммутатором 42 блока 33 управления путем подключения выхода генератора 39 одиночных импульсов к управляющим входам формирователей 27-29 импульсов и к информационному входу триггера 9. Вычисления в устройстве начинаются после запуска с помощью коммутатора 41 генератора 39 одиночных импульсов, выходной импульс которого запускает формирователи 27 29импульсов и устанавливает триггер 9 в единичное состояние.

На выходах формирователей 27 - 29 импульсов после запуска формируются импульсы, длительность которых пропорциональна сигналам (аналоговым или цифровым), поступающим по входам 34 - 36 аргумента устройства.

Если длительность выходных импульсов формирователей 27-29 импульсов различна, то наибольший по длительности импульс выделяется на выходе элемента ИЛИ 17, импульс наименьшей длительности - на выходе элемента И 11, а средний по длительности импульс выделяется элементом И-ИЛИ 21.

Под действием наименьшего импульса на выходе элемента И 11 тактова- тель 30 импульсов формирует из последовательности импульсов п-го разряда распределителя 38 импульсов блока 33 управления, задержанных элементом 26 задержки на длительность тактового импульса, строб пачки импульсов, количество которых пропорционально -наименьшей величине, действующей на одном из входов 34 - 36 аргумента устройства. Сигнал строба на прямом выходе тактователя

30импульсов переключает коммутатор 7 в состояние, в котором его выход

соединяется с выходом элемента 24 задержки на такт.

Под действием наибольшего импульс выхода элемента ИЛИ I7 тактователь 3 импульсов формирует строб пачки импульсов, количество которых пропорционально наибольшей величине. Сигна строба прямого выхода тактователя 31 импульсов открывает элемент И 12, который подключает вход сумматора 4 к выходу сумматора 5.

Элемент И-ИЛИ 21 выделяет из выходных сигналов формирователей 27 - 29 импульс, длительность которого больше наименьшего, но меньше наибольшего импульса. До тех пор,пока на выходах 27 - 29 формирователей импульсов действуют одновременно не менее двух импульсов, на выходе элемента И-ИЛИ формируется единичный сигнал. Тактователь 32 импульсов,управляемый выходным сигналом элемента И-ИЛИ 21, формирует строб пачки импульсов, количество которых пропорционально средней величине, действующей на одном из входов 34-36 аргумента устройства.

Обозначаются величины, действующие на входах 34 - 36 аргумента соответственно через X, Y и Z. Допускается, что 0 X Y Z. В этом случае алгоритм формирования суммы квадратов трех величин описывается соотношением

X2 + Y + Z 3 Ј (21+1 ) + г°

+ 2 Г (2i + l) + (21+1), (1) i.x У

где 1 0, 1,2, 3... - натуральный ряд чисел.

Устройство реализует этот алгоритм следующим образом.

После запуска устройства единичный сигнал прямого выхода триггера 9 открывает элемент И 15, через который начинает поступать последовательность импульсов n-го разряда распределителя 38 импульсов блока 33 управления, задержанная элементом 26 задержки на длительность тактового импульса генератора 37 импульсов Первый импульс последовательности, действующий на выходе элемента И 15, устанавливает в единичное состояние триггер 8, на инверсном выходе которого формируется нулевой сигнал,бло- кирующий элемент И 10.

Единичный сигнал прямого выхода триггера 8, спустя время задержки элемента 25J задержки на длительность тактового импульса генератора 37 импульсов, поступает через элемент ИЛИ 19 на вход элемента И 10. Иод действием

тактовых импульсов генератора 37 импульсов блока 33 управления с выхода регистра 2 сдвига в первом такте сдвигается1 младший разряд начального нулевого кода, сигнал которого поступает на инверсный вход сброса триггера 8 и устанавливает его в нулевое состояние. На инверсном выходе триггера 8 формируется единичный сигнал, который снимает блокировку элемента

И 10. Благодаря задержке элементом 25 задержки на .длительность тактового импульса сигнала прямого выхода триггера 8 на выходе элемента И 10 формируется импульсный сигнал,который -в первом такте под-действием тактовых импульсов записывается в регистр 2 сдвига в качестве младшего разряда двоичного кода.

В течение первого такта импульс

первого разряда распределителя 38 импульсов блока 33 управления поступает через элемент ИЛИ 18 и элемент И 13, открытый сигналом строба прямого выхода тактователя 32 импульсов,

J5

на вход сумматора 5, с выхода которого этот импульс через элемент И 12- и сумматор 4 под действием тактовых импульсов записывается в первый разряд- регистра 1 сдвига.,

Q В следующем такте выходной импульс элемента ИЛИ 18 действует на выходе элемента 24 задержки на такт и через коммутатор 7, сумматор 5, элемент И 12 и сумматор 4 записывается под 5 действием тактовых импульсов во в горой разряд регистра 1 ДР: -а. Гя :им образом, после первгг па вычислений в чечение п тактов в регистрах 1 и 2 сдвига сформировались соответ0 ственно двоичные коды квадратичной .функции ЗХ, 3 и аргумента X , 1. Выходной импульс элемента ИЛИ I8 на первом шаге вычислений поступает также через элемент 24 задержки и

5 коммутатор 7 на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22, на втором входе которого действует единичный сигнал прямого выхода тактователя 32 импульсов. Поэтому в течение п тактов на

to

15

первом шаге вычислений на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22 сформируется обратный код 11...И01, который через элемент И 14 поступает на вход сумматора 6. Элемент И 14 открыт единичным сигналом прямого выхода такто- вателя 32 импульсов, действующим через элемент ИЛИ 20. С выхода регистра 3 сдвига под действием тактовых импульсов генератора 37 импульсов на первом шаге вычислений сдвигается, начиная с младшего разряда, начальный двоичный код 00...0001. В результате суммирования последовательных i

кодов, поступающих на входы сумматора 6 , на его выходе суммы формируется дополнительный код двойки 11 ... 1110, который под действием тактовых импульсов записывается в регистр 3 сдви-20 га. Таким образом, после первого шага вычислений в регистре 3 сдвига сформировался дополнительный код отрицательной величины квадратичной функции - 2 X - 2.

На втором и последующих шагах вычислений до окончания действия наименьшего импульса на одном из выходов формирователей 27-29 импульсов устройство в регистрах 1 и 3 сдвига формирует двоичные коды квадратичных функций

ЗХ; ЗХ, + 3(2Х ., t

.15803568

делителя 38 импульсов блока 33 управления поступает на первый вход элемента ИЛИ 18 одновременно с поступ- , лением на его второй вход с выхода элемента 23 задержки двоичного кода

величины 2Х . На выходе элемента

25

30

и

+ О

-2Х -2XJ2., -2(2ХЬ1 -И)

X

(2) (3)

X - и

|, - зна- i-l-х шагах

соответственно, где чения аргумента на i- и вычислений соответственно.

Например, на i-м шаге вычислений под действием тактовых импульсов,формируемых генератором 37 импульсов блока 33 управления, на первый вход сумматора 4 сдвигается последовательный двоичный код величины ЗХ .1 , сформированный на предыдущем шаге вычислений в регистре 1 сдвига, а с выхода регистра 2 сдвигается последовательный двоичный код аргумента X $, , который задерживается элементом 23 задержки на такт. Так как двоичный код сдвигается из регистра 2 сдвига, начиная с младших разрядов, то на выходе элемента 23 задержки формируется последовательный двоичный код величины 2Х ,, , в младшем разряде которого всегда содержится нулевой код. Импульс первого разряда распре35

40

45

50

55

ИЛИ 18 формируется последовательный код величины 2Х t +1, который поступает через элемент И 13 на вход сумматора 5. На выходе элемента 24 задержки на такт формируется двоичный код величины 2(2Х- 1 +1), который через коммутатор 7 поступает, начиная с младших разрядов, на сумматор 5. На выходе сумматора 5 формируется последовательный двоичный код величины 3(2Х, +1), который через элемент И 12 поступает, начиная с младших разрядов, на вход сумматора 4. На выходе сумматора 4 согласно соотношению (2) формируется последовательный двоичный код значения ЗХ квадратичной функции на i-м шаге вычисления, который под действием тактовых импульсов записывается в регистр 1 сдвига.

Двоичный код величины 2(2Xt .1 + l), действующий на выходе коммутатора 7 во время 1-го шага вычислений,преобразуется в обратный код элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 22, на одном из входов которого действует единичный сигнал прямого выхода тактователя 32 импульсов. Обратный код величины 2(2Х;, +1) поступает, начиная с младшего разряда, через элемент И 14 на вход сумматора 6, на другие входы которого подаются последовательный двоичный код отрицательной величины -2Х;, , сдвигаемый под действием тактовых импульсов с выхода регистра 3 сдвига, и единица младшего разряда, действующая по цепи переноса сумматора 6 в результате образования переноса из n-го разряда в предыдущем шаге вычислений. На выходе суммы сумматора 6 формируется согласно выражению (3) последовательный -обратный код отрицательной величины -2Х ., который под действием тактовых импульсов сдвигается в регистр 3 сдвига. Так как в n-х разрядах1 двоичных кодов отрицательных величин,суммируемых сумматором 6, содержатся единицы, то на выходе переноса сумматора 6 формируется сигнал переноса, поступающий в следующем шаге вычислений по цепи переноса на вход сумма

0

величины 2Х . На выходе элемента

5

0

5

0

45

50

55

ИЛИ 18 формируется последовательный код величины 2Х t +1, который поступает через элемент И 13 на вход сумматора 5. На выходе элемента 24 задержки на такт формируется двоичный код величины 2(2Х- 1 +1), который через коммутатор 7 поступает, начиная с младших разрядов, на сумматор 5. На выходе сумматора 5 формируется последовательный двоичный код величины 3(2Х, +1), который через элемент И 12 поступает, начиная с младших разрядов, на вход сумматора 4. На выходе сумматора 4 согласно соотношению (2) формируется последовательный двоичный код значения ЗХ квадратичной функции на i-м шаге вычисления, который под действием тактовых импульсов записывается в регистр 1 сдвига.

Двоичный код величины 2(2Xt .1 + l), действующий на выходе коммутатора 7 во время 1-го шага вычислений,преобразуется в обратный код элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 22, на одном из входов которого действует единичный сигнал прямого выхода тактователя 32 импульсов. Обратный код величины 2(2Х;, +1) поступает, начиная с младшего разряда, через элемент И 14 на вход сумматора 6, на другие входы которого подаются последовательный двоичный код отрицательной величины -2Х;, , сдвигаемый под действием тактовых импульсов с выхода регистра 3 сдвига, и единица младшего разряда, действующая по цепи переноса сумматора 6 в результате образования переноса из n-го разряда в предыдущем шаге вычислений. На выходе суммы сумматора 6 формируется согласно выражению (3) последовательный -обратный код отрицательной величины -2Х ., который под действием тактовых импульсов сдвигается в регистр 3 сдвига. Так как в n-х разрядах1 двоичных кодов отрицательных величин,суммируемых сумматором 6, содержатся единицы, то на выходе переноса сумматора 6 формируется сигнал переноса, поступающий в следующем шаге вычислений по цепи переноса на вход сумматора 6 в качестве единицы младшего разряда. Это позволяет преобразовать обратный код результата,сформированный сумматором 6 на предыдущем шаге вычислений, в дополнительный код за счет прибавления единицы младшего разряда, поступающей по цепи переноса в следующем шаге вычислений.

На каждом шаге вычислений в регистре 2 сдвига двоичный код Х.( увеличивается на единицу.

Действительно, установка триггера 8 в единичное состояние импульсом последовательности выхода элемента И 15 обеспечивает разрыв цепи циркуляции кодов с выхода регистра 2 сдвига на его информационный вход, так как элемент И 10 закрыт нулевым сигналом инверсного выхода триггера 8.

До возврата триггера 8 в нулевое состояние в младшие разряды двоичного кода регистра 2 сдвига записываются нулевые сигналы. Триггер 8 вернет в нулевое состояние первый,начиная с младшего разряда, нулевой сигнал двоичного кода, который сдвигается под действием тактовых импульсов с выхода регистра 2 сдвига. Переход триггера 8 из единичного состояния в нулевое приведет к формированию на выходе, элемента И I 0 импульсного сигнала благодаря задержке элементом 25 задержки на длительность тактового импульса единичного сигнала прямого выхода триггера 8 его предыдущего состояния. Следовательно, вместо первого, начиная с младшего разряда, нулевого разряда двоичного кода, сдвигаемого под действием тактовых импульсов с выхода регистра 2 сдвига, на его информационный вход поступает импульс, сформированный на выходе элемента И 10. Остальные разряды двоичного кода, сдвигаемого с выхода регистра 2 сдвига, перепи- ьшаются без изменения через эле- менты ИЛИ 19 и И 10 в регистр 2 сдви- га. Таким образом, двоичный код в регистре 2 сдвига на каждом шаге вычислений за время п тактов увеличивается на единицу и соответствует количеству импульсов, действующих на выходе элемента И 15, с момента запуска устройства.

Устройство работает аналогичным образом до окончания действия наименьшего импульса на одном из выхо

(Дов формирователей 27 - 29 импульсов. После окончания строба наименьшего импульса на прямом выходе тактовате- ля 30 импульсов коммутатор 7 подключает свой выход к выходу элемента ИЛИ 18.

На интервале- времени от момента окончания наименьшего до момента окончания среднего импульса на выходах формирователей 27-29 импульсов в регистрах 1 и 3 сдвига формируются двоичные коды согласно выражениям

х +

2Y

2(2У,

Л

+ 1)

- (X

2Уг)

(4)

5

0

v})

0

(5)

0

-(X ч- ) -(Хг

-(2Tj + О

соответственно, где X величина аргумента; Y чина аргумента. К моменту окончания наименьшего импульса на j-м шаге вычислений в регистрах 1 и 3 формируются согласно соотношениям (2) и (3) двоичные коды величин ЗХ : X2 + + -2Х -(X

наименьшая средняя велил. J

Y)

соответ5

j i j ственно, а в регистре 2 сдвига двоичный код наименьшей величины X Y;, который с помощью элемента 23

задержки удваивается. На выходе элемента ИЛИ I8 формируется двоичный код величины 2Y .+ 1, так как в младший разряд записывается импульс первого разряда распределителя 38 импульсов блока 33 управления.ПослеQ довательный двоичный код величины

2Y-+1 с выхода элемента ИЛИ 18 поступает через коммутатор 7 и элемент И 13 соответственно на первый и второй входы сумматора 5, на выходе ко5 торого формируется двоичный код величины 2 -(2Y.-+ 1). На первый и второй входы сумматора 4 поступают двоичный код величины X + 2Y2,сдвигаемый под действием тактовых импульсов с выхода регистра 1 сдвига, и двоичный код величины 2-(2Y-+1)действующий на выходе сумматора 5 и поступающий через элемент И 12. Результат суммирования, соответствующий

е выражению (4), записывается под действием тактовых импульсов в регистр 1 сдвига.

Последовательный двоичный код величины 2Yj+l, действующий на выходе

элемента ИЛИ 18, поступает также че рез коммутатор 7 на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 22, который преобразует его в обратный код, так как на его другом входе действует единичный сигнал строба средней величины,формируемый тактователем 32 импульсов. Обратный код отрицательной величины -(2Y.- + 1 ) поступает через элемент И 14 на вход сумматора 6, на другие входы которого поступают обратный код отрицательной величины -(X + Y ; сдвигаемый под действием тактовых импульсов с выхода регистра 3 сдвига, и по цепи переноса: перенос из n-го разряда, сформированный на предыдущем шаге вычислений.

В результате суммирования на выходе суммы сумматора 6 формируется согласно выражению (5) обратный код отрицательной величины -(X + + Yj4i ), который под действием тактовых импульсов записывается в регистр 3 сдвига, а на выход переноса сумматора 6 формируется перенос из n-го разряда, поступающий по цепи переноса на вход сумматора 6.

В это время, как ранее было описано, двоичный код в регистре 2 сдвига при каждом шаге вычислений увеличивается на единицу младшего разряда.

На всех последующих шагах вычисления выполняются аналогично до момента окончания на К-м шаге средне- го импульса величины Y, К этому моменту времени в регистре 1 сдвига сформировался согласно выражению

(А) двоичный код величины X +

Х

+ Y + Z

k

Y - 2Yt.

в регистре 2 сдвига - двоичный код средней величины Y Z jl, а в регистре 3 сдвига - обратный код отрицательной величины -(X7 + Y ). После окончания строба среднего импульса величины Y на прямом выходе тактователя 32 импульсов формируется нулевой сигнал, который совместно с нулевым сигналом инверсного выхода тактователя 31 импульсов формирует на выходе элемента ИЛИ 20 нулевой сигнал, блокирующий элемент И 14. В следующем шаге вычислений перенос из n-го разряда, сформированный на предыдущем шаге вычислений, поступает но цепи переноса на вход сумматора 6, на другой вход которого под действием тактовых импульсов сдвигается с выхода регистра 3 сдви

га обратный код величины (Хг + Y2). В результате суммирования на выходе суммы сумматора 6 формируется дополнительный код величины -(X +Y ),который под действием тактовых импульсов запоминается динамическим способом путем циркуляции кода с выхода реги- - стра 3 сдвига на его информационный вход через сумматор 6.

После окончания строба средней величины Y нулевой сигнал прямого выхода тактователя 32 импульсов блокирует элемент И 13, а в регистре 1 5 сдвига формируется двоичный код величины.

Y +

Zl (Г

Y +

:

zt)

-K2Z.+ 1),,

(6)

где X, Y и Z - соответственно наименьшее, среднее и наибольшее значения аргумента. Действительно, на (k+1)-м шаге двоичный код величины Z,, сдвигаемый под действием тактовых импульсов из регистра 2 сдвига, удваивается с помощью элемента 23 за1- держки на такт. На выходе элемента ИЛИ 18 формируется двоичный код величины 2 Z + 1, который через коммутатор 7, сумматор 5 и элемент И 12 поступает на вход сумматора 4, на другой вход которого с выхода регистра 1 сдвига поступает двоичный код величины X + Y + Z 1. Результат суммирования, соответствующий выражению (6), записывается под действием тактовых импульсов в регистр 1 сдвига. Одновременно на (k+1)-м шаге

вычислений, как описано выше, двоичный код в регистре 2 сдвига уве- .личивается на единицу младшего разряда.

Вычисления на всех последующих

шагах выполняются аналогично до момента окончания наибольшего импульса величины Z. После окончания наибольшего импульса на выходе элемента ИЛИ 17 устанавливается нулевой

сигнал, который формирует на прямом выходе тактователя 31 импульсов нулевой сигнал, а на инверсном выхо- .де - единичный. Нулевой сигнал пря- - мого выхода тактователя 31 импульсов . блокирует элемент И 12. Процесс вычисления суммы квадратов трех величин завершается, а в регистре 1 сдвига запоминается динамическим способом ;

двоичный код величины X +

Y%

13

который под действием тактовых импульсов циркулирует через сумматор 4 с выхода регистра 1 сдвига на его информационный вход.

После окончания строба наибольшей величины на прямом выходе тактова- теля 31 импульсов в регистре 2 сдвига продолжается процесс формиро- вания двоичногд кода величины W YA а + Y г + Z2. Предполагается, что наибольший импульс величины Z окончился на r-м шаге вычисл

лений и обозначается Ј г -X -Y Тогда в регистре 3 сдвига циркулирует под действием тактовых импульсов дополнительный код величины Јг. Алгоритм формирования двоичных кодов в регистре 3 сдвига после окончания наибольшего импульса величины Z и с учетом введенных обозначений описывается выражением

с.гм- Ј,

2Wr +

1 .

W

Устройство реализует выражение (7) следующим образом.

Двоичный код величины W Z сдвигается под действием тактовых импульсов с выхода регистра 2 сдвига, удваивается элементом 23 задержки и увеличивается на единицу на выходе элемента ИЛИ 18 таким же образом, как описано выше. На выходе элемента ИЛИ I8 формируется двоичный код величины 2Wr + 1, который поступает через коммутатор 7, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 22 и элемент И 14 на вход сумматора 6, на другой вход которого под действием тактовых импульсов с выхода регистра 3 сдвигается дополнительный код величины Јг. На выходе суммы сумматора 6 в результате суммирования формируется согласно выражению (7) новый дополнительный код величины разбаланса Јр-м который под действием тактовых импульсов записывается в регистр 3 сдвига. Следует отметить , что в этом режиме элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 22 пропускает двоичный код величины 2W +1 без изменения, так как на его втором входе действует нулевой сигнал прямого выхода тактователя 32 импульсов. Элемент И 14 в этом режиме открывается единичным сигналом инверсного выхода тактователя 31 импульсов, действующим через элемент ИЛИ 20. Двоичный код в регистре 2 сдвига в процессе перезаписи за п

58035614

тактов с выхода на информационный вход регистра 2 сдвига через элементы ИЛИ 19 и И 10 увеличивается на каждом шаге вычислений на единицу младшего разряда, как описано выше. Блокировка элемента И 16 в этом режиме снимается, так как на инверсном выходе тактователя 31 импульсов .Q действует единичный сигнал.

На всех последующих шагах вычисления выполняются аналогичным образом до тех пор, пока дополнительный код разбаланса ЕГ41 в регистре 3 сдвига jr не достигнет положительного или нулевого значения. В этом случае на выходе переноса сумматора 6 формируется сигнал переноса из n-го разряда, который открывает элемент И 16. Им- 20 пульс n-го разряда распределителя 38 импульсов блока 33 управления проходит через элемент И 16 и устанавливает триггер 9 в нулевое состояние. Нулевой сигнал прямого выхода 25 триггера 9 блокирует элементы И 14 и 15. Процесс вычислений в устройстве завершается. В регистре 1 сдвига запоминается динамическим способом двричщлй код величины X + Y 2 + Z , 3Q а в регистре 2 сдвига - W YX + Y + Z

В том, что1 алгоритм (7) позволяет гюлучить еличину W Т(Х э + Y г + Z% можно убедиться ,из следующих соотношений.

Если W Ух + Y1 + Z, то

W X + Y2 + Z .(8)

Переносятся в левую часть (8) все члены и вводится обозначение сигнала разбаланса Ј«fi на r-H-м шаге вычислений

E -W -X -Y -Z. (9)

Устройство реализует алгоритм

р т i И и т I .(10J

W, Wj,+ 2Wr+ 1.

С учетом СЮ) выражение (9) примет

вид

Јr+1 wЈ + 2Wr + I - X г- Z4.(ll)

В момент окончания импульса наибольшей величины Z на r-м шаге вычислений имеется W. Z или

wЈ - z 2 о.(12)

Тогда при Ј., - X2-Y с учетом (12) выражение (11) примет вид (7). Об15

уление сигнала разбаланса беспечивает равенство (8),

,1580356

--г+ откуда

О

ИЛ ро пе ва ми во И эл до с с р р и к л м в н р с 25 ф .„ п -с в 5д в .м „ п

ормула изобретения

Устройство для вычисления суммы вадратов трех величин , содержащее ва регистра сдвига, два сумматора, коммутатор, первый триггер, четыре элемента И, три элемента ИЛИ, элемент -ИЛИ, три элемента задержки, три актователя импульсов,три формироватея импульсов и блок управления,первый выход которого соединен с входами синхронизации, второй выход - с управляющими входами первого и второго регистров сдвига, установочные входы которых подключены к входу логического нуля устройства, а информационные входы - к выходам первого сумматора и первого элемента И, уп- равлякицие входы первого, второго и третьего тактователей импульсов соединены с выходами соответственно второго элемента И, первого элемента ИЛИ и элемента И-ИЛИ, третий выход блока управления соединен с первым входом второго элемента ИЛИ,второй вход которого соединен с выходом первого элемента задержки, четвертый выход блока управления подключен к управляющим входам первого, второго и третьего формирователей импульсов, информационные входы которых являются входами соответственно первого, второго и третьего аргументов устройства, выход первого регистра сдвига соединен с первым входом первого сумматора; второй вход которого соединен с выходом третьего элемента И, выход второго элемента ИЛИ соединен непосредственно с первым информационным входом и через второй элемент задержки - с вторым информационным входом коммутатора, управляющий вход которого соединен с прямым выходом первого тактователя импульсов,выход второго регистра сдвига соединен с входом первого элемента задержки,с входом первого элемента ИЛИ и -инверсным входом установки первого триггера, инверсный выход которого соединен с первым входом первого элемента И, прямой выход первого триггера соединен через третий элемент задержки с вторым входом третьего элемента

16

5

0

ИЛИ, выход которого подключен к второму входу первого элемента И,выходы первого, второго и третьего формирователей импульсов соединены с первыми, вторыми и третьими входами первого элемента ИЛИ и второго элемента И, первый и второй входы третьего элемента И соединены с прямым выходом второго тактователя импульсов и с выходом второго сумматора соответственно, первый и второй входы которого соединены с выходами коммутатора и четвертого элемента И, первый и второй входы которого подключены к прямому выходу третьего тактователя импульсов и выходу второго элемента ИЛИ соответственно, выход первого формирователя импульсов соединен с первыми входами первой и второй групп входов элемента И-ИЛИ,вторые входы первой и второй групп входов которого подключены к выходам соответственно второго и третьего 5 формирователей импульсов, первый и второй входы третьей группы входов элемента И-ИЛИ соединены с выходами соответственно второго и третьего формирователей импульсов, отличающееся тем, что, с целью расширения функциональных возможностей за счет дополнительного вычисления корня квадратного из суммы квадратов трех величин, в него введены третий регистр сдвига, третий сумматор, второй триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, пятый, шестой, и седьмой элементы И, четвертый элемент ИЛИ и четвертый элемент задержки, .„ причем выход коммутатора соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход и выход которого соединены с прямым выходом третьего тактователя импульсов и с первым -с входом пятого элемента И соответственно, инверсный выход второго тактователя импульсов и прямой выход третьего тактователя импульсов соединены соответственно с первым и 5д вторым входами четвертого элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И, инфор- .мационный вход первого триггера соединен с выходом шестого элемента И, „ первый и второй входы которого подключены к прямому выходу второго триггера и к выходу четвертого элемента задержки соответственно,выход третьего регистра сдвига соединен с

0

5

первым входом третьего сумматора, второй вход которого подключен к выходу пятого элемента И, третий вход которого соединен с прямым выходом второго триггера, информационный вход и вход сброса которого подключены соответственно к четвертому выходу блока управления и к выходу седьмого элемента И, первый и второй выходы блока управления соединены соответственно с входом синхронизации и управляющим входом третьего регистра сдвига, установочный вход которого подключен к третьему выходу блока

0

5

управления, информационный вход третьего, регистра сдвига соединен с выходом суммы третьего сумматора, выход переноса которого подключен к первому входу седьмого элемента И, второй вход которого и вход четвертого элемента задержки соединены с пятым выходом блока управления, а третий вход .- с инверсным выходом второго тактователя импульсов,выход четвертого элемента задержки соединен с тактовыми входами первого,вто- рого и третьего тактователей импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1987 |

|

SU1501049A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Квадратор | 1983 |

|

SU1180885A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

| Устройство для контроля экспоненциальных процессов | 1984 |

|

SU1282087A1 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU955051A1 |

| Цифровой регулятор | 1980 |

|

SU938255A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

Изобретение относится к вычислительной технике и предназначено для формирования суммы квадратов трех величин и извлечения из нее квадратного корня. Цель изобретения - расширение функциональных возможностей за счет дополнительного вычисления корня квадратного из суммы квадратов трех величин. Эта задача решается тем, что в устройство, содержащее два регистра сдвига, два сумматора, коммутатор, первый триггер, четыре элемента И, три элемента 1или4, элемент И-ИЛИ, три элемента задержки, три тактователя импульсов, три формирователя импульсов и блок управления, введены третий регистр сдвига, третий сумматор, вторй триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, пятый , шестой и седьмой элементы И, четвертый элемент ИЛИ и четвыртый элемент задержки. Изобретение может найти применение для построения цифровых систем управления, цифровых дифференциальных анализаторов и специализированных вычислительных устройств. 2 ил.

57

| Устройство для вычисления выражения @ | 1985 |

|

SU1260950A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1988-09-19—Подача