(54) УСТРОЙСТВО для ИЗВЛЕЧЕНИЯ КВАДРАТНОГО

КОРНЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительное устройство | 1978 |

|

SU824206A1 |

| Функциональный преобразователь | 1983 |

|

SU1126968A1 |

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| Устройство для вычисления тригонометрических функций тангенса и котангенса | 1980 |

|

SU907545A1 |

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

| Устройство для вычисления функций синуса и косинуса | 1980 |

|

SU907546A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| Цифровой генератор функций | 1976 |

|

SU736079A1 |

| Цифровое устройство для воспроизве-дЕНия фуНКций | 1979 |

|

SU809126A1 |

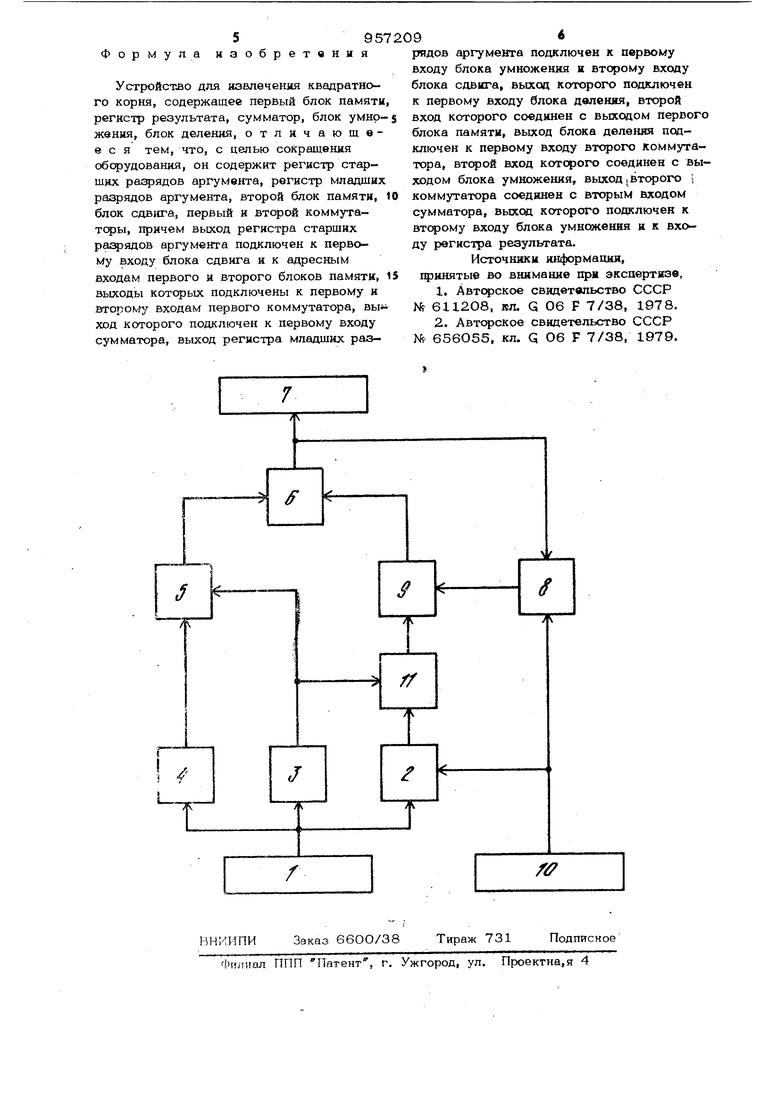

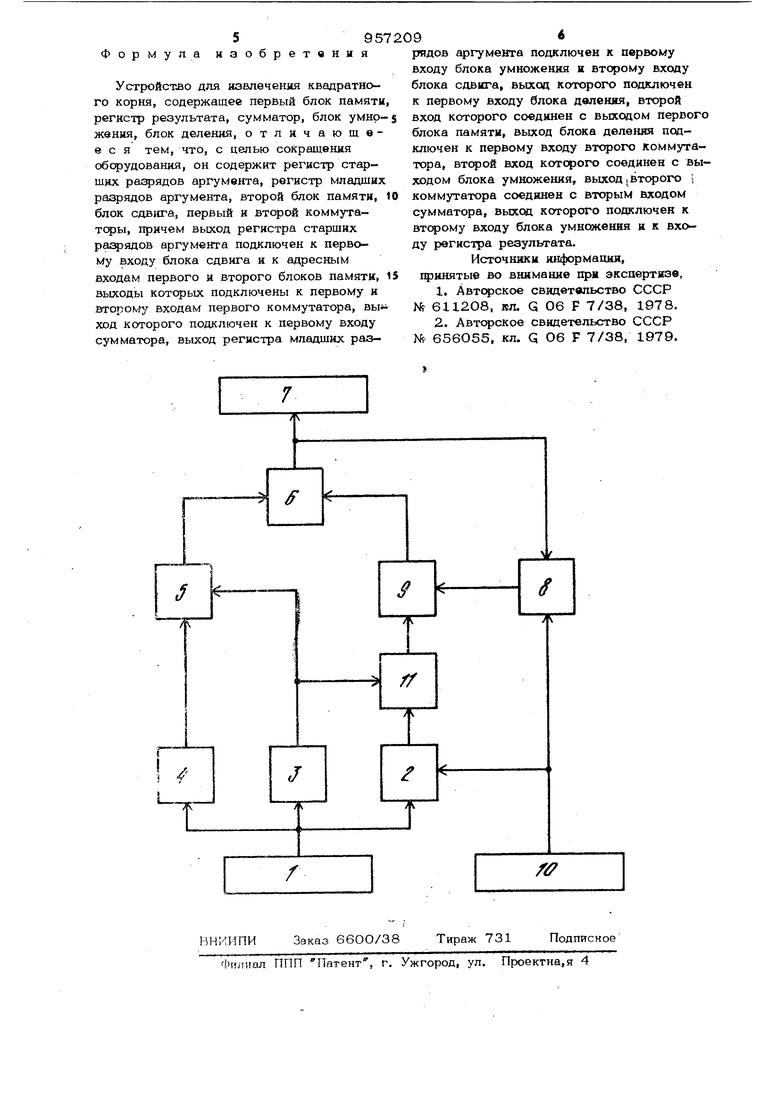

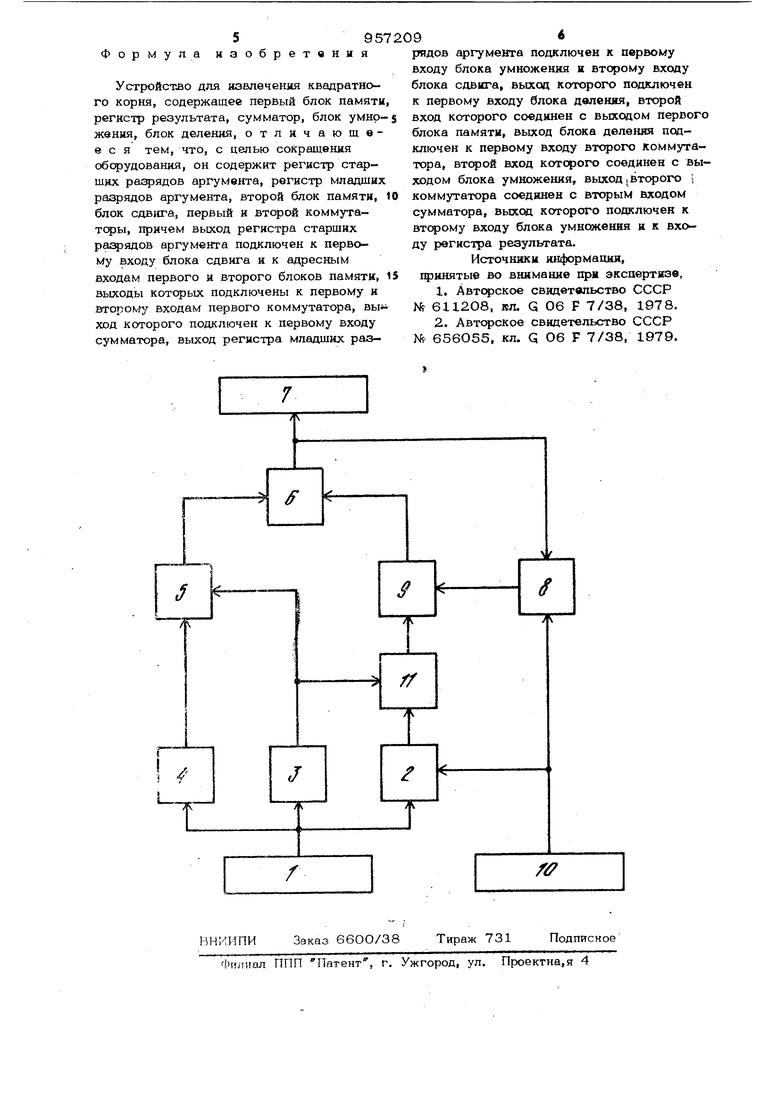

Изобретение относится к вычнслитепьной TexHjtKe и может быть испольаоваио в споцкализированных и универсальных быстродействующих ци45эовых вычислител ных машинах. Известно устройство для извлечения квадратного корня, содержащее входной и вьц:одной регистры, блок возведения в квадрат, схему сравнения и блок подбора цифр результата ЗOnHaiio это устройство не обеспечивает высокого быстродействия, так как вы числэния осуществляются методом после .пзательных итераций. Накболее близким к изобретению является устройство для извлечения квадратного корня, содержащее блок умножения, блок деления, первый блок памяти п регистр результата 21, Недостаток такого устройства заключается в его сложности, обусловленный необходимостью использования памяти большой емкости, что связано с приминенаем метода линейной интерполя- дии для вычисления значений фун-кцни между опорными точками, Так для указанного устройства, имеющего длину раврядной сетки входного и выходного слова, равную (n+l), включая знаковый разряд, требуется запоминающее устройство емкостью (Зр (n + j .2 Бит. Цель изобретения - сокращение оборудования. Поставленная цель достигается тем, что устройство для извлечения квадратного корня, содержащее первый блок памяти, регистр результата, сумматор, блок умножения, блок деления, содержит регистр старших разрядов аргумента, регистр младших разрядов аргумента, второй блок памяти, блок сдвига, первый и второй коммутаторы, причем вь1ход регистра старших разрядов аргумента подключен к первому входу блока сдвига и к адресным входам первого и второго блоков памяти, выходы которых подключены к первому к второму входам первого комму татора, выход которого подключен к первому входу сумматора, выход регистра младших разрядов аргумента подключен к первому входу блока умножения и. вто- рому входу блока сдвига, выход которого подключен к первому входу блока деления второй вход которого соединен с выходом первого блока памяти, выход блока деле- нця л.одключен к первому входу второго KOMMjoSTOpa, Второй вход которого соединен с выходом опока умножения, выход второго коммутатора соединен с вторым входом сумматора, выход которого подключен к второму входу блока умножения н X входу регистра результата. На чертеже показана структурная схе ма устройства. Устройство содержит регистр 1 старших разрядов аргумента, блок 2 сдвига, первый и второй блоки 3 к 4 памяти первый коммутатор 5, сумматор 6, регистр 7 результата, блок 8 укпюжекня, Второй коммутатор 9, регистр 10 младших разрядов аргумента, блок i 1 дачения, ВыТ-Ксление значения функции V : Ух производится на основе следующего приб jitDVieHKcro состНошенкя; fo Т/ Т-Ч / V (. Г-ля нормалкзойанных значений аргумента лежз1ц0л: в интервале 1/4 X -f , norpeuuiccTb R которого, как показывают рйсчеть, оценивается Выражением R : ,й X i, гфлчем X XQ -1- дХ где XQ чиспо, образованное К старшими разряда Я|Н tpr-jKieiJTa; йХ i .число, образован.;€- 1,- К ,у ладшчмь1 разрядами аргумента,; (1 - число разрядов для представления аргумента X. Устройство работает следуюш,им обра згАь Зкачениа аргумента X хранится на p::i--v.c-i:pax 1 И 10 и младших р3: ркдо& аргуй ента соответстве1шо. Б первом тшсте работы устройства с;-аШ5-;ие X с вььхода регистра 1 старши разрядсй аргумента поступает на адрес:,:,1й вход бпока 3 памяти и на первый зкоц блока 2 сдвига, на второй вход которого поступает значение X с выхода гл5гксггра .1C младших разрядов аргумента... С БЬхода первого б.лока 3 памяти с мается значенве YXj и .передается на вход делимого блока 11 деления. 1, .Блок 2 сдвига преобразует поступившие него а.начен гЯ в сумму 4Хо + + 2 дХ Путем смещения влево ходов Хд и дХна2н1 разряд соответствеяно, занося при этом значение О в дополнительный разряд, расположенный между кодами 4Хд и 2 л X. Блок сдвига 2 может быть реализован как группа элементов ИЛИ. Сформированная сумма 4Xj3 + 2 д X поступает на вход делителя блока 11 деления, на выходе которого образуется первый промежуточный результат-К/(о)Во втором такте код XQ с выхода регистра 1 старших разрядов аргумента передается на адресный вход второго блока 4 памяти, с выхода которого сни- мается значение 1/4 УХ , передаваемое через первый вход первого коммутатора 5 на вход сумматора .6, на другой вход которого поступает через первый вход второго коммутатора 9 значение Р. На Выходе сумматсра 6 получается Второй щэомежуточный результат Р 1/4УКо +Р,. В третьем такте происходит умножение значения Рл на код и X, и образуется третий промежуточный результат РЗ РХ В четвертом такте вьтолняется сложение Рд, поступившего на суммат э 6 через второй вход второго коммутатора 9, и значения УЛ , переданного на дру1 ой вход сумматора 6 через второй вход первого коммутатора 5. На, выходе сумматора 6 формируется значение результа та р , запоминаемое на регистре 7 результата. Расчеты показывают, что суммарная емкость Э. блоков памяти 3 и 4 определяется по формуле: Q 2(nм)2. Г(п..)/41. Функция (Х - Х представляет собой наименьшее целое число не меньшее X. Для , например, получаем )., (5м;-2Г- 1.. Сокрашение объема оборудования в этом случае составляет T | -----.

Авторы

Даты

1982-09-07—Публикация

1980-07-10—Подача