1

Изобретение отиосится к областя вычислительной техники и может быть примшшо, иапример, в арифметических устройствах блоедого типа, в вьгшслительиых средах или в специализированных устройствах, построенных на основе больших интегральных схем.

Известно устройство, содержащее сумматор, пе{юую и вторую группы элементов И, счетчик, генератор тактовьк импульсов 1 .

Известное устройство не позволяет полностью совмещать во времени поразрядный ввод аргумента с вычислошем и поразрядной выдачей результата.

Наиболее близким техническим решением к данному предложению является устройс11 о для вычисления квадратного корня, содержащее сметчик циклов, выходы которого соединены со входами депшфратора, сдвигатель, выходы которого соединены с первой группой входов первого сумматора, регистр результата, промежуточный регистр, второй, третий и четвергьш сумматоры 21.

Недостаток его состоит в низком быстродействии.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в устройство введены коммутатор, две группы злементов И-НЕ, блок анализа знаков, выходы

которого соединены с выходами устройства и управляющими входами сдвигателя и коммутатора, выходы которого подключены ко входам промежуточного регистра, выходы трех старших разрядов которого подключены к первой группе

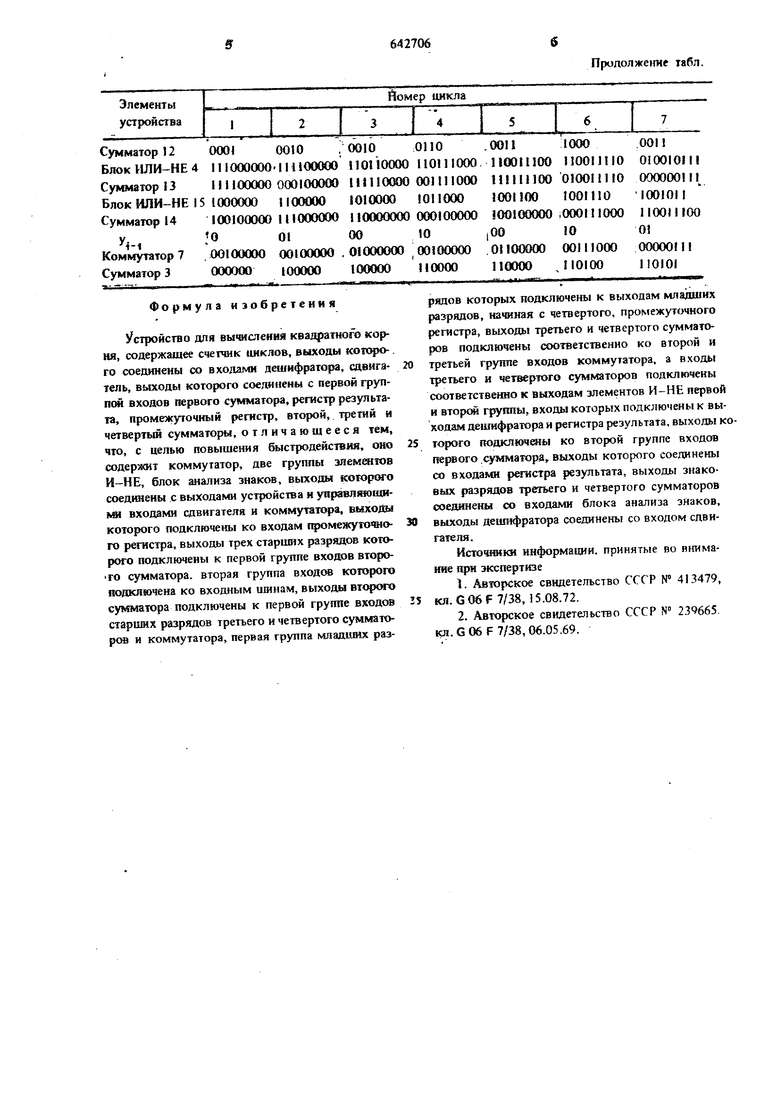

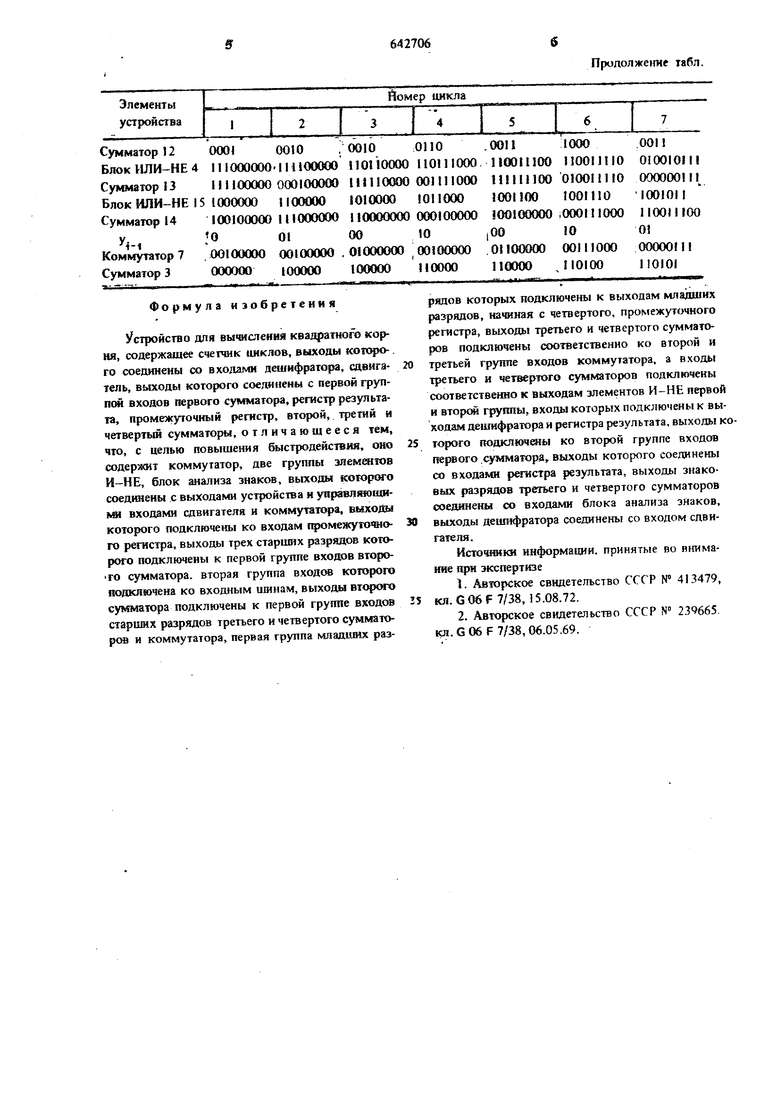

входов второго сумматора, вторая группа входов которого подключена ко входным шинам, выходы второго сумматора подключеиы к первой группе входов старишх разрядов третьего и четвертого сумматоров и коммутатора, первая группа младашх разряде которых подключены к выходам младцшх разрядов, начиная с четвертого, промежуточного регистра, выходы третьего и четвертого сумматоров подключены соответственно ко второй и третьей группе входов коммутаторй, а входы третьего и четвертого сумматоров подключеиы соответственно к выходам элементов И-НЕ первой и второй гру1шы, входы которых подключены к выходам дешифратора и регистра результата, выходы которого подключены ко второй группе входов первого сумматора, выходы которого соединены со входами регистра результата, выходы знаковых разрядов третьего и четвертого сумматоров соединены со входами блока анализа знаков, выходы дешис атора соединены со входом сдвигателя. Сущность предполагаемого изобретения поясняется прилагаемым чертежом, на котором нзображена структурная схема устройства для вычисления квадратного корня. Устройство содержит регистр результата 1 и промежуточный регистр 2, выполненные ю схеме регистра с внутренней задержкой, сумматор 3, группу элементов ИЛИ-НЕ 4, счетчнк циклов 5 и связанный с ним дешифратор 6, а также коммутатор 7, сдвигатель 8 н блок анализа знаков 9, реализующую систему логических уравнений: входные шины 10, П, сумматоры 12, 13, 14, группу элементов ИЛИ-НЕ 15, выходные шины 16, тактирующую 1Ш1ну 17. В исходном СОСТОЯНЮ1 (цепи установки исходного состояния на чертеже не показаны) в регистрах I и 2 записаны нули, а в счетчике циклов 5 зага1сана еданица. В каждом i-OM цикле вычисления на входные шины. 10 поступает 101фра аргумента, имеющая вес 2 (арг)гмент должен быть нормализовш), а на выходе деишфратора 6 единица находится в i-oM разряде слева. Группы элементов ИЛИ-НЕ 4 и 15 формируют на входе сумматоров 13 и 14 дополнительный ход суммы чисел, поступаюишх на их входы. Блок 9 анализирует знаковые разряШ | сумматоров 13 и 14 и вырабатьюает очередную цифру результата, которая выдается на выходные шины 16 н поступает на управляющие входы коммутатора 7 и сдвигателя 8. Сформированная 1шфра результата-имеет вес 2 ,т.е. задержка прявлетшя на выходе старшей цифры результата составляет одаи цикл. При этом числа на входе и выходе устройства представлены в избыточном двоичном коде, где шфры принимают значения из множества |0, 1,2) (поскольку неизбьгточная двоичная система счисления явяется частным случаем выше указанной,то на ход устройства могут поступать и числа в чеизыточиом коде). Если цифра результата равна даум, то коммуатор 7 подключает ко входам регистра 2 выходы умматора 14, а сдвигатель 8 осуществляет сдвиг лево на один разряд числа, поступающего на его ход. Если цифра результата равна единице, то коммутатор 7 подключает ко входам регистра 2 выходы сумматора 13, а сдвигатель 8 осуществляет передачу кода без сдвига. Если Ффра результата равна нулю, то коммутатор 7 подключает ко входным регистрам 2 выходы разрядов сумматора 12 и выхода младших разряде регистра 2, а сдвигатель 8 кода не выдает. После полного срабатывания всех узлов устройства, т.е. после завершения всех переходных процесссж в схеме, когда на входах jjerHCTpos 1 и 2 сформированы коды, предаазначенные для записи, следует сигнал в синхронизирующей шине 17, по которому происходит прием кода на регистры 1 и 2 и прибавление единицы в счетчик циклов. Применение в качестве регистров i и 2 регистров с внутренней задержкой позволяет исключить возможность появления гонок. В прилагаемой таблице, где через Xj у j обозначены соответственно цифры аргумента н результата, имеющие вес 2 , приведен пример вычисления квадратного корня из числа X 0,100212 0,101100, при зтом получен результат V 0,102021 0,110101. Как видао из примера, задержка появления соответствующих разрядов результата на выходе устройства составляет Тр. Следовательно, выигрыш в быстродействии по сравнению с известным устройством равен (in/2-l)- „ Одинаковая форма представления чисел на входе и выходе позволяет применение предлагаемого устройства в вычислительной среде. Например, задержка появления соответствующих разрядов результата на выходе последовательной цепочки из k предлагаемых устройств составляет Следовательно, результат будет получен на ()п раньше, чем при применении извест ных устройств.

Продолжение табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления интегра-лОВ | 1976 |

|

SU840901A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1141399A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

Формула изобретения

Устройство для вычисления кваяратногё корня, содержащее счегчик циклов, выходы . го соединены со входами дешифратора, сдвигатель, выходы которого соетшиеиы с первой группой входов первого сумматора, регистр результата, промежуточный регистр, второй, третий и четвертый сумматоры, отличающееся тем, что, с целью повышения быстродействия, око содержит коммутатор, две группы эяемшгов И-НЕ, блок анализа знаков, выхода) которого соединены с выходами устройства и унраиляюндамя входами сдвигателя и коммутатора, выхода которого подключены ко входам промежуто« ого регистра, выходы трех старших разрядов которого подключены к первой группе входов второго сумматора, вторая группа входов которого подключена ко входным шинам, выходы вторшх) сумшатора подключены к первой группе входов старших разрядов третьего и четвертого сумматоре и коммутатора, первая группа младших разрядов которых подключены к выходам младших разрядов, начиная с четвертого, промежуточного регистра, выходы третьего и четвертого сумматоров подключены соответственно ко второй и

третьей группе входов коммутатора, а входы третьего и четвертого сумматоров подключены соответственно к выходам элементов И-НЕ первой и вторш группы, которых подключены к выходам дешифратора и регистра результата, выходы которого подключены ко второй группе входов первого .сумматора,, выходы которого соединены со входакш регистра результата, выходы знаковых разрядов третьего и четвертого сумматоров соединены со входами блока аналнза знаков,

выходы дешифратора соединены со входом сдвнгателя.

Источники информации, принятые во пниманке при экспертизе

Авторы

Даты

1979-01-15—Публикация

1976-03-04—Подача