30

В

этот мочисло, соответствующее периоду вход- о держки переднего Лронта выходного ного сигнала, деленному на число сигнала . Разрядность счетчика 16 равна п. На два входа установки n-го разряда счетчика 16 постоянно подается сигнал логической 1.15

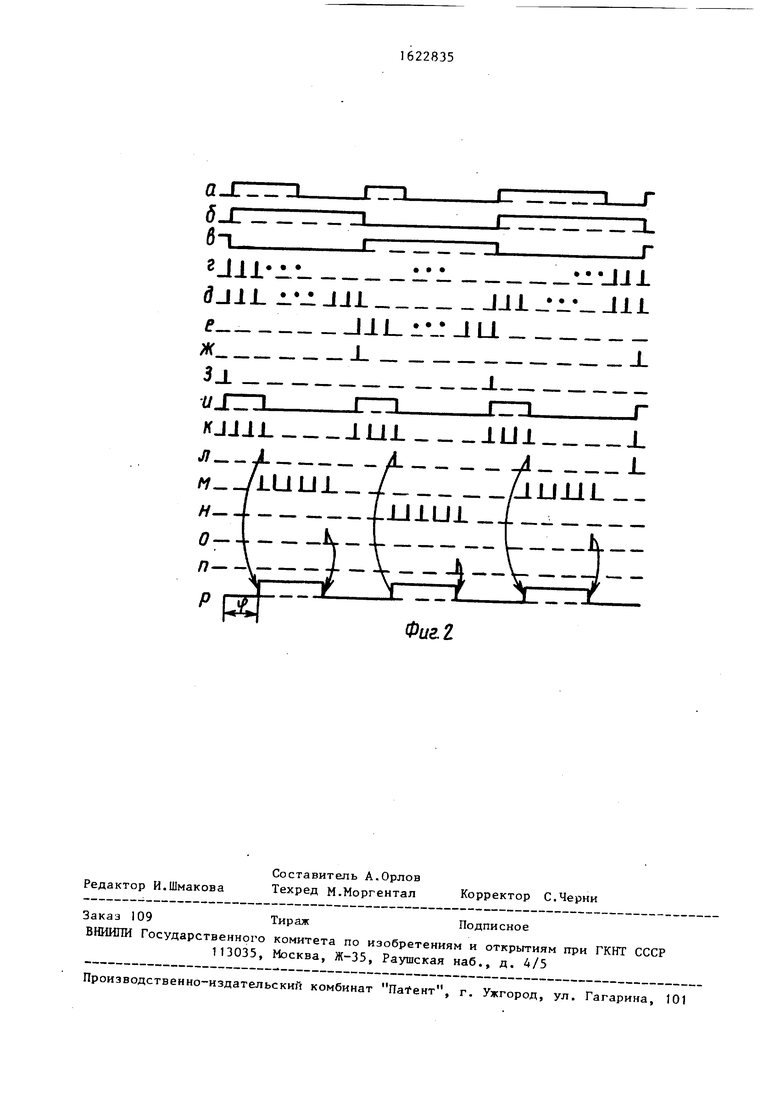

Запись чисел, поступающих с блоков 14 и 15 в счетчик 16, происходит импульсами, поступающими на входы разрешения записи с выходов Формирователей 3 и 7, на входы которых поступают сигналы с выходов делителя 2 (фиг.2 б) и инвертора 6 (фиг.2 в). Формирователь 3 формирует импульс записи по заднему фронту сигнала с делителя 2 (фиг.2ж),а формирователь 7 - по заднему фронту сигнала с инвертора 6 (Лиг.2з). В результате этого в счетчик 16 поочередно записывается двоичное число то с блока 14, то с блока 15 в зависимости от полупериода сигнала на выходе делителя 2, Так, если на выходе делителя 2 появляется передний фронт сигнала,то в счетчик 16 записывается число и с выходов счетчика 11, в счетчик 12 поступают импульсы частотой F в течение периода входного сигнала. Если на выходе делителя 2 появляется задний фронт сигнала, то в счетчик 16 записывается число с выходов счетчи- к-1 12, а в счетчик 11 поступают импульсы частотой F.

При записи числа в счетчик 16 в его старший рязряд записывается логическая 1. В результате этого 45 на выходе старшего разряда счетчика .16 появляется сигнат (фиг.2и), который поступает на вход элемента И 17, на другой вход которого подаются импульсы с генератора 10 50 (фиг.2в) частотой F. С выхода элемента И 17 импульсы поступают на вычитающий вход счетчика 16 (иг.2к) до тех пор, пока в старшем разряде счетчика 16 не появится сигнал О 55 (фиг.2 и). При этом импульс с выхода (n-l)-ro разряда счетчика 16 (Лиг.2л) переводит триггер 13 в единичное состояние и формирует передний фронт

,

ния 1 на выхо де триггера 13 в зависимости от си нала на выходе делителя 2 на выход

20 лиГто элемента И 4, либо элемента И появляются импульсы частотой F от генератора 10 (фиг.2 м, н), которы поступают на вычитающие входы втор разрядов счетчиков 12 и 11 соответ

25 ственно. В результате этого при п явлении на выходах счетчиков 11 и логических О на выходах переноса этих счетчиков появляется импульс (фиг.2о,п) через время t, равное полупериоду входного сигнала t2

N а ,

2 F 2

мент времени импульс переноса счет чика 11 (либо 12) переводит тригг 13 в нулевое состояние, и на его в ходе Формируется задний Фронт выхо ного сигнала (Фиг.2р).

Таким образом, на выходе устрой ва (фиг.2р) присутствует сигнал со 40 скважностью, равной двум, сдвинуты относительно входного сигнала на в личину

35

fr

Ч -2Т

где 1 0,1,2...,т- число на упра

ляющем входе устройства,определяющее сдв разрядов чисел записанных в счетчиках 11 и 12; ( - угол сдвига Лаз между вход

и выходным сигналами. Максимальный фазовый сдвиг „дк If при 1 0, а минимальный

ч

мин

2пГ ПРИ 1

ш.

а выход

,

0

В

этот мония 1 на выходе триггера 13 в зависимости от сигнала на выходе делителя 2 на выходе

0 лиГто элемента И 4, либо элемента И 9 появляются импульсы частотой F от генератора 10 (фиг.2 м, н), которые поступают на вычитающие входы вторых разрядов счетчиков 12 и 11 соответ5 ственно. В результате этого при появлении на выходах счетчиков 11 и 12 логических О на выходах переноса этих счетчиков появляется импульс (фиг.2о,п) через время t, равное полупериоду входного сигнала t2

N а ,

2 F 2

мент времени импульс переноса счетчика 11 (либо 12) переводит триггер 13 в нулевое состояние, и на его выходе Формируется задний Фронт выходного сигнала (Фиг.2р).

Таким образом, на выходе устройства (фиг.2р) присутствует сигнал со 0 скважностью, равной двум, сдвинутый относительно входного сигнала на величину

5

fr

Ч -2Т

е 1 0,1,2...,т- число на управ-.

ляющем входе устройства,определяющее сдвиг разрядов чисел, записанных в счетчиках 11 и 12; ( - угол сдвига Лаз между входным

и выходным сигналами. Максимальный фазовый сдвиг „дк If при 1 0, а минимальный

ч

мин

2пГ ПРИ 1

ш.

Точность поддержания заданного фазового сдвига определяется погрешностью О «ь квантования периода входного сигнала, которая при определе- входного сигнала составнии периода ляет

кв JlXF

Формула изобретения

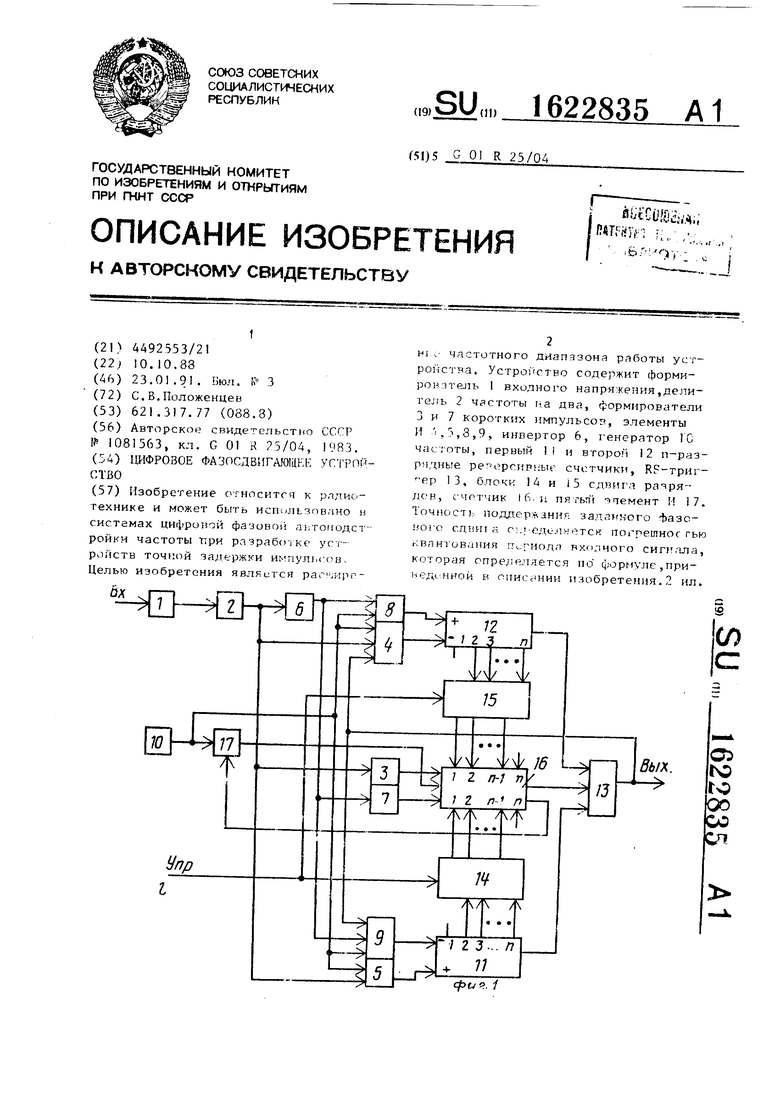

Цифровое фазосдвигающее устройство, содержащее формирователь входного напряжения, делитель частоты на два, инвертор, пять логических элементов И, два n-разрядных реверсивных счетчика, n-разрядный вычитающий счетчик, RS-триггер, генератор частоты, информационный вход, вход управления и выход, причем информационный вход устройства через Последовательно соединенные Формирователь входного напряжения и делитель частоты на два подключен к входу инвертора и к первым входам первого и второго логических элементов И, выход инвертора подключен к первым входам третьего и четвертого логических элементов И, выход генератора частоты подключен к вторым входам первого и четвертого логических элементов И, выход третьего логического элемента И подключен к суммирующему входу первого n-разрядного реверсивного счетчика, вычитающий вход второго разряда которого подключен к выходу первого логического элемента И, выход второго логического элемента И подключен к суммирующему входу второго n-разрядного реверсивного счетчика, вычитающий вход второго разряда которого подключен к выходу четвертого логического элемента И, выход пятого логического

5

0

5

0

5

0

45

элемента И подключен к вычитающему входу n-разрядного вычитающего счетчика, выход старшего разряда которого подключен к первому входу пятого логического элемента И, выход RS- триггера является выходом устройства, отличающееся тем, что, с целью расширения частотного диапазона устройства, в него введены два формирователя коротких импульсов по заднему фронту сигнала и два блока сдвига разрядов, вход пер- . вого формирователя коротких импульсов по заднему фронту сигнала подключен к выходу делителя частоты на два, вход второго - к выходу инвертора, а их выходы подключены соответственно к первому и второму входам разрешения записи n-разрядного вычитающего счетчика, второй вход пятого логического элемента И подключен к выходу генератора частоты, выходы рязря- дов со второго по n-ый п-разрядных реверсивных счетчиков подключены через блоки управления соответственно к первому и второму входам установки чисел n-разрядного вычитающего счетчика, причем n-е разряды входов этого счетчика подключены к сигналу логической единицы, управляющие входы блоков сдвигов разрядов объединены к входу управления устройства, S- вход RS-триггера соединен с выходом переноса (n-l)-ro разряда п-разряд- ного вычитающего счетчика, а два R- входа RS-триггера подключены к выходам переноса соответственно первого и второго n-раэрядных реверсивных счетчиков, выход RS-триггера соединен с третьими входами первого и четвертого логических элементов И,вторые входы третьего и первого логических элементов И, объединены,также объединены вторые входы второго и четвертого логических элементов И.

UJLL

JL

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Электростимулятор дыхания | 1990 |

|

SU1766421A1 |

| Стенд для испытания тормозов транспортных средств | 1987 |

|

SU1474506A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Цифровое фазосдвигающее устройство | 1983 |

|

SU1081563A1 |

| Импульсное фазосдвигающее устройство | 1986 |

|

SU1411959A1 |

| Устройство для пуска синхронной @ -фазной машины | 1990 |

|

SU1823119A1 |

| Устройство для сравнения фаз | 1984 |

|

SU1282254A1 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 1991 |

|

RU2040852C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

Изобретение относится к рлдио- технике и может быть использовано в системах цифровой фазовой аьтоподст ройки частоты при разработке устройств точной задержки импульсов Целью изобретения является parsnprHi , частотного диапазона работы устройства. Устройство содержит форми- ронттель 1 входного напряжения,делитель 2 частоты на два, формирователи 3 и 7 коротких импульсог, элементы И .5,3,9, инвертор 6, генератор 1C час;пты, первый 1I и втором 12 п-раэ- рчдные ре ергирныг счетчики, RF-триг- ер 13, блочк 14 и 15 сдтзигл разря- дс В, счогчик I (-. и пя гьп( - темент И 17. Точност) поддержания задаккого фазового а г1.; едел«втся погрешног гью квантования периода вхплчого сигнала, которая гпрелеллется по форгп лс ,при- нед1. иной в описании изобретения. 2 ил.

SJL

2Jli- L I..

6J1L JLM JJlIJ1 Ji i

eIJLJLi : lUL

/ff i - i

3±L

i/jcmimimiг

KJJJJLULluii.

J-J.A.J,L

M-JLL1LAL-J./JLLIJUIJ

//--/1U1U1 1

01 -4-I4-rjEEfiiSi±±Eii:

j

| Цифровое фазосдвигающее устройство | 1983 |

|

SU1081563A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-01-23—Публикация

1988-10-10—Подача