(54) МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифмов чисел | 1980 |

|

SU932491A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Устройство для умножения в избыточной системе счисления | 1984 |

|

SU1229755A1 |

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| Устройство для вычисления давления в узле трубопроводной системы | 1983 |

|

SU1170460A1 |

| Матричный умножитель по модулю чисел Ферма | 1990 |

|

SU1783513A1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1104511A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

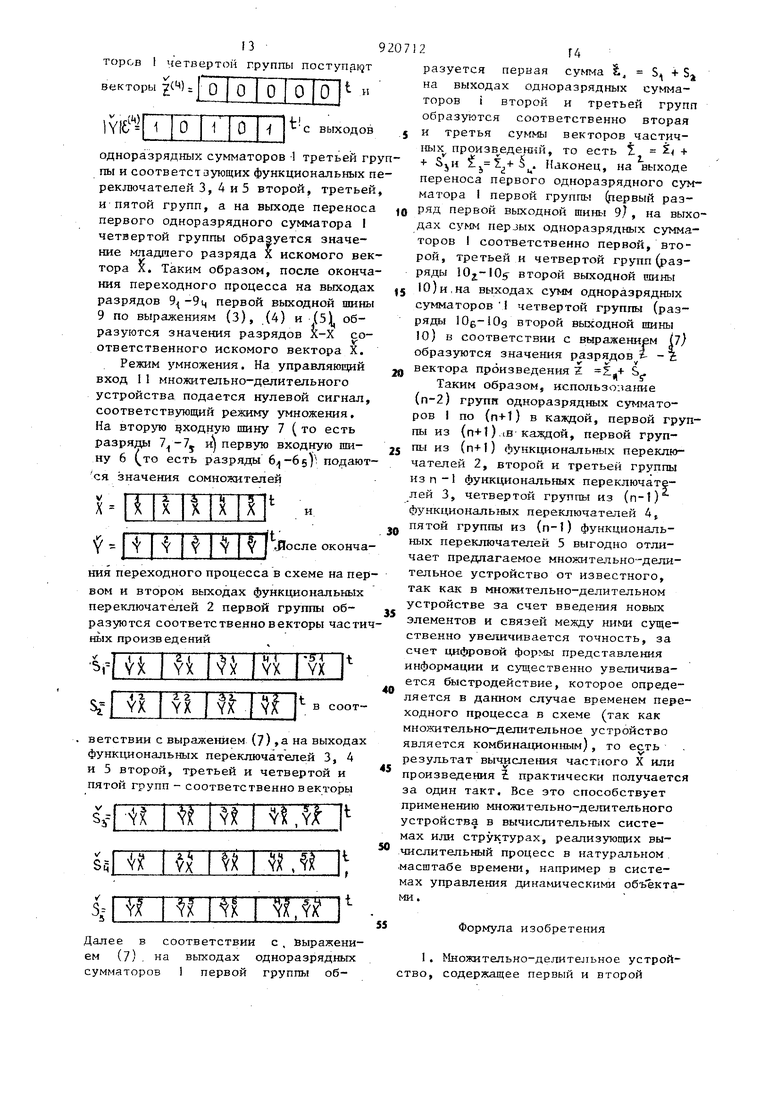

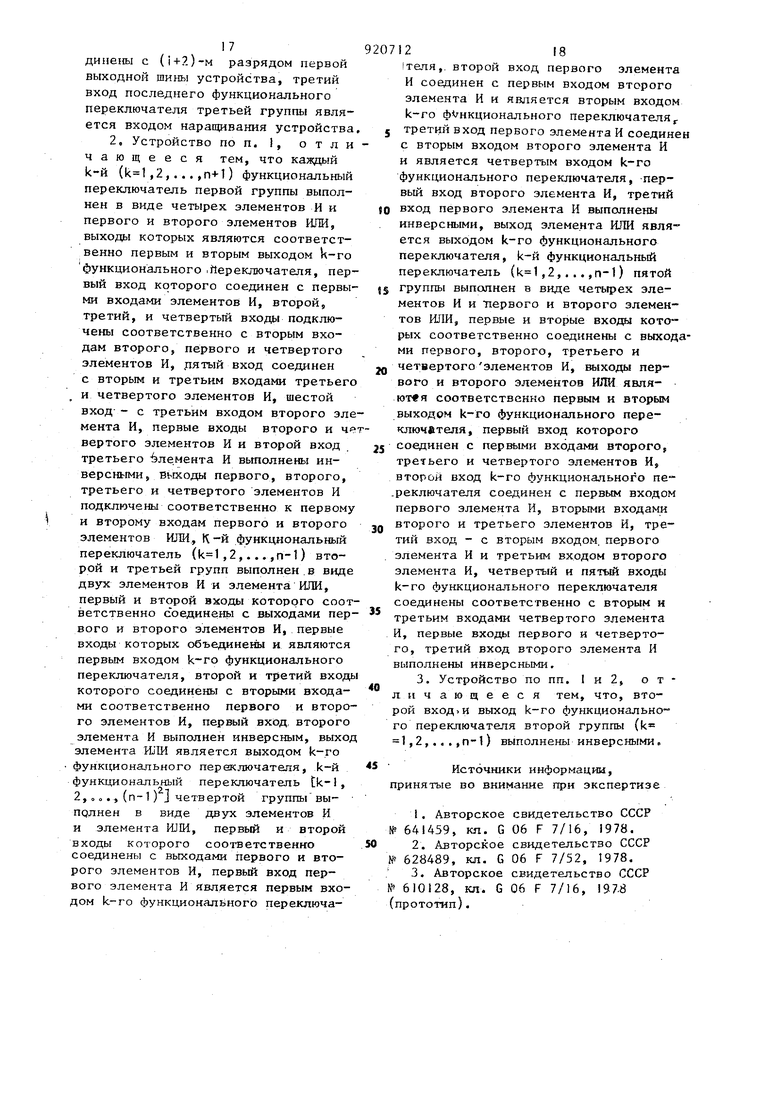

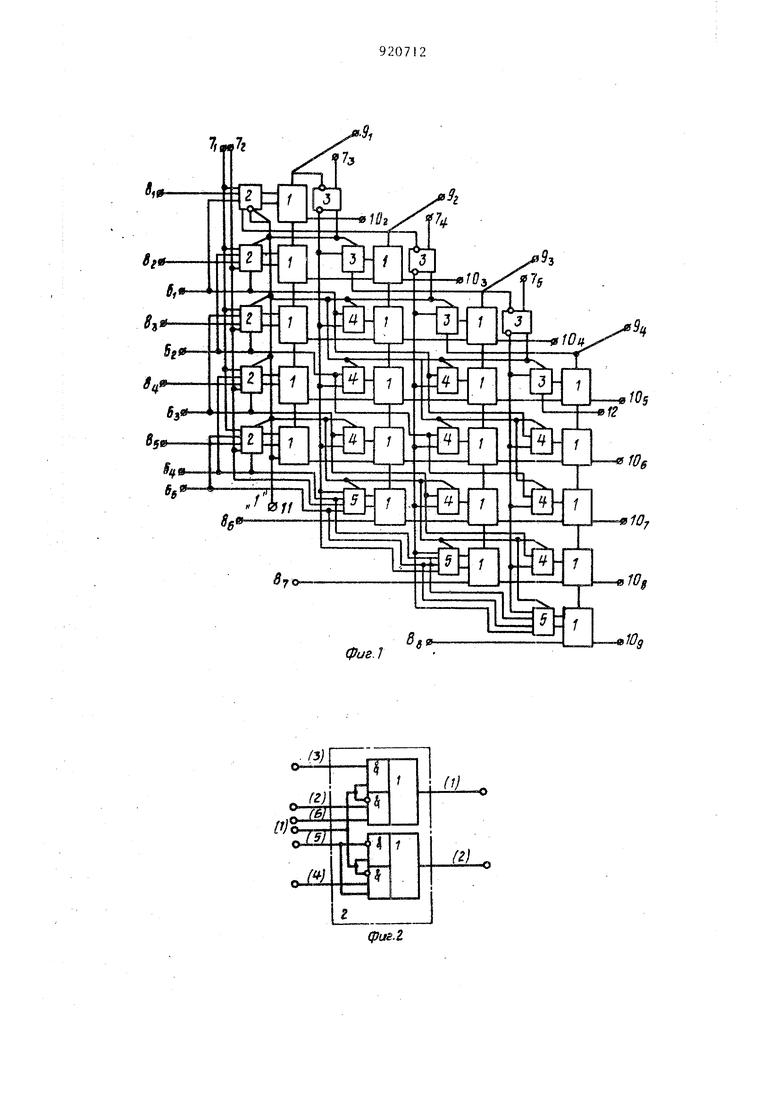

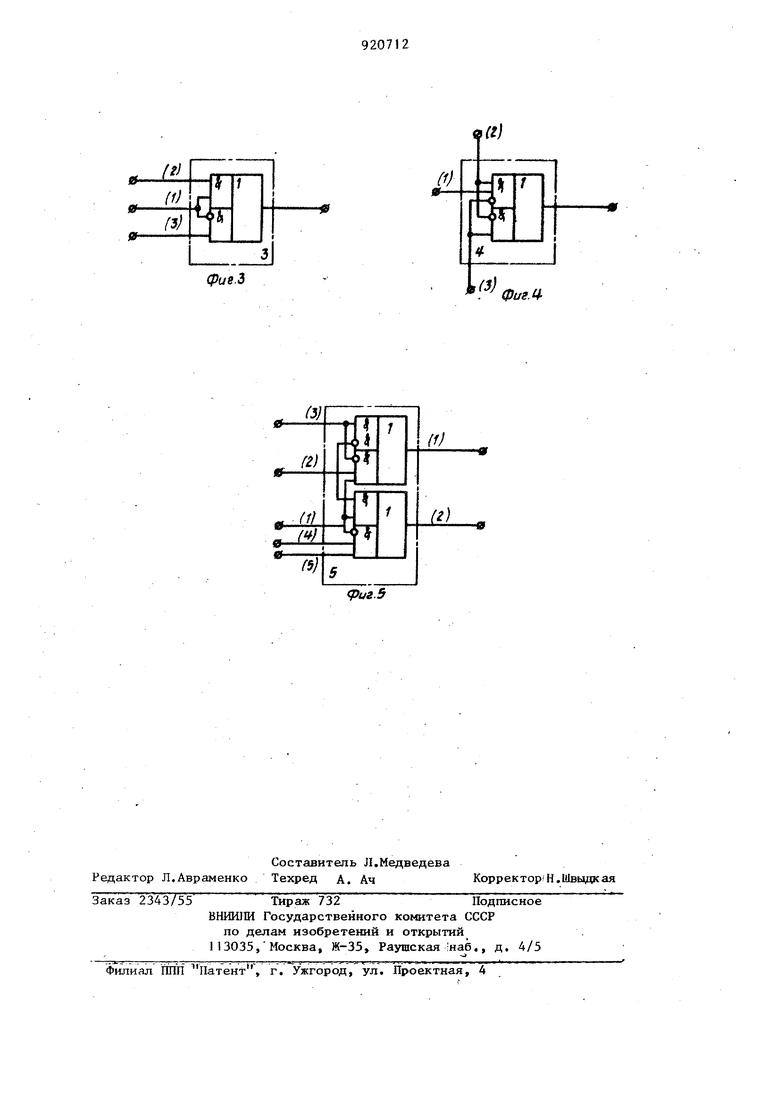

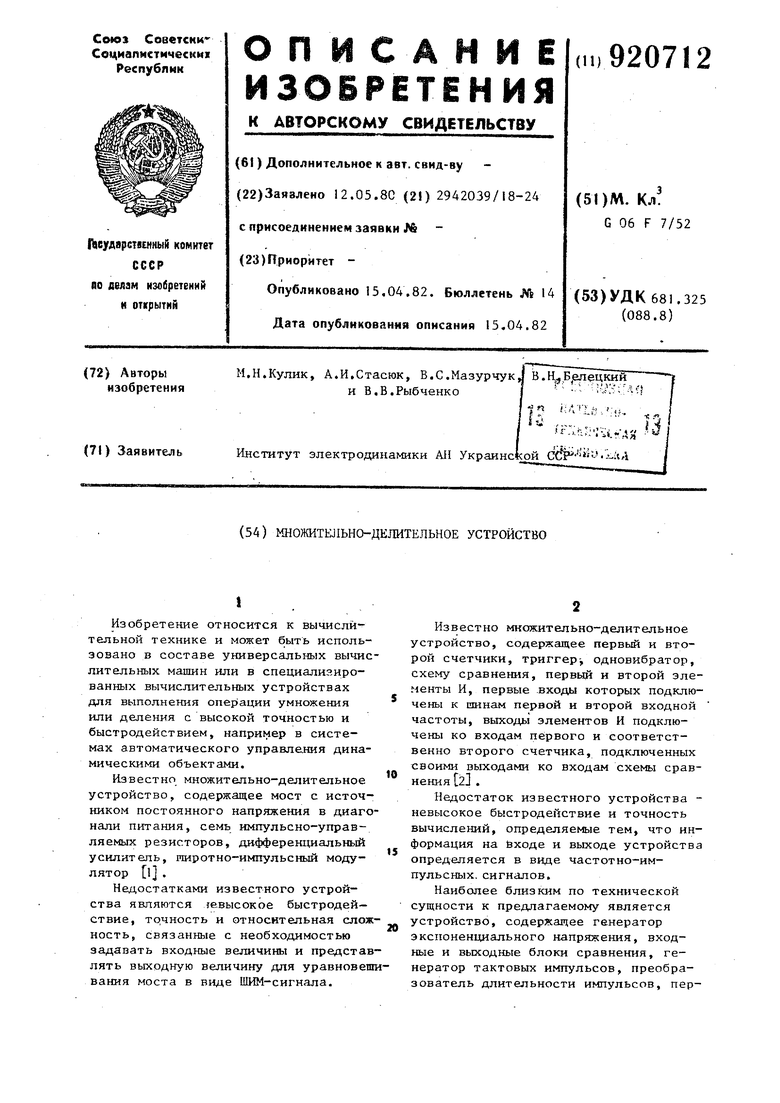

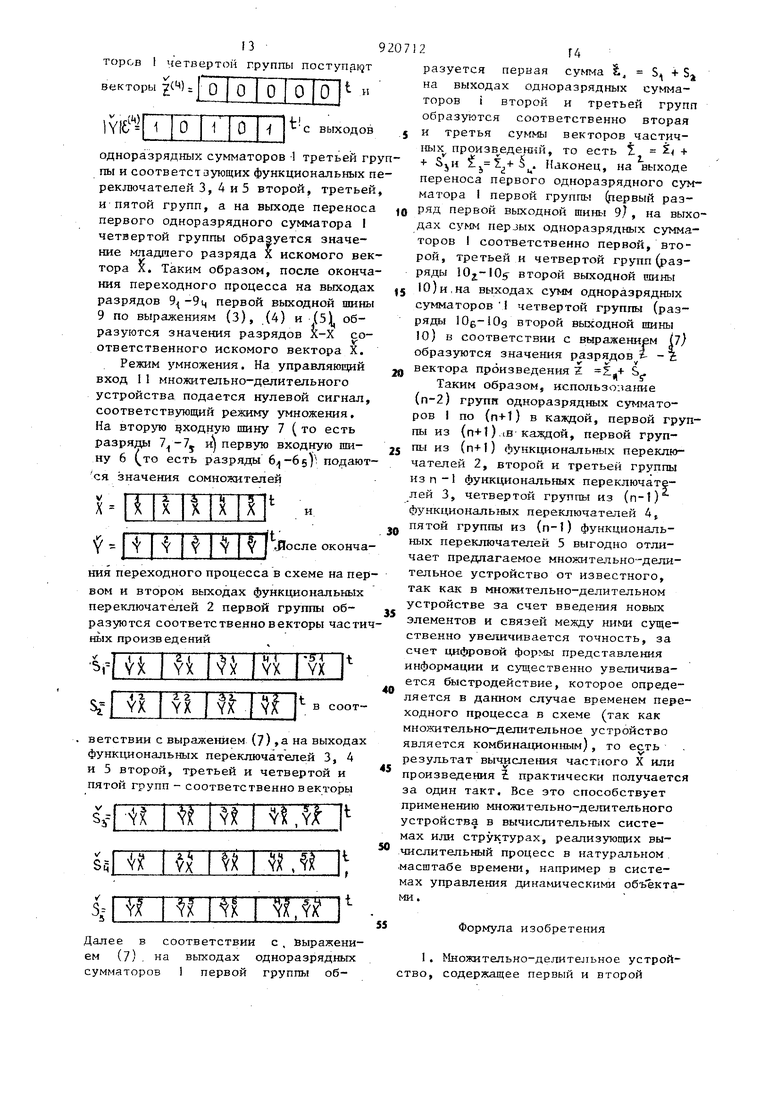

Изобретение относится к вычислительной технике и может быть использовано в составе универсальных вычис лительных машин или в специализированных вычислительных устройствах для выполнения операции умножения или деления с высокой точностью и быстродействием, например в системах автоматического управления динамическими объектами. Известно множительно-делительное устройство, содержащее мост с источ ником постоянного напряжения в диаг нали питания, семь импульсно-управляемых резисторов, дифференциальный усилитель, ииротно-импульсный модулятор tlj . Недостатками известного устройства являются невысокое быстродействие, точность и относительная слож ность, связанные с необходимостью задавать входные величины и предста лять выходную величину для уравнове вания моста в виде ШИМ-сигнала. Известно множительно-делительное устройство, содержащее первый и второй счетчики, триггер-, одновибратор, схему сравнения, первый и второй элементы И, первые входы которых подключены к шинам первой и второй входной частоты, выходы элементов И подключены ко входам первого и соответственно второго счетчика, подключенных своими вьгходами ко входам схемы сравнения 2J . Недостаток известного устройства невысокое быстродействие и точность вычислений, определяемые тем, что информация на Входе и выходе устройства определяется в виде частотно-импульсных, сигналов. Наиболее близким по технической сущности к предлагаемому является устройство, содержащее генератор экспоненциального напряжения, входные и выходные блоки сравнения, генератор тактовых импульсов, преобразователь длительности импульсов, первый сумматор, входы которого соеди neiibi с выходами всех преобразователей длительности импульсов, второй сумматор, один 1зход которого сов динен с выходом запоминающего блока а другой - с выходом усилителя рассогласования з. Недостаток известного устройства относительно низкое быстродействие и точность, определяемые тем, что в устройстве осуществляется представление величин входных сигналов в виде соответствующих временных интервалов. Цель изобретения - увеличение быстродействия и точности вычислений. Поставленная цель достигается тем, что в множительно-делительное устройство, содержащее первый и вто рой сумматоры, введены п-2 труппы о .норазрядных сумматоров (п - разрядность .операвдов по п+1 в каждой iгруппе (i 1 ,/I, . .. ,п-2) , первая гру па из п+1 функциональных переключат лей, вторая группа из п-1 функциона ных, переютючателей, третья группа и п-1 функциональных переключателей, / четвертая группа из (п-1) функциональнь1Х переключателей, пятая группа из п-1 функциональных переключателей, причем первые объединенные входы функциональных переключателей первой, второй, третьей, четвертой, пятой групп и первый вход (п+1)го одноразрядного сумматора первой гру пы соединены с управляющим входом устройства, вторые входы функционал ных переключателей первой группы объединены и являются входом младшего разряда второй входной шины, третьи входы функциональных перекпючателей первой группы соединены с соответствукщими разрядными входа ми третьей входной шины, первый и второй входы k-ro одноразрядного су матора (,2,.,,,n) первой группы соединены с первым и вторым выходами соответствующего т-го функционального переключателя ( ,2,. .. ,п первой группы, первый и второй выходы последнего функционального переключателя первой группы соответственно соединены с вторым и третьи входами поспеднего одноразрядного сумматора первой группы, первый выход каждого 1-го одноразрядного сум матора (1 ,2,. , о ,п+1) ,-и группы соединен с первым входом (1-1 )то oдliopaзpяднoгo сумматора ( + 1)-й группы, второй вход каждого -го одноразрядного сумматора (,2,.,.,п) (i-H)-ii группы соединен с выходом функционального переключателя соответствующей группы, первый и второй выход k-ro функционального переключат ел я ( , 2 , . . ...п-1) пятой группы соответственно соединены с первым и вторым входами последнего одноразрядного сумматора соответствующей (i + 1 )-й группы, третий вход которого соединен с входом (n+i)ro разряда третьей входной шины устройства, выход переноса (i+l)-ro одноразрядного сумматора L-и группы соединен со входом переноса -го одноразрядного сумматора этой же группы, выход переноса первого одноразрядного сумматора t-Игруппы соединен со вторым входом соответствующего функционального переключателя второй группы и является t -м разрядом первой выход ной пшны устройства, выход первого одноразрядного сумматора каждой (,-й Группы и выход каждого одноразрядiHoro сумматора последней группы соединены соответственно со входами соответствуюпдах разрядов второй выходНой 1ЛИНЫ устройства, че-лвертьш вход inepBoro функционального переключателя первой группы соединен с выходом переноса первого одноразрядного сумматора (|+1)-й группы, пятый вход первого функ11;ионального переключателя первой группы соединен с управляющим входом устройства, четвертые объединенные входы функциональных переключателей первой группы, начиная со второго, подключены ко входу второго разряда второй входной шины устройства, выход каждого функционального переключателя второй группы соединены со вторыми входами соответствующих функциональных переключателей третьей, четвертой и пятой групп, пятый вход каждого (1+1)-го функционального переключателя первой груп- , пы, начиная со второго, подключен соответственно к шестому входу Е-го функционального переключателя этой же группы, к третьим объединенным входам соответствующих функциональных переключателей четвертой и пятой групп и ко входам соответствующих разрядов первой входной шины устройства, четвертый вход первого функционального переключателя пятой группы подключен (КО входу второго разряда второй вход5ной шн)ш устройства, шестой вход последнего фуикгдионального переключате ля первой группы соединен со входом старшего разряда первой входной шины устройства, с четвертыми входами функциональных переключателей пятой группы, начиная со второго, и с пятым входом первого функционального переключателя этой же группы, пятые входы функциональных переключателей пятой группы, начиная со второго. Соединены с выходом соответствующего функционального переключателя второй группы, третий вход каждого функционального переключателя третьей группы, кроме последнего, соединен с (i+2)-M разрядом первой выходной шины устройства, третий вход последнего функционального переключателя тре тьей группы является входом наращивания устройства, каждый k-й (k . 1 ,2,, .. ,п+1) функционалышй переключатель первой группы выполнен в виде четырех элементов И и первого и второго элементов ИЛИ, выходы кото-25 и рых являются соответственно первым и вторым выходом k-ro функционального переключателя, первый вход которого соединен с первыми входами элементо И, второй, третий и четвертый входы подключены соответственно ко вторым входам второго, первого и четвертого элементов И, пятый вход соединен со вторым и третьим входами третьего и четвертого элементов И, шестой вход - с третьим входом второго элемента И, первые входы второго и четвертого элементов И и второй вход тр тьего элемента И выполнены инверсными, выходы первого, второго, третьег и четвертого элементов И подключены соответственно к первому и второму входам первого и второго элементов ИЛИ, k-й функциональньш переключател (,2,...,п-1) второй и третьей групп выполнен- в виде двух элементов И и элемента ИЛИ, первый и второй входы которого соответственно соединены с выходами первого и второго элементов И, первые входы которых объединены и являются первым вхо дом k-ro функционального переключателя, второй и третий входы которого соединены со вторыми входами соответственно первого и второго элементов И, первый вход второго элемента И выполнен инверсным, выход элемента ИЛИ является выходом k-ro функционального переключателя, k-й функ12циональш.1й переключатель ,2,, . ., (п-1) четвертой группы выполнен в виде двух элементов И и элемента ШШ, первый и второй входы которогср соответственно соединены с выхода№1 первого и второго элементов И, первый вход первого элемента И является первым входом k-ro функционального переключателя, второй вход первого элемента И соединен с первым входом второго элемента И и является вторым входом k-ro функционального переключателя, третий вход первого элемента И соединен со вторым входом второго элемента И и является четвертым входом k-ro функциональfforo переключателя, первый вход второго элемента И, третий вход первого элемента И выполнены инверсными, выход элемента ШШ является выходом k-ro функционального переключателя, k-й функциональный переключатель ,2,...,п-1) пятой группы выполнен в виде четырех.элементов И первого и второго элементов ИЛИ, первые и вторые входы которых соответственно соединены с выходами первого, второго, третьего и четвертого элементов И, выходы первого и второго элементов ШИ являются соответственно первым и вторым выходом li;-го функционального переключателя, первый вход которого соединен с первыми входами второго, третьего и четвертого элементов И, второй вход k-ro функционального переключателя соединен с первьм входом первого элемента И, вторыми входами второго и третьего элементов И, третий вход - со вторым входом первого элемента И и третьим входом второго элемента И, четвертый и пятый входы Х-го функционального переключателя соединены соответственно со вторым и третьим входами четвертого элемента И, входы первого и четвертого, третий вход второго элемента И выполнены инверсными, второй вход и выход jj-го функционального переключа теля второй-группы (,2,...,п-1) выполнены инверсными. На фиг. 1 представлена функциональная схема множительно-делительного устройства для случая, к-огда информация представлена п 4 двоичными раэрядами в режиме деления и п -П+1 в режиме умножения j на фиг.2 - k-й функциональньш переключатель первой группы; на фиг. 3 - то же.

79

второй и третьей группы; на фиг„4 и 5то же, соответственно четвертой и пятой групп.

Множитех ьно-делительное устройство содержит П Групп одноразряднь9с сумматоров 1 по (п+1) в каждой группе (,2,...,п), первую гругР пу из п+1 функциональных пере :спючателей 2, вторую и третью группы из п-1 функциональных переключателей 3, четвертую группу из (п-1) функциональных переключателей 5, первую входную шину 6J (,2,...,п+2), вторую входную шину 71, третью входную шину 81 (,2,...,2п)первую выходную шину 91, вторую выходную шину 10 1 + 1, управлякяций вход 11, вход 12 наращивания.

Первые объединенные входы функциональных переключателей 2, 3, 4 и 5 первой, второй, третьей, четвертой, пятой групп и первый вход (п+ -«1)-го одноразрядного сумматора 1 первой группы соединены с управляющим входом II устройства, вторые вхо ды функциональных переключателей 2 первой группы объединены и являются входом младшего разряда второй входной шины 7, третьи входы функционал№ix переключателей 2 первой группы соединены с соответствующими разрядными входами третьей входной шины 8, nepBbrii и второй входы k-ro одноразрядного сумматора 1 (,2,...,п первой группы соединены -с первым и вторым выходами соответствующего т-го функционального переключателя 2 (,2,..,,п) первой группы, первый и второй выходы последнего функилонального переключателя 2 первой группы соответственно соединены с вторым и третьим входами последнего одноразрядного сумматора 1 первой группы, первый выход каждого 1-го одноразрядного сумматора (,2, ...,п+1) i-и группы соединен с первым входом (1-1)-го одноразрядного сумматора (+1)-й группы, второй вход каждого 1-го одноразрядного суматора I (,2,...,п) ((+1)-й труп пы соединен с выходом соответствующего функционального переключателя ,3,4 или 5 соответствуквдей третьей, четвертой или пятой группы, первый второй выход k-ro функционального переключателя 5 (,2,...,п-1) пятой группы соответственно соединены с первым и вторым входами последнего одноразрядного сумматора 1 соотв2,8

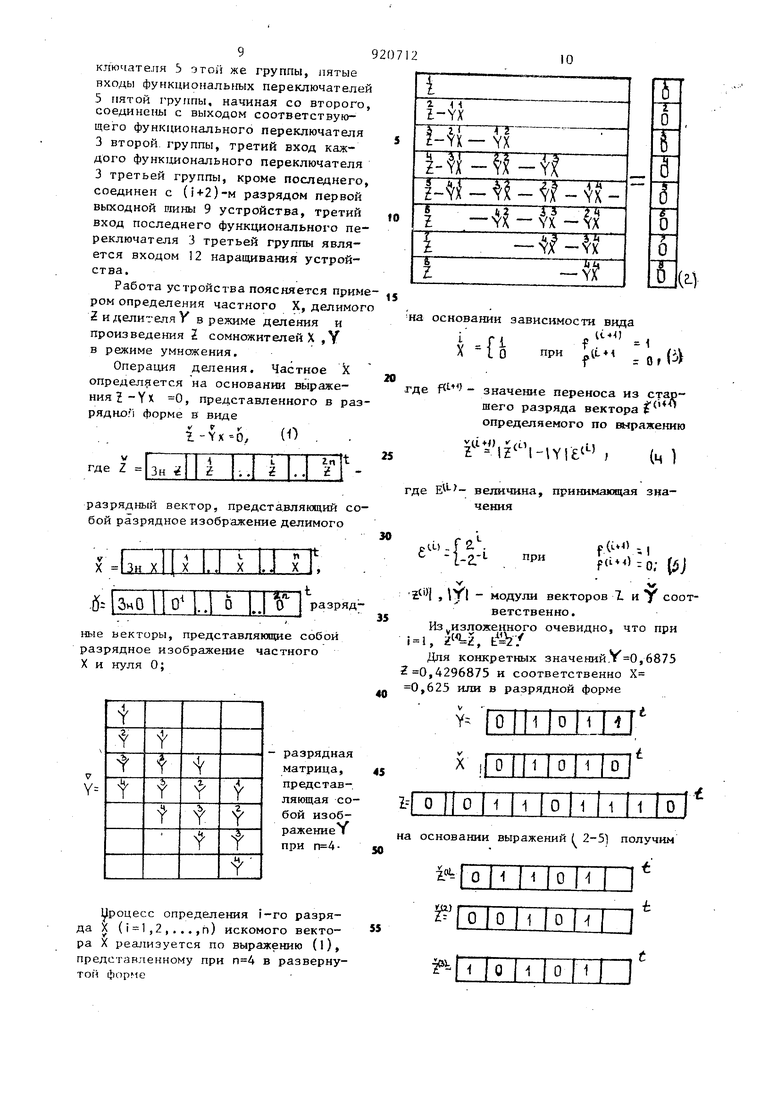

ствуклцей (4-|)-й группы, третий вход которого соединен о входом (n-t-i)-ro разряда третьей входной шины 8 устройства, выход переноса (1+1)-го .одноразрядного сумматора 1 -и группы соединен со входом переноса -го одноразрядного, сумматора I этой же группы, выход переноса первого одноразрядного сумматора 1 1--й группы соединен со вторым входом соответ- : ствугацего функционального переключателя 3 второй группы и является С-м разрядом первой выходной шины 9 уст ройства, выход первого одноразрядно1го сумматора 1 ка;«дой L-й группы и выход каждого одноразрядного сумматора 1 последней группы соединены соответственно со входами соответствуюпщх разрядов второй выходной шины 10 устройства, четвертый вход первого функционального переключателя 2 первой группы соединен с выходом переноса первого одноразрядного сумма-тора 1 (|+1)-й группы, пятый вход первого функционального переключателя 2 первой группы соединен с управляющим входом I 1 устройства,; четвертые объединенные входы функциональных переключателей 2 первой группы, начиная со второго, подключень ко входу второго разряда второй входной шины 7 устройства, выход каждого функционального переключателя 3 второй группы соединен со вторыми входами соответствующих функциональных переключателей 3, 4 и 5, соответственно третьей, четвертой и пятой групп, пятый вход каждого ( функционального переключателя 2 первой групльз, начиная со второго, подключен соответственно к шестому входу 1-го функционального .переключателя 2 этой же группы, к третьим объединенным входам соответствукяцнх функциональных переключателей 4 и 5 четвертой и пятой групп и ко входам соответствуюш х разрядов первой входной шины 6 устройства четвертый вход первого функционального переключателя 5 пятой группы подключен ко входу второго разряда второй входной шины 7 устройства, шестой вход последнего функционального переключателя 2 первой группы соединен со входом старшего разряда первой входной шины б устройства, с четвертыми входами функцио. нальных переключателей 5 пятой группы, начиная со второго, и с пятьм входом первого функционального пере99ключателя 5 этой же группы, лятые входы функциональных переключателей 5 пятой группы, начиная со второго, соединены с выходом соответствующего функционального переключателя 3 второй группы, третий вход каждого функционального переключателя 3 третьей группы, кроме последнего, соединен с (+2)-м разрядом первой выходной шинь 9 устройства, третий вход последнего функционального переключателя 3 третьей группы является входом 12 наращивания устройства. Работа устройства поясняется приме ром определения частного X, делимого 2 и делителя У в режиме деления и произведения Z сомножителей X ,Y в режиме умножения. Операция деления. Частное X определяется на основании выражения 2-Ух 0, представленного в разрядном форме в виде

где Z

разрядный вектор, представляющий собой разрядное изображение делимого

разрядные векторы, представляющие собой разрядное изображение частного X и нуля 0;

- разрядная матрица, представляющая собой изображение Т при п 4Цроцесс определения i-го разряда X (,2,...,h) искомого вектора X реализуется по выражению (1), представленному при в развернутой форме

где величина, принимающая значения

.а).Га

f ( -, I

-1-2:

при )ro; {5J

Y-«г

iVl модули векторов Z и j соответственно. Из изложенного очевидно, что при

i i, ,

Для конкретных значений. 0,6875 ,4296875 и соответственно Х 0,625 или в разрядной форме вании зависимости вида П f п - f rOrli - значение переноса из стар шего разряда вектора определяемого по выражению Z lz VlYlfe , (ц)

Операция умножения. Произведение Z сомножителей Х Y определяется на основании выражения ,i пред ставленного в разрядной форме в виде

V V V

,

(6)

что в развернутом виде при n)Trf-l 5 может быть записано

Рассмотрим работу множительноделительного устройства для конкрет ных значений 2, , X описанного примера в режиме умножения и деления,

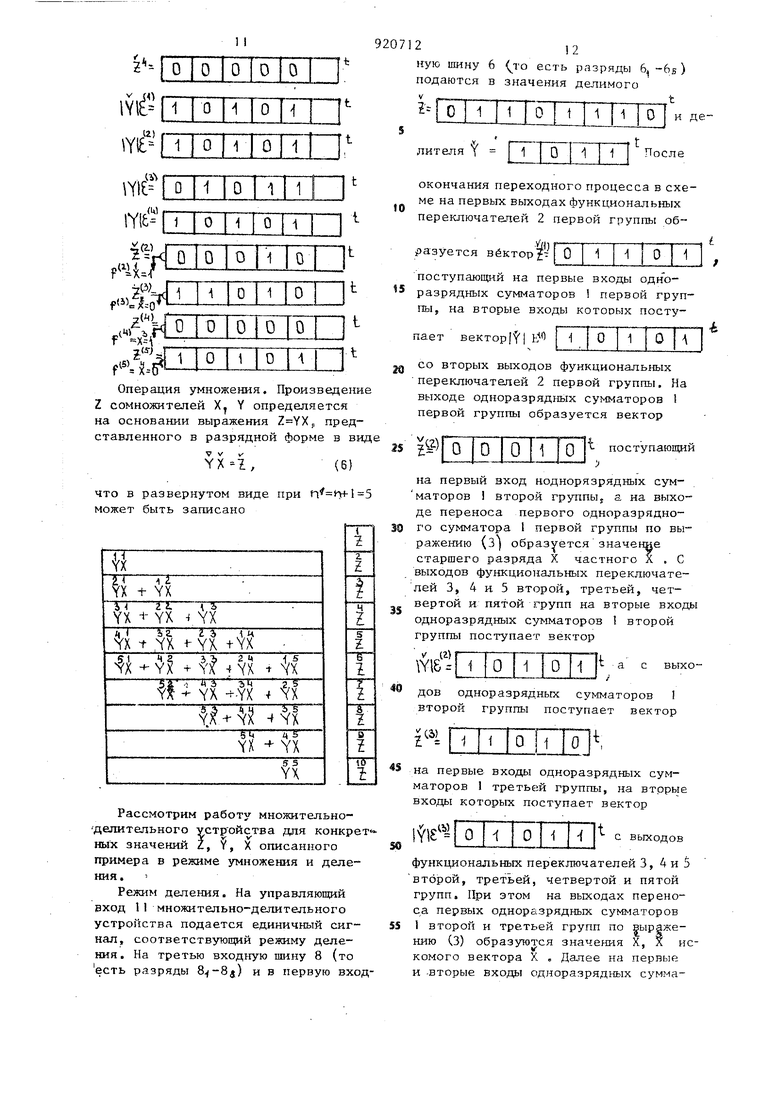

Режим деления. На управляющий 0ХОД 11 множительно-делительного устройства подается единичный сигнал, соответствующий режиму деления. На третью входьгую шину 8 (то есть разряды ) и в первую вход920712,2

ную шину 6 то есть разряды 6 -6s) подаются в значения делимого

t

лителя Y

После

окончания переходного процесса в схеме на первых выходах функциональных переключатапей 2 первой группы обпоступающий на первые входы одно 5 разрядных сумматоров 1 первой груп пы, на вторые входы которых поступает BeKTopltl

20 со вторых выходов функциональных переключателей 2 первой группы. На выходе одноразряднь1х сумматоров 1 первой группы образуется вектор

1

ts

поступающий

на первый вход ноднорязрядных сумматоров 1 второй группы, а на выходе переноса первого одноразрядного сумматора 1 первой группы по выражению (З) образуется значение старшего разряда X частного л , С выходов функциональных переключателей 3, 4 и 5 второй, третьей, четвертой и пятой групп на вторые входы одноразрядных сумматоров второй группы поступает вектор V (г)

У1Б -выходов одноразрядных сумматоров 1 второй группы поступает вектор

на первые входы одноразрядных сумматоров 1 третьей группы, на вторые входы которых поступает вектор

1,2

с выходов

функциональных переключателей 3, А и 5 второй, третьей, четвертой и пятой групп. При этом на выходах переноса первых одноразрядных сумматоров 1 второй и третьей групп по выражению (3) образуются значения X, X искомого вектора X , Далее на первые и .вторые входы одноразрядных сумматоров 1 четвертой группы nocTynaHjT одноразрядных сумматоров -1 третьей г пы и соответствующих функциональных реключателей 3, 4 и 5 второй, третье и пятой групп, а на выходе перенос первого одноразрядного сумматора I четвертой группы образуется значение младшего разряда л искомого ве тора л. Таким образом, после оконча ния переходного процесса на выходах разрядов первой выходной шины 9 по выражениям (З), (4) и (5 образуются значения разрядов Х-Х соответственного искомого вектора X. Режим умножения. На управляющий вход 11 множительно-делительного устройства подается нулевой сигнал соответствующий режиму умножения. На вторую цхокную шину 7 ( то есть разряды и) первую входную ши(15/ - .. то есть разряды ) подают ся значения сомноясителей ,Яосле оконча ния переходного процесса в схеме на пер вом и втором вьгходах функциональнь1х переключателей 2 первой гругап. образуются соответственно векторы части нь1х произведений 5гИГ|уПТМ в соответствии с выражением (7),а на выходах функциональных переключателей 3, 4 и 5 второй, третьей и четвертой и пятой групп- соответственно векторы МуП уДДалее в соответствии с , выражением (7/ . на вьгходах одноразрядных сумматоров 1 первой группы об55 Формула изобретения

фигЛ

(рие.З

,i(3)

фиг.Ц

Авторы

Даты

1982-04-15—Публикация

1980-05-12—Подача