Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах управления технологическими процессами, в экспертных системах искусственного интеллекта.

Целью изобретения является упрощение процессора и повышение его быстродействия.

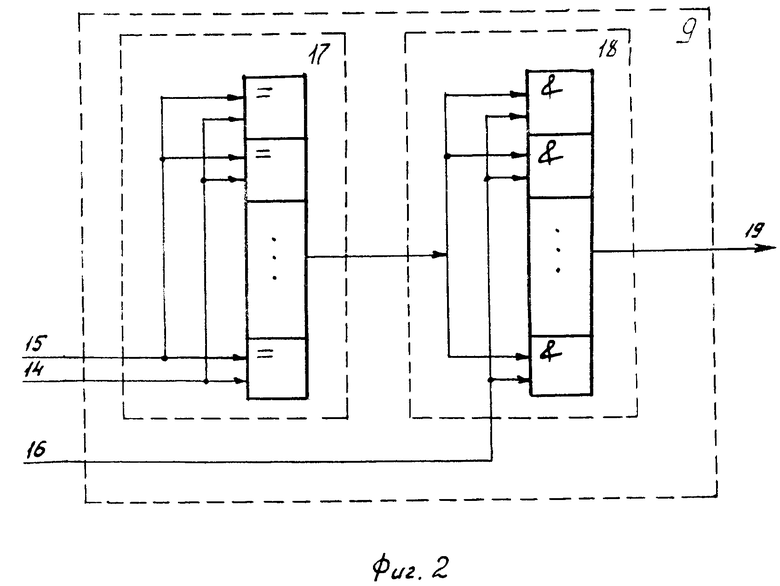

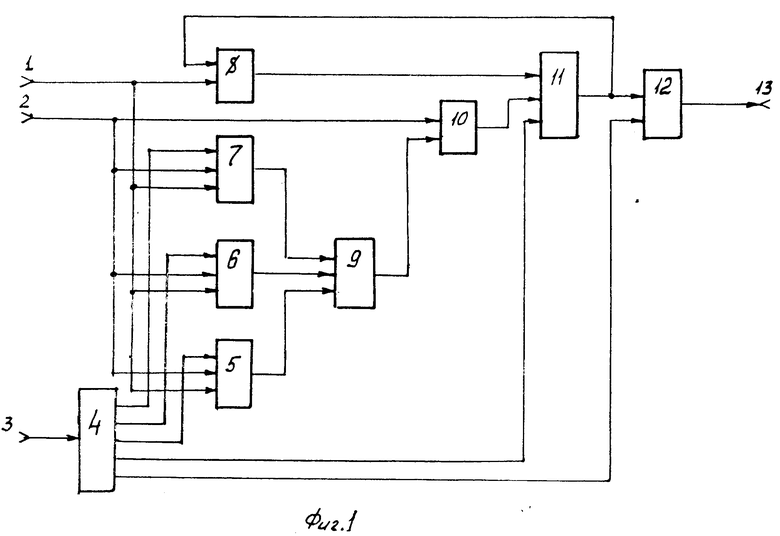

На фиг. 1 показана схема логического процессора; на фиг. 2 - схема блока вычисления логических функций; на фиг. 3 - временные диаграммы работы процессора.

Логический процессор содержит (фиг. 1) вход 1 данных, вход 2 синхронизации, вход 3 адресов, дешифратор 4, регистр 5 аргумента, первый регистр 6 коэффициентов, второй регистр 7 коэффициентов, сумматор 8, блок 9 вычисления логических функций, элемент И 10, регистр 11 суммы, регистр 12 результата и выход 13.

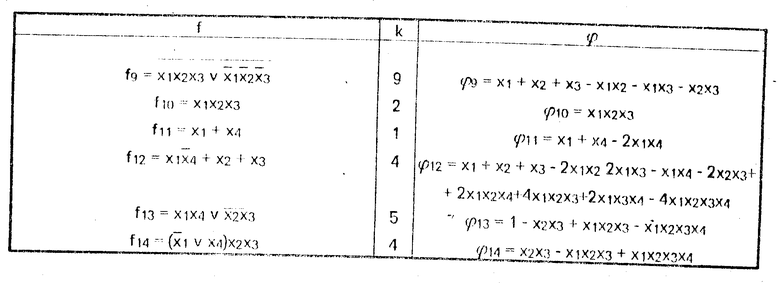

Блок 9 вычисления логических функций содержит (фиг. 2) выходы 14, 15 и 16, узел 17 элементов равнозначности, узел 18 элементов И, выход 19.

Процессор работает следующим образом.

Система логических функций представляется в виде арифметического полинома, образуемого путем арифметического сложения логических функций (f1, . . . , fm), каждая из которых взята со своим коэффициентом (двоичным весом 21-1):

Р= f +f

+f +f

+f +. . .

+. . .

Каждый разряд вычисленного полинома равен значению некоторой функции, определяемой соответствующим коэффициентом, и задача обработки системы логических функций сводится к вычислению полинома.

В регистры 5,6,7 по входу 1 данных пересылаются аргументы функции х и коэффициенты М1 и М2 в последовательности, показанной на диаграмме (фиг. 3). Каждое данное сопровождается по входу 3 своим адресом, преобразуемым на дешифраторе 4 в сигналы выборки соответствующих регистров 5, 6, 7.

В момент, когда на вход сумматора 8 приходит аргумент Х1, на выходе блока 9 уже сформировано значение конъюнкции на этом аргументе (в соответствии с формулой условия равенства конъюнкции единице) и регистр 11 выбран для записи суммы аргумета Х1 с содержимым регистра 11, в котором уже содержится результат суммирования i-1 членов полинома. Такт записи в регистр 11 формируется на выходе элемента И 10 только в том случае, если значение конъюнкции равно единице, т. е. в регистре 11 осуществляется накопление только тех аргументов, при которых значение конъюнкций равно единице. Окончательный результат вычислений записывается в регистр 12.

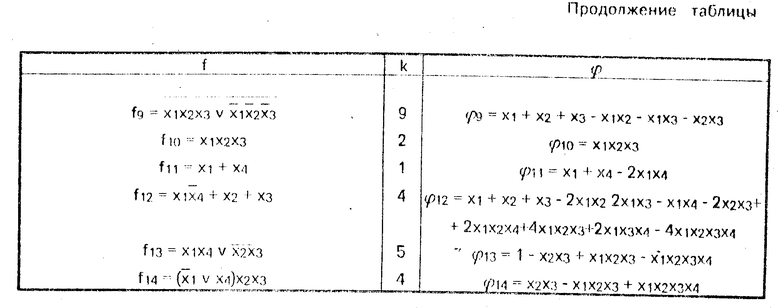

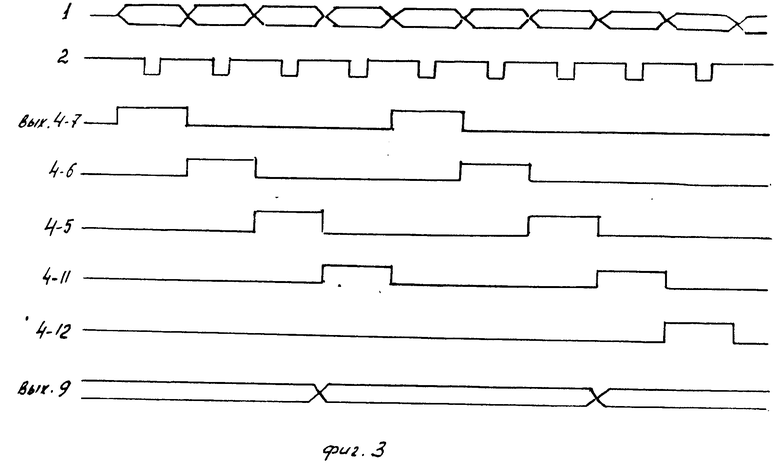

В качестве примера рассмотрена система из 14 логических функций от четырех переменных: f1, . . . , f14 (см. таблицу). Для каждой из функций указано число команд (k), необходимое для ее реализации на известных устройствах посредством обычных операторных программ. Дано арифметическое представление этих же функций ϕ1, . . . , ϕ 14. Арифметическое представление исходной системы функций посредством преобразования 2i-1= P(x) Р(х)= 4263хo-914х1+218х2+2159х3+1032х4

2i-1= P(x) Р(х)= 4263хo-914х1+218х2+2159х3+1032х4

Реализация данного полинома на предложенном параллельном логическом процессоре требует пять тактов. Вычисление на известных устройствах (даже без учета необходимых команд перехода от функции к функции) требует 55 тактов.

(56) Мишев Ж. и др. Программируемые контроллеры. М. : Машиностроение, 1986, с. 36.

Авторское свидетельство СССР N 1136145, кл. G 06 F 7/00, 1981.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления полиномов | 1985 |

|

SU1277098A1 |

| Специализированный процессор | 1981 |

|

SU1023339A1 |

| Устройство для вычисления коэффициентов интерполирующего полинома | 1990 |

|

SU1748158A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| СПЕЦПРОЦЕССОР ДЛЯ ЗАДАЧИ ВЫПОЛНИМОСТИ БУЛЕВЫХ ФОРМУЛ | 2013 |

|

RU2515206C1 |

| Устройство для вычисления полиномов | 1989 |

|

SU1674112A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах управления технологическими процессами. Цель изобретения - упрощение устройства и повышение его производительности при логических вычислениях. Это достигается тем, что в результате применения арифметических форм описания систем логических уравнения в предлагаемом устройстве использованы три параллельно соединенных регистра аргументов функции и коэффициентов, которые через логический блок реализуют быстрые логические вычисления. 1 табл. 3 ил.

ЛОГИЧЕСКИЙ ПРОЦЕССОР, содержащий регистр аргумента и сумматор, информационный вход регистра аргумента соединен с входом данных процессора и первым входом сумматора, вход синхронизации - с входом синхронизации процессора, вход разрешения - с первым выходом дешифратора, вход которого подключен к входу адресов процессора, отличающийся тем, что, с целью упрощения и повышения быстродействия, процессор содержит первый и второй регистры коэффициентов, регистр суммы, регистр результата, блок вычисления логических функций и элемент И, причем информационные входы первого и второго регистров коэффициентов соединены с входом данных процессора, входы синхронизации - с входом синхронизации процессора, входы разрешения - с вторым и третьим выходами дешифратора, четвертый выход которого подключен к входу разрешения регистра суммы, информационный вход которого соединен с выходом сумматора, а вход записи - с выходом элемента И, первый вход которого подключен к входу синхронизации процессора, второй вход элемента И соединен с выходом блока вычисления логических функций, первый, второй и третий входы которого соединены с выходами регистра аргумента и первого и второго регистров коэффициентов соответственно, пятый выход дешифратора подключен к входу записи регистра результата, информационный вход которого подключен к выходу регистра суммы и второму входу сумматора, а выход регистра результата подключен к выходу процессора, причем блок вычисления логических функций содержит узел элементов равнозначности и узел элементов И, выходы которого через МОНТАЖНОЕ ИЛИ подключены к выходу блока вычисления логических функций, первый и второй входы элементов узла равнозначности и первый вход узла элементов И подключены соответственно к первому, второму и третьему входам блока вычисления логических функций, выход узла элементов равнозначности соединен с вторым входом узла элементов И.

Авторы

Даты

1994-01-30—Публикация

1991-02-15—Подача