Изобретение относится к вычислительной технике, в частности к устройствам для реализации математических зависимостей, предназначено для вычисления алгебраических полиномов вида:

N Pk Z У akXk k 1

и может быть использовано в устройствах обработки данных при решении систем алгебраических и дифференциальных уравнений с правой частью, содержащей несколько типов нелинейностей, т е, при решении задач вычисления полиномов с текущими значениями аргументов хк и аппроксимации элементарных функций.

Цель изобретения - расширение области применения за счет возможности вычисления значений полинома при произвольных натуральных показателях степени изменяющегося аргумента.

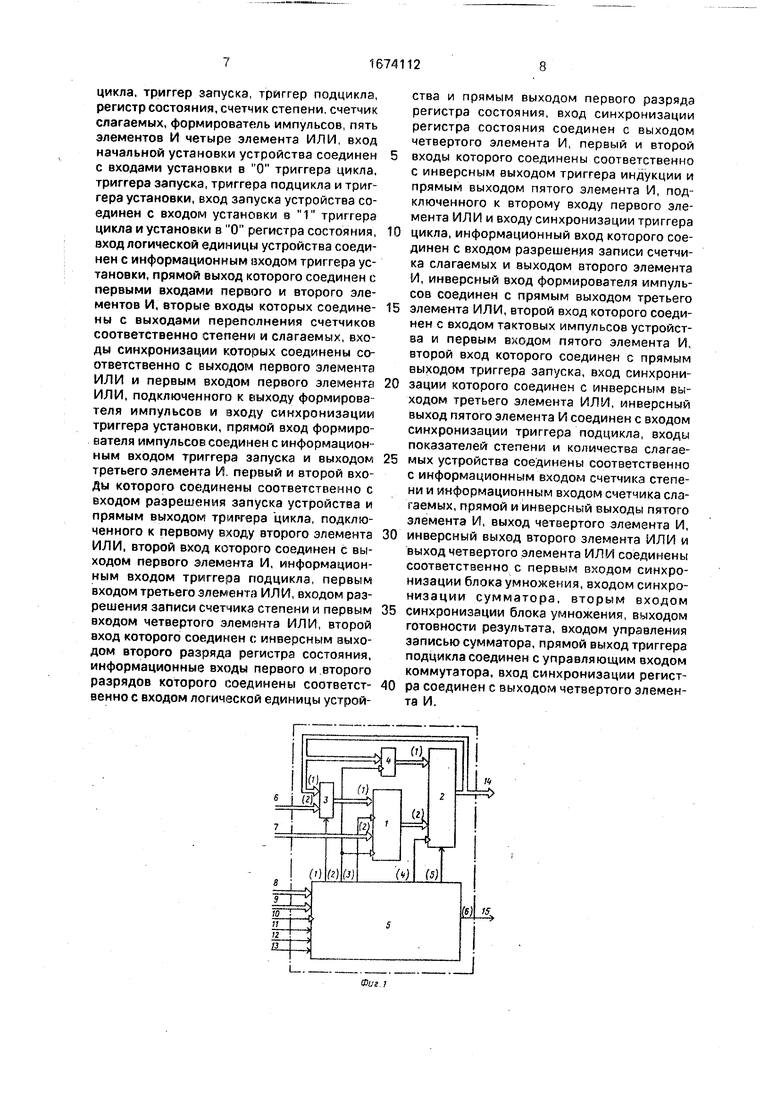

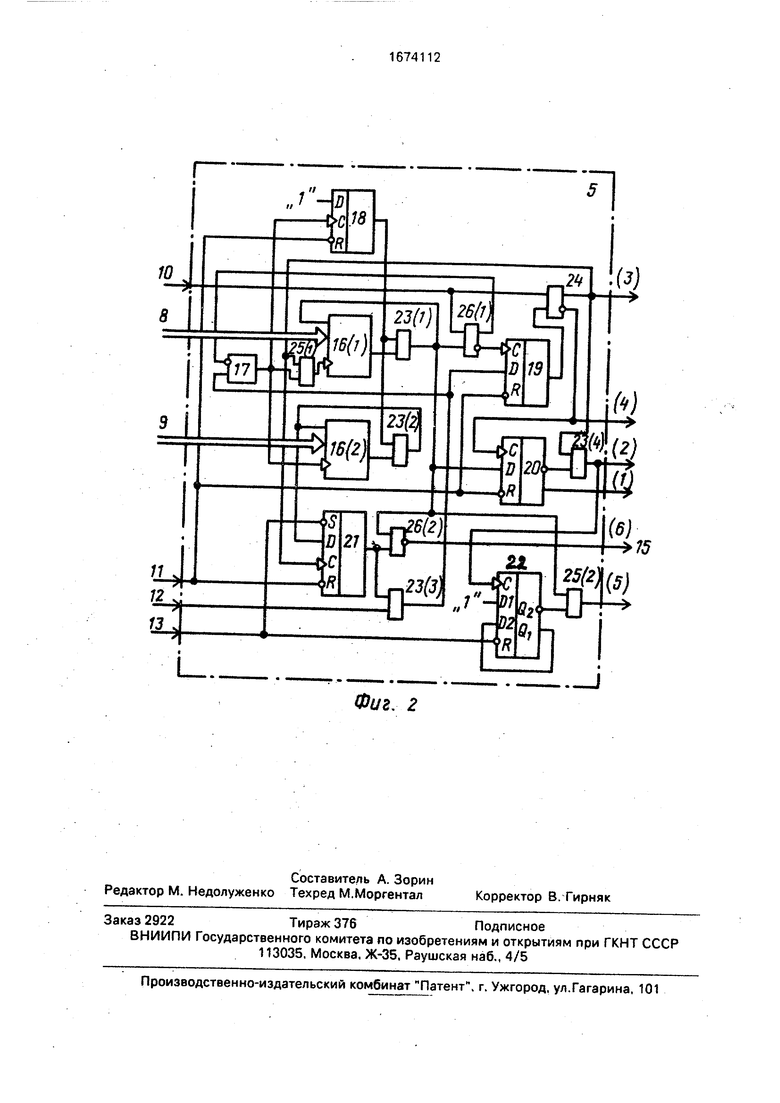

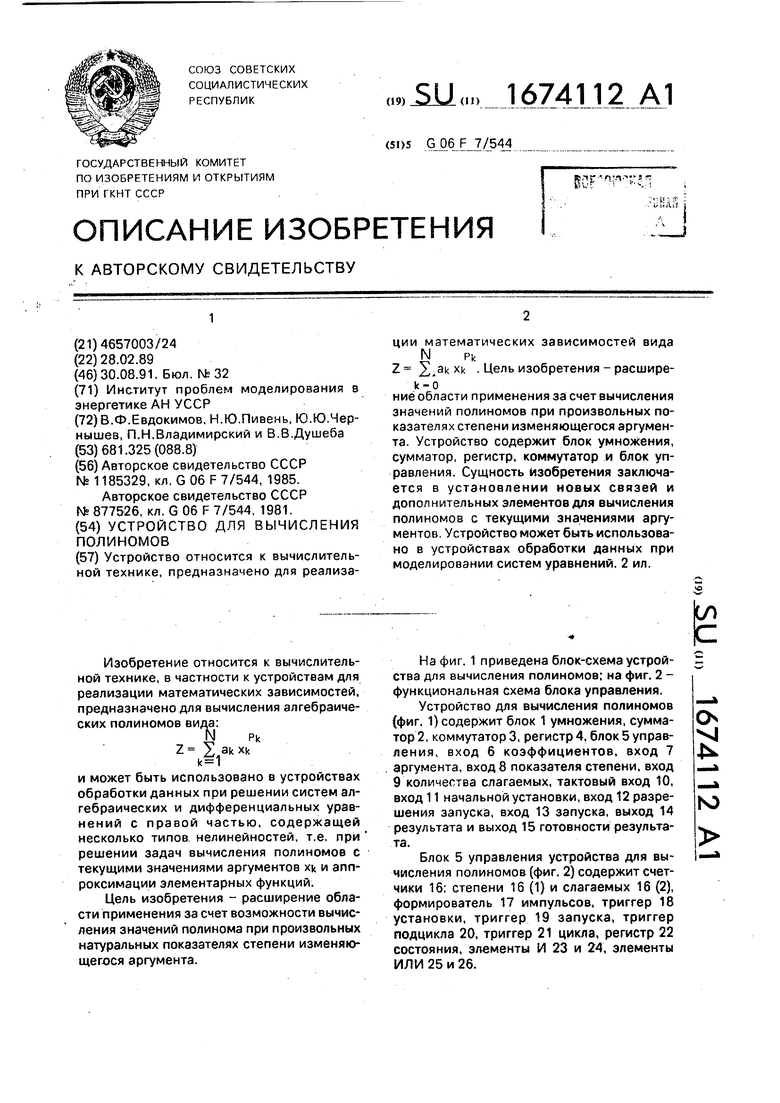

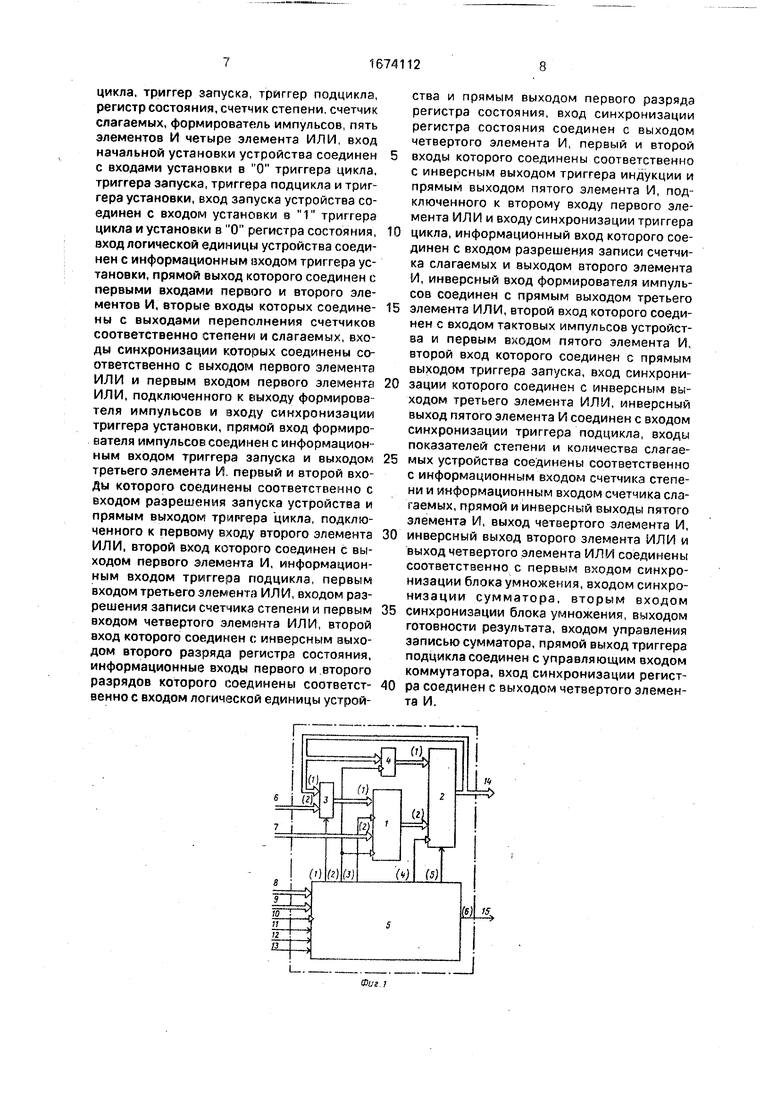

На фиг. 1 приведена блок-схема устройства для вычисления полиномов; на фиг. 2 - функциональная схема блока управления.

Устройство для вычисления полиномов (фиг. 1) содержит блок 1 умножения, сумматор 2, коммутатор 3, регистр 4, блок5управ- ления, вход 6 коэффициентов, вход 7 аргумента, вход 8 показателя степени, вход 9 количества слагаемых, тактовый вход 10, вход 11 начальной установки, вход 12 разрешения запуска, вход 13 запуска, выход 14 результата и выход 15 готовности результата.

Блок 5 управления устройства для вычисления полиномов (фиг. 2) содержит счетчики 16. степени 16 (1) и слагаемых 16 (2), формирователь 17 импульсов, триггер 18 установки, триггер 19 запуска, триггер подцикла 20, триггер 21 цикла, регистр 22 состояния, элементы И 23 и 24, элементы ИЛИ 25 и 26.

О VI

Јь

ьо

Здесь и Е дальнейшем цифрами в скобках, стоящими после номера позиций, показаны порядковые номера совершенно одинаковых по своему функциональному назначению и техническому исполнению элементов и узлов, а просто цифрами в скобках, стоящими возле контура блоков, показаны порядковые номера их входов или выходов.

Устройство для вычисления полиномов работает следующим образом.

По сигналу начальной установки с входа 11 устройства производится обнуление триггера установки 18, триггера запуска 19, триггера 20 подцикла и триггера 21 цикла. Нулевой сигнал с выхода триггера установки 18 через 23 (1) и 23 (2) элементы И подается на входы разрешения записи соответственно счетчика степени 16 (1) и счетчика слагаемых 16(2), определяя работу их в режиме загрузки информации, подаваемой соответственно с входа 8 показателя степени и входа 9 количества слагаемых устройства.

Нулевой сигнал с выхода триггера 19 запуска, подаваемый на второй вход элемента И 24, исключает возможность формирования синхросигналов Тх, Ti и Та на (2), (3) и (4) выходах блока управления 5 соответственно. По сигналу запуска с входа 13 производится установка в единичное состояние триггера 21 цикла и обнуление регистра 22 состояния. Единичный сигнал с выхода триггера 21 цикла открывает элемент И 23 (3) для прохождения сигнала разрешения запуска с входа 12 устройства.

Исходная информация вычисляемой математической зависимости ао, Хо, Ро, N подается на вход 6 коэффициента, вход 7 аргумента, вход 8 показателя степени и вход 9 количества слагаемых соответственно. О наличии аргумента х по входу 7 устройства свидетельствует сигнал с входа 12 устройства.

При готовности операнда х (единичное значение сигнала разрешения запуска на входе 12 устройС7ва) по отрицательному фронту тактового сигнала с входа 10 устройства триггер 19 запуска переходит в единичное состояние, открывая элемент И 24, что обеспечивает возможность формирования синхросигналов Тх, Ti и Ji на выходах (2), (3) и (4) блока 5. Одновременно по отрицательному фронту тактового сигнала через прямой выход элемента ИЛИ 26 (1) происходит запуск формирователя 17. вырабатывающего одиночный импульс, по положительному фронту которого информация Р0 и N с входов 8 и 9 устройства заносится соответственно в счетчик 16 (1) степени и счетчик 15

(2) слагаемых и осуществляется установка в единичное состояние триггера 18 установки, что переводит счетчики степени 16 (1) и слагаемых 16 (2) из режима загрузки в счет- ный режим.

Цикл работы устройства состоит из N + 1 подциклов длительностью Pk вычислительных тактов каждый. В течение каждого

Pk

0 подцикла вычисляется значение akXk которое, в конце каждого подцикла суммируется в результатом, полученным в предыдущем подцикле.

Каждый вычислительный такт работы

5 устройства состоит из двух подтактов, что определяется наличием операций умножения и сложения, выполняемых соответственно в первом и втором подтактах каждого такта работы устройства.

0 Тактовые сигналы первого - Ti и второго - Т2 подтактов формируются на выходах соответственно (3) и (4) блока 5.

Каждый из двух подтактов каждого такта начинается с приходом положительного

5 фронта соответствующего тактового сигнала - Тч или Т2.

По положительному фронту тактового сигнала с входа 10 устройства на прямом выходе элемента И 24, открытого единич0 ным сигналом с выхода триггера 19 запуска, формируется положительный фронт сигнала TI первого подтакта, под воздействием которого триггер 21 цикла переходит в единичное состояние, а содержимое счетчика

5 степени 16 (1) уменьшается на 1й. отсчитывая один такт работы устройства. Синхросигнал TI через выход (3) блока 5 управления подается на синхровход с блока 1 умножения. Одновременно с этим на выходе эле0 мента И 23 (4) формируется положительный фронт синхросигнала Тх. который через выход (2) блока 5 подается на другой синхровход блока 1 умножения и на синхровход регистра 4. Под воздействием положитель5 ного фронта синхросигнала Т прямой первый выход регистра состояния 22 переходит в единичное состояние.

По отрицательному фронту тактового сигнала с входа 10 устройства на инверсном

0 выходе элемента И 24 формируется положительный фронт сигнала Т2 второго подтакта, под воздействием которого триггер подцикла 20 переходит в единичное состояние, блокируя нулевым сигналом со своего ин5 версного выхода формирование сигнала Тх на выходе элемента И 23 (4). Синхросигнал Т2 подается через выход (4) блока 5 на синхровход сумматора 2,

Во время первого подтакта каждого такта работы устройства в блоке 1 умножения

производится перемножение операндов, заносимых в него с его первого и второго информационных входов по положительным фронтам синхросигналов соответственно Тх и TL поступающих на его синхровходы. Причем информация, поступающая на второй вход блока 1 умножения, определяется сигналом с выхода (1) блока 5, под воздействием которого коммутатор 3 проводит информацию с первого или второго своих информационных входов.

По первому информационному входу блока 1 умножения информация заносится с входа 7 аргумента устройства один раз в подцикле - в начале первого такта каждого подцикла вычислений.

Во время второго подтакта каждого такта работы устройства в сумматоре 2 производится суммирование операндов, занесенных в него по положительному фронту синхросигнала Т2 с выхода (4) блока 5. Причем информация с первого входа сумматора 2 заносится в него в начале второго подтакта каждого такта вычислений и определяется как результат работы блока 1 умножения на первом подтакте.

Со второго входа сумматора 2 в соответствии со значением сигнала с выхода (5) блока 5 заносится информация из регистра 4 на последнем такте каждого, исключая первый, подцикла вычислений, а во всех остальных случаях информация, заносимая в сумматор 2, с его второго входа равна 0.

В конце каждого вычислительного подцикла работы устройства на выходе счетчика степени 16 (1) вырабатывается нулевой сигнал, свидетельствующий о достижении заданной степени аргумента. Наличие этого сигнала устанавливает счетчик степени 16 (1) в режим загрузки информации, открывает третий ИЛИ 26 (1), разрешая запуск формирователя 17, определяет переход триггера подцикла 20 в нулевое состояние по фронту синхросигнала Т2 с инверсного выхода элемента И 24 и открывает элемент ИЛИ 25 (2) для формирования сигнала на выход (5) блока 5.

По отрицательному фронту тактового сигнала с входа 10 устройства происходит запуск формирователя 17, при наличии единичного значения сигнала разрешения запуска, свидетельствующего о готовности информации по входу 7 аргумента и входу 8 показателя степени устройства. По положительному фронту импульса, вырабатываемого формирователем 17, в счетчик степени 16 (1) заносится информация.

Триггер 19 запуска устанавливается в единичное состояние и с приходом положительного фронта тактового сигнала с входа

10 устройства начинается следующий под- цикл вычислений.

В начале каждого подцикла работы устройства по положительному фронту синхро- сигнала Тх с выхода (2) блока 5 в регистр 4 заносится информация с выхода сумматора 2, представляющая собой результат работы устройства в предыдущем подцикле вычислений.

0 Перед началом последнего (N + 1}-го подцикла работы устройства импульс с выхода формирователя 17 обнуляет содержимое счетчика слагаемых 16 (2), о чем свидетельствует нулевой сигнал на его вы5 ходе, который, будучи поданным на вход триггера цикла 21, определяет переход последнего в нулевое состояние по положительному фронту синхросигнала TL

По окончании последнего подцикла ра0 боты обнуляется счетчик степени 16 (1), о чем свидетельствует нулевой сигнал на его выходе, в связи с чем на выходе (6) блока 5 формируется единичное значение сигнала конца цикла вычислений, подаваемое на вы5 ход 15 устройства. По истечении времени второго подката (N + 1)-го подцикла вычислений на выходе 14 результата формируется результат вычислений.

Повторные запуски устройства осуще0 ствляются по сигналу с входа 13 запуска устройства при наличии разрешающего сигнала с входа 12 устройства без предварительной подачи сигнала с входа 11 начальной установки устройства, в котором, в

5 отличие от первоначального запуска, нет необходимости.

Формула изобретения Устройство для вычисления полиномов, содержащее сумматор, блок умножения, ре0 гистр, коммутатор и блок управления, причем вход аргумента устройства соединен с входом первого сомножителя блока умножения, вход второго сомножителя и выход которого соединены соответственно с выхо5 дом коммутатора и входом первого слагаемого сумматора, выход которого соединен с информационным входом регистра и выходом результата устройства, вход коэффициентов которого соединен с первым

0 информационным входом коммутатора, отличающееся тем, что, с целью расширения области применения за счет возможности вычисления значений полинома при произвольных натуральных покаэа5 телях степени изменяющегося аргумента, выход сумматора соединен с вторым информационным входом коммутатора, выход регистра соединен с входом второго слагаемого сумматора, причем блок управления содержит триггер установки, триггер

цикла, триггер запуска, триггер подцикла, регистр состояния, счетчик степени, счетчик слагаемых, формирователь импульсов, пять элементов И четыре элемента ИЛИ, вход начальной установки устройства соединен с входами установки в О триггера цикла, триггера запуска, триггера подцикла и триггера установки, вход запуска устройства соединен с входом установки а 1 триггера цикла и установки в О регистра состояния, вход логической единицы устройства соединен с информационным входом триггера установки, прямой выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с выходами переполнения счетчиков соответственно степени и слагаемых, входы синхронизации которых соединены соответственно с выходом первого элемента ИЛИ и первым входом первого элемента ИЛИ, подключенного к выходу формирователя импульсов и входу синхронизации триггера установки, прямой вход формирователя импульсов соединен с информационным входом триггера запуска и выходом третьего элемента И, первый и второй входы которого соединены соответственно с входом разрешения запуска устройства и прямым выходом триггера цикла, подключенного к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, информационным входом триггера подцикла, первым входом третьего элемента ИЛИ, входом разрешения записи счетчика степени и первым входом четвертого элемента ИЛИ, второй вход которого соединен с инверсным выходом второго разряда регистра состояния, информационные входы первого и второго разрядов которого соединены соответственно с входом логической единицы устройства и прямым выходом первого разряда регистра состояния, вход синхронизации регистра состояния соединен с выходом четвертого элемента И, первый и второй

входы которого соединены соответственно с инверсным выходом триггера индукции и прямым выходом пятого элемента И, подключенного к второму входу первого элемента ИЛИ и входу синхронизации триггера

цикла, информационный вход которого соединен с входом разрешения записи счетчика слагаемых и выходом второго элемента И, инверсный вход формирователя импульсов соединен с прямым выходом третьего

элемента ИЛИ, второй вход которого соединен с входом тактовых импульсов устройства и первым входом пятого элемента И, второй вход которого соединен с прямым выходом триггера запуска, вход синхронизации которого соединен с инверсным выходом третьего элемента ИЛИ, инверсный выход пятого элемента И соединен с входом синхронизации триггера подцикла, входы показателей степени и количества слагаемых устройства соединены соответственно с информационным входом счетчика степени и информационным входом счетчика слагаемых, прямой и инверсный выходы пятого элемента И, выход четвертого элемента И,

инверсный выход второго элемента ИЛИ и выход четвертого элемента ИЛИ соединены соответственно с первым входом синхронизации блока умножения, входом синхронизации сумматора, вторым входом

синхронизации блока умножения, выходом готовности результата, входом управления записью сумматора, прямой выход триггера подцикла соединен с управляющим входом коммутатора, вход синхронизации регистра соединен с выходом четвертого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессорный модуль | 1989 |

|

SU1674111A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для вычисления значений полинома | 1986 |

|

SU1348827A1 |

| Устройство для вычисления полинома @ -ой степени | 1985 |

|

SU1305670A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Специализированный процессор | 1981 |

|

SU1023339A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Устройство для вычисления полиномов | 1978 |

|

SU792263A1 |

| Цифровой функциональный преобразователь | 1979 |

|

SU877526A1 |

Устройство относится к вычислительной технике, предназначено для реализации математических зависимостей вида Z = ΣNAKXK. Цель изобретения - расширение области применения за счет вычисления значений полиномов при произвольных натуральных показателях степени изменяющегося аргумента. Устройство содержит блок умножения, сумматор, регистр, коммутатор и блок управления. Сущность изобретения заключается в установлении новых связей и дополнительных элементов для вычисления полиномов с текущими значениями аргументов. Устройство может быть использовано в устройствах обработки данных при моделировании систем уравнений. 2 ил.

Фиг, 2

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Ветряный двигатель с принудительно поворачиваемыми посредством цепных передач лопастями | 1924 |

|

SU877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1989-02-28—Подача