с входом установки в боль первого триггера, инверсный выход которого соединен с информационным входом пер вого триггера и первым входом второг элемента ИЛИ-НЕ, выход которого соед нен с вторым входом элемента И и вто рым входом узла памяти, третий и четвертый входы которого соединены соответственно с выходом третьего элемента ИЛИ-НЕ и старшим разрядом первого входа блока управления, остальные разряды которого соединены с входами третьего элемента ИЛИ-НЕ, вторые входы первых элементов ИЛИ-НЕ и И-НЕ соединены с вторым входом бло ка управления и первым входом второго элемента И-НЕ, выход которого соединен с вторым входом второго элемента ИЛИ-НЕ и тактовым входом перво го триггера, вход установки в единиц которого соединен с вторым выходом узла памяти, третий выход которого соединен с входами установки в ноль BTopqro и третьего триггеров, входы установки в единицу которых соединены с выходами соответственно первого и третьего элементов И-НЕ, выходы первого элемента ИЛИ-НЕ и второго 1 0 триггера соединены с входами третьего элемента И-НЕ, выход третьего триггера соединен с вторым входом второго элемента И-НЕ, выходы с первого по девятый блока управления соединены соответственно с инверсным выходом младшего разряда счетчика, четвертым, пятым, шестым и седьмым выходами узла памяти, выходом разрядов счетчика, выходом второго элемента ИЛИ-НЕ и третьим выходом узла памяти. 1, отлича2. Устройство по п. блок введения ю щ е е с я тем, что коэффициента содержит сумматор, сдвигатель и узел коррекции, причем информационный вход блока соединен с информационным входом сдвигателя и входом первого слагаемого сумматора вход второго слагаемого которого соединен с выходом сдвигателя и входом узла коррекции, выход которого соединен с входом переноса сумматора и вторь м выходом блока, управляющий вход и первый выход которого соединены соответственно с управляющим входом сдвигателя и выходом сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Устройство для вычисления функций @ @ @ @ и @ @ @ @ | 1990 |

|

SU1732342A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Цифровой функциональный преобразователь | 1986 |

|

SU1361547A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления квадратного корня из суммы квадратов | 1990 |

|

SU1751751A1 |

| Устройство для выполнения векторно-скалярных операций над действительными числами | 1990 |

|

SU1728861A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

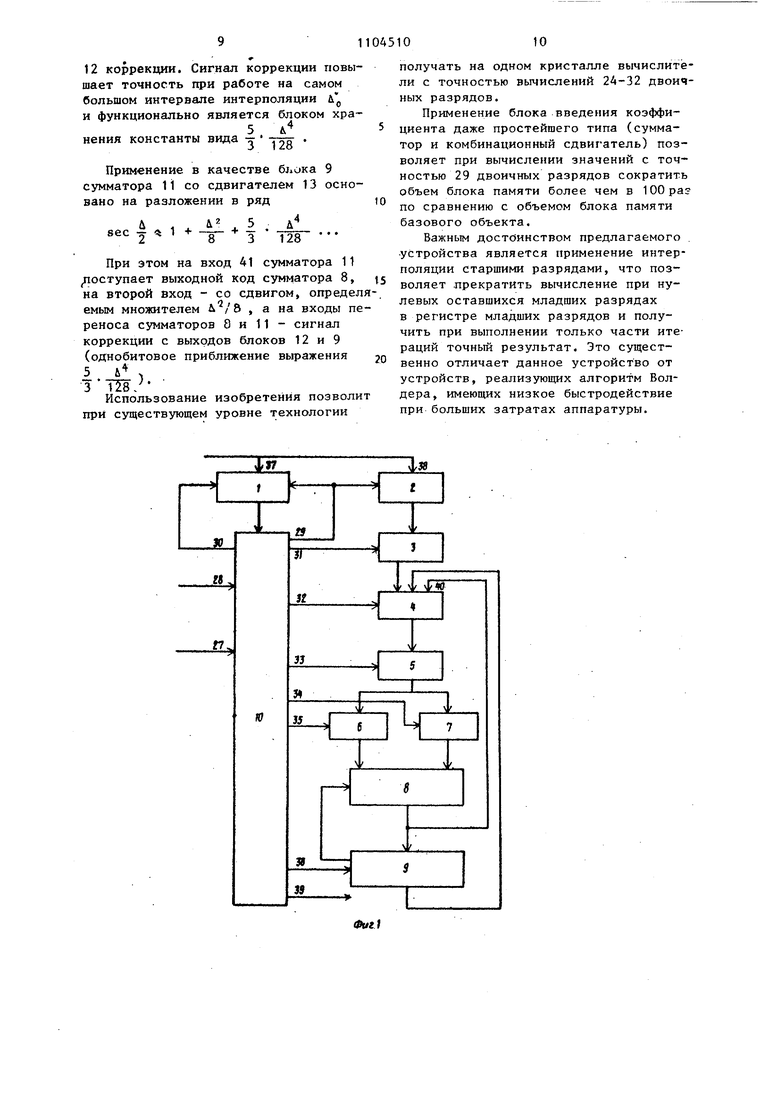

1. ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИНУСНО-КОСИНУСНЫХ ЗАВИСИМОСТЕЙ, содержащее сдвиговый регистр младших разрядов аргумента, регистр старших разрядов аргумента, блок памяти, первый и второй регистры слагаемых, мультиплексор, сумматор и блок управления, выходы с первого по четвертьй которого соединены с управляющими входами соответственно блока памяти, мультиплексора и входами записи первого и второго регистров слагаемых, пятый выход блока управления соединен с входом сдвига сдвигового регистра мпадших разрядов аргумента, выход и вход записи которого соединены соответственно с первым входом блока управления и шестым выходом блока управления, подключенным к входу записи регистра старших разрядов аргумента, выход которого соединен с адресным входом блока памяти, информационные входы сдвигового регистра младших и регистра старших разрядов аргумента соединены с входом аргумента устройства, о т л ичающееся тем, что, с целью сокращения аппаратурных затрат за счет снижения емкости блока памяти, оно содержит регистр узловых значений и блок введения коэффициента, управляющий вход которого соединен с седьмым выходом блока управления, восьмой выход и второй и третий входы которого соединены соответственно с входом записи регистра узловых значений, тактовым входом и входом разрешения записи устройства, девятый выход блока управления соединен с выходом конца преобразования устройства, информационные входы с первого по третий мультиплексора соединены соответственно с вьгходом блока § памяти, выходом cyMi-iaTopa и первым выходом блока введения коэффициента, (Л второй выход и информационный вход которого соединены соответственно с ВХОДОМ переноса и выходом сумматора, первый и второй входы слагаемых которого соединены с выходами соответственно первого и второго регистров слагаемых, информационные входы которых подключены к выходу регистра узловых значений, информационный вход кото сд рого соединен с выходом мультиплексора и выходом устройства, причем блок управления содержит три элемента ИЛИ-НЕ, элемент НЕ, три элемента И-НЕ, элемент И, три триггера, счетчик и узел памяти, первый выход которого соединен с первым входом элемента И, выход которого соединен со счетным входом счетчика, выход которого соединен с первым входом узла памяти, вход обнуления счетчика соединен с третьим входом блока управления, первыми входами первых элементов ИЛИ-НЕ и И-НЕ и через элемент НЕ соединен

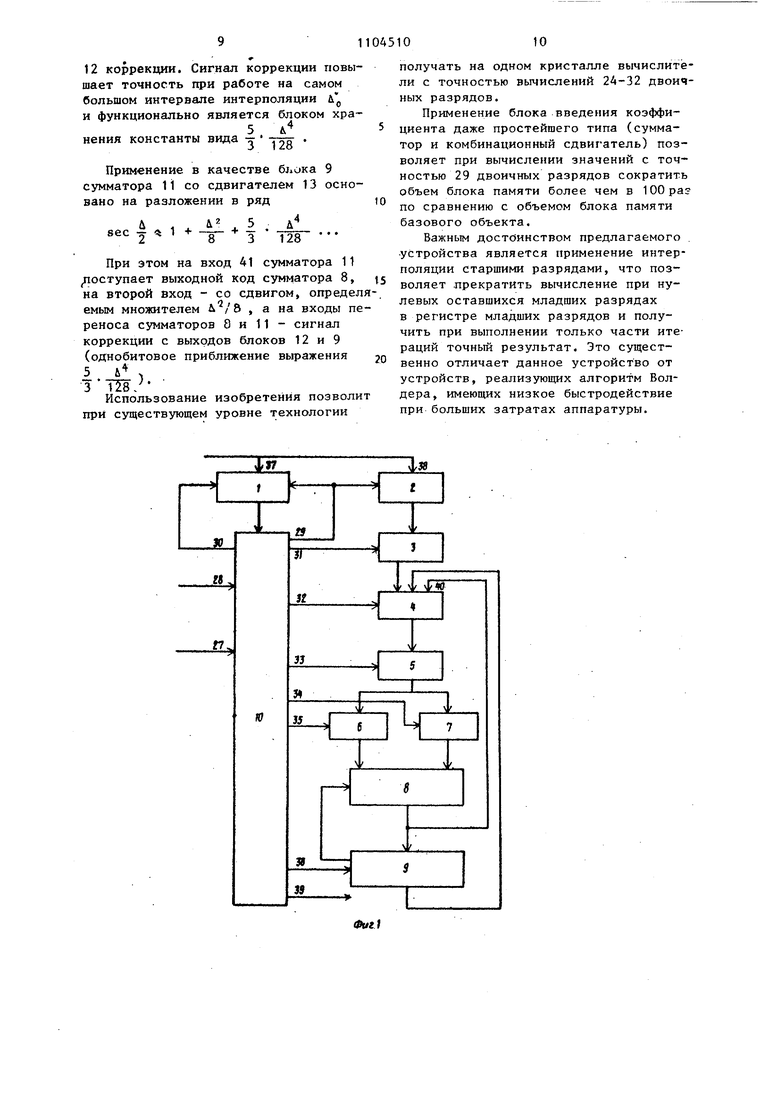

Изобретение относится к вычислительной технике, в частности к цифро вым вычислительным устройствам для нахождения тригонометрических функций, и может быть использовано при разработке больших специализированны интегральных схем для реализации цифровых вычислителей синуса и косинуса, при реализации цифровых вычислителей гиперболического синуса и ко синуса, а также экспоненты. Известен специализированный процессор, содержащий регистр, блок умножения, сумматор, элементы И, блок памяти, блок управления, сдвигатель Приближающий полином вычисляется по схеме Горнера. Наличие комбинационного блока умножения повъшает быстродействие Л . Недостатком этого процессора является его сложность. Наиболее близким к данному устройству является арифметическое устройство специализированной цифровой вычислительной нашины, содержащее два входных регистра, в которые заносятся старшие и младшие разряды аргумента, блок памяти, два регистра слагаемых, мультиплексор, сумматор и блок управления. По внешнему сигналу производится запись аргумента во входные регистры. Из блока памяти извлекается значение функции, соответствующее старшим разрядам входного кода и заносится в первый регистр слагаемых. Затем блок управления увеличивает адрес блока памяти на единицу и его содержимое заносится во второй регистр хранения интерполируемой функции. Процесс линейной интерполяции осуществляется путем подачи через мультиплексор на вход накапливающего сумматора содержимого первого и второго регистров слагаемых, т.е. значения функции в начале и в конце интерполируемого интервала. Входной регистр младших разрядов является сдвиговым. При сдвигании кода вправо на выходе младшего разряда регистра появляется последовательный код. Он используется для управле ния мультиплексором 2 . Недостатком известного устройства является то, что применение кусочнолинейной интерполяции в устройстве при жестких требованиях к точности приводит к резкому увеличению объема блока памяти для хранения узлов интерполяции. Целью изобретения является сокращение аппаратурных затрат за счет снижения емкости блока памяти. Поставленная цель достигается тем что цифровое устройство для вычисления синусно-косинусных зависимостей, содержащее сдвиговый регистр младших разрядов аргумента, регистр старших разрядов аргумента, блок памяти, первый и второй регистры слагаемых, мультиплексор, сумматор и блок управ ления, выходы с первого по четвертый которого соединены с управляющими входами соответственно блока памяти, мультиплексора и входами записи первого и второго регистров слагаемых, пятый выход блока управления соедине с входом сдвига сдвигового регистра младших разрядов аргумента, выход и вход записи которого соединены соо ветственно с первым входом блока управления и шестым выходом блока управления, подключенным к входу записи регистра старших разрядо.в аргумен та, выход которого соединен с адресным входом блока памяти, информацион ные входы сдвигового регистра младших и регистра старших разрядов аргу мента соединены с входом аргумента устройства, содержит регистр узловых значений и блок введения коэффициента, управляющий вход которого соединен с седьмым выходом блока управления, восьмой выход и второй и третий входы которого соединены соответственно с входом записи регистра узловых значений, тактовым входом и входом разрешения записи устройства, девятый выход блока управления соединен с выходом конца преобразования устройства, информационные входы с первого по третий мультиплексора соединены соответственно с выходом блока памяти, выходом сумматора и первым выходом блока введения коэффициента, второй выход и информационный вход которого соединены соответственно с входом перенЬса и выходом сумматора, первый и второй входы слагаемых которого соединены с выходами соответственно первого и второго регистров слагаемых, информационные входы которых подключены к выходу регистра узловых значений, информационный вход которого соединен с выходом мультиплексора и выходом устройства, причем блок управления содержит три элемента ИЛИ-НЕ, элемент НЕ, три элемента И-НЕ, элемент И, три триггера, счетчик и узел памяти, первый выход которого соединен с первым входом элемента И, выход которого соединен со счетным входом счетчика, выход которого соединен с первым входом узла памяти, вход обнуления счетчика соединен с третьим входом блока управления, первыми входами первых элементов ИЛИ-НЕ и И-НЕ и через элемент НЕ соединен с входом установки в ноль первого триггера, инверсный выход которого соединен с информационным входом первого триггера и -первым входом второго элемента ИЛИ-НЕ, выход которого соединен с вторым входом элемента И и вторым входом узла памяти, третий и четвертый входы которого соединены соответственно с выходом третьего элемента ИЛИ-НЕ и старшим разрядом первого входа блока управления, остальные разряды которого соединены с входами третьего элемента ИЛИ-НЕ, вторые входы первых элементов ИЛИ-НЕ и И-НЕ соединены с BTopbiM входом блока управления и первым входом второго элемента И-НЕ, выход которого соединен с вторым входом второго элемента ИЛИ-НЕ и тактовым входом первого триггера, вход установки в единицу которого соединен с вторым выходом узла памяти, третий выход которого соединен с входами установки в ноль второго и третьего триггеров, входы установки в единицу которых соединены с выодами соответственно первого и третьего элементов И-НЕ, выходы первого элемента ИЛИ-НЕ и второго триггера соединены с входами третьего лемента И-НЕ, выход третьего триггеа соединен с вторым входом второго элемента И-НЕ, выходы с первого по девятый блока управления соединены соответственно с инверсным выходом младшего разряда счетчика, четвертым .пятым, шестым и седьмым выходами узла памяти, выходом разрядов счетчика, выходом второго элемента ИЛИ-Н и третьим выходом узла памяти. Блок введения коэффициента содержит сумматор, сдвигатель и узел коррекции, причем информационный вход, блока соединен с информационным входом сдвигателя и входом первого слагаемого сумматора, вход второго слагаемого которого соединен с выходом сдвигателя и входом узла коррекции, выход которого соединен с входом переноса сумматора и вторым выходом блока, управляющий вход ипевый выход которого соединены соответственно с управляющим входом сдвигателя и выходом сумматора. На фиг. 1 представлена блок-схема на фиг. 2 и 3 - варианты выполнения соответственно блока введения коэффициента и блока управления. Цифровое устройство для вычисления синусно-косинусных зависимостей содержит сдвиговьш регистр 1 младших разрядов аргумента, регистр 2 старши разрядов аргумента, блок 3 памяти, мультиплексор 4, регистр 5 узловых значений, первый.и второй регистры 6 и 7 слагаемых, сумматор 8, блок 9 введения коэффициента и блок 10 управления. Блок введения коэффициента содержит сумматор 11, узел 12 коррекции и сдвигатель 13. Блок управления содержит элементы 14-16, элемент НЕ 17, элементы И-НЕ 18-20, элемент И 21, триггеры 22-24, счетчик 25 и узел 26 памяти. Цифровое устройство для вычисления синусно-косинусных зависимостей работает следующим образом. На входы 27 и 28 блока 10 управления поступают сигналы тактового генератор и сигнал записи кода аргумента. В ре зультате этого блок 10 управления формирует выходные сигналы управления, а именно: выход 29 формирует сигнал, осуществляющий запись в регистрах 1 и 2 младших и старших разрядов аргумента, выход 30 - сдвиг влево содержимого регистра 1 младших разрядов аргумента, выход 31 - прибавление единицы к адресу блока 3 памяти, выход 32 - управление состоянием мультиплексора 4, выход 33 запись данных с мультиплексора 4 в регистр 5 узловых значений, выход 34 - запись в регистре 7 слагаемых, значений интерполируемой функции конца интервала интерполяции, выход 3 - запись в регистре 6 слагаемых значений интерполируемой функции начала интервала интерполяции, выход 36 задает коэффициент передачи блока введениякоэффициента 9. Многоразрядный код аргумента, поступающий на вход 37 регистра 1 младших и вход 38 регистра 2 старших разрядов аргумента, по сигналу записи с блока 10 управления записывается в регистр 1 младших и регистр 2 старших разрядов аргумента. После этого блок 10 управления устанавливается в исходное состояние. Из блока 3 памяти выбирается содержимое по адресу, записанному в регистре 2 старших разрядов аргумента и через мультиплексор 4 по сигналу, поступающему из выхода 33 блока 10 управления, заносится в регистр 5 узловых значений. Затем блок 10 управления формирует сигнал прибавления единицы к адресу блока 3 памяти, из которого извлекается содержимое, соответствующее значению функции в конце интервала интерполяции, и помещается в регистре 5 узловых значений. Так как сигналы управления регистром 5 узловых значений и сигналы управления регистрами 6 и 7 слагаемых противофазны, то сначала происходит запись в регистр 6 или 7 слагаемых, т.е. прежнее содержимое регистра 5 узловых значений заносится в регистр 6 слагаемых, а затем через такт новое содержимое - в регистр 7 слагаемых. Далее формируется сигнал, поступающий с выхода 32 блока 10 управления на мультиплексор 4. Мультиплексор 4 переключается так, что выход блока 9 введения коэффициента поступает на информационный вход регистра 5 узловых значений. На входы сумматора 8 из регистров 6 и 7 слагаемых поступают сигналы, соответствующие значениям функции начала и конца интервала интерполяции. За чет монтажного сдвига из сумматора 8 снимается сигнал, соответствующий полусумме значения функции в начале и в конце интервала интерполяции, а на выходе блока введения коэффициента 9 - значение функции, соответствующее середине интервала интерполяции. Это достигается тем, что на выходе 36 блока 10 управления формируется требуемый коэффициент передачи. Если в регистре 1 младших разрядов аргумента старший разряд равен 1, а остальные О, то на этом блок 10 управления прекращает свою работу и на выходе мультиплексора 4 формируется го товый результат работы устройства в виде многоразрядного кода. При этом с выхода 39 блока 10 управления поступает сигнал о конце преобразования. Следует отметить, что при запис в регистр 1 младших разрядов аргумен та всех нулей сигнал о конце преобра з.ования формируется при появлении на выходе мультиплексора 4 значения функции начала интерполяции. На выходе 30 блока 10 управления формируется сигнал сдвига, старший разряд выталкивается из регистр 1 младших разрядов аргумента, а на место младшего разряда записывается 0. Вычисленное ранее значение функци в середине начального интервала запи сано в регистр 6 или 7 слагаемых. Та если после сдвига старший разряд регистра 1 младших разрядов аргумента равен 1, то Еи 1числение значения функции заносится в регистр 6 слагаемых в качестве значения фукнции начала нового интервала интерполяции. Если старший разряд регистра 1 младших разрядов аргумента равен О, то обнов ляется значение функции в конце интервала, т.е. производится запись в .регистр 7 слагаемых. После каждой итерации интервал уменьшается вдвое. Коэффициент передачи блока 9 введения коэффиц 1ента при уменьшении интервала стремится к 1. Поэтому после определенного числа шагов можно перейти на линейную интерполяцию, совершая при этом ошибку меньше допустимой. С выхода 32 блока 10 управления вьщается новое значение сигнала управления, при котором сигнал с выхода сумматора 8 через вход 40 мультиплексора 4 подается на вход регист ра 5 узловых значений. Это позволяет для последующих шагов ограничиться линейной интерполяцией. Благодаря этому можно сократить длительность такта и повысить быстродействие устройства. Блок 10 управления представляет соб.ой автомат, устанавливаемый в исходное состояние внешним сигналом записи аргумента. Внутреннее состояние и состояние выходов 31, 32, 30, 29 и 33 блока 10 управления определяется числом импульсов сигнала, поступающего с тактового генератора (на схеме не показан) на вход 32 этого блока. Состояние выходов 35 и ЗД блока 10 управления определяется как внутренним состоянием его, так и содержанием старшего разряда регистра 1 младших разрядов аргумента. Остановимся более подробно на реализации блока 9 введения коэффициента. При вычислении функции sinx, cpsx коэффициент передачи блока должен быт1 Д1 равен sec -j- , Выходной код сумматора 8 поступает на вход 41 сумматора 11 (фиг. 2), а на вход 42 его - через сдвигатель 12. Выход.36 блока 10 управления задает код сдвига. При хранении узлов интерполяции в блоке 3 памяти с шагом по аргументу АО 2 и точности вычислений, например 27-28 двоичных разрядов, с.двигатель 13 должен иметь пятнадцать информационных выходов (входов) и обеспечить только восемь двухразрядных сдвигов. Так как каждый сдвиг производится на два разряда, то комбинационный 15-входовый сдвигатель 13 на восемь состояний можно заменить двумя сдвигателями (с четными и нечетными входами) соответственно с восемью и семью входами. В свою очередь, такой сдвигатель может быть реализован на программируемой логической матрице (ПЛМ), позволяющей использовать восемь выходных функций обтцим объемом 48 конъюнкций 16-вход11ьгх переменных. Заметим, что комбинашюнный сдвигатель требует ПЛМ объемом 36 конъюнкций 11 переменных. Избыточность в ПЛМ числа конъюнкций и резерв в 7-входовом сдвигателе одной выходной функции позволяют сформировать сигнал коррекции с выхода блока 9 введения коэффициента на входы пергносов сумматора 11 блока 9 и сумматора 8 устройства. Благодаря этому в одной из вух ПЛМ помимо сдвигателя можно разестить также комбинационный узел

12 коррекции. Сигнал коррекции повышает точность при работе на самом большом интервале интерполяции Ь. и функционально является блоком хра

5 И нения константы вида - -Гтрг

Применение в качестве 9 сумматора 11 со сдвигателем 13 основано на разложении в ряд

1

- 8

1 +

- %

128

При этом на вход 41 сумматора 11 юступает выходной код сумматора 8, на второй вход - со сдвигом, определи-. емым множителем , а на входы переноса сумматоров 8 и 11 - сигнал коррекции с выходов блоков 12 и 9 (однобитовое приближение выражения 20 5. Ь1) .

3 Не/

Использование изобретения позволит при существующем уровне технологии

получать на одном кристалле вычислители с точностью вычислений 2А-32 двоичных разрядов.

Применение блока введения коэффициента даже простейшего типа (сумматор и комбинационный сдвигатель) позволяет при вычислении значений с точностью 29 двоичных разрядов сократить объем блока памяти более чем в ЮОраг по сравнению с объемом блока памяти базового объекта.

Важным достоинством предлагаемого . устройства является применение интерполяции старшими разрядами, что позволяет прекратить вычисление при нулевых оставшихся младших разрядах в регистре младших разрядов и получить при выполнении только части итераций точный результат. Это существенно отличает данное устройство от устройств, реализующих алгоритм Волдера, имеющих низкое быстродействие при больших затратах аппаратуры.

V

л

л

/z

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Специализированный процессор | 1977 |

|

SU723581A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ВСЕСОЮ8ЫЛЯ f пши^ш-т;';'':;;^' :::•:: | 0 |

|

SU363973A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1983-01-31—Подача