Изобретение относится к области вычислительной техники и может быть использовано к сверхбольших интегральных схемах (СБИС) в качестве элементной базы устройств каскадной логики к конвейерной обработки данных, в частности при реализации арифметических и логических устройств.

Известна реализация логических цифровых устройств на основе каскадных динамических схем типа "домино" (Патент США N 4780626, H 03 K 19/096. НКИ - 307 - 448 от 25.10.1988). Они требуют меньших затрат по числу транзисторов на одну функцию по сравнению с традиционными статическими КМДП элементами. Их недостаток - отсутствие возможности фиксации состояния на выходе каскада и ограниченное быстродействие. Последнее обусловлено тем, что перезаряд нагрузки осуществляется через логическую часть, т.е. через несколько последовательно включенных транзисторов. Это приводит к зависимости быстродействия как от величины нагрузки, так и от глубины логики, что существенно усложняет работу каскадов под общей синхронизацией.

Наиболее близким техническим решением к предлагаемому является многокаскадное логическое устройство, предназначенное для выполнения логических операций над несколькими переменными с использованием однофазных входных и выходных сигналов при одновременном тактировании всех каскадов (Патент США N 4668880, H 03 K 19/096. НКИ 307-469 от 26.05.87, фиг. 3).

Это устройство, принятое за прототип, содержит последовательно соединенные каскады логики, каждый из которых состоит из тактируемого КМДП инвертора, во внутреннюю цепь которого включен логический блок, состоящий из комбинационных цепей И/ИЛИ, выполненный на транзисторах n-типа.

Недостаток этого устройства - функциональная ограниченность. Это обусловлено, во-первых, отсутствием запоминания или фиксации логического состояния в самом каскаде в процессе его работы, что ограничивает число последовательно включенных каскадов, работающих под общей синхронизацией. Во-вторых, логический блок каждого каскада вследствие использования только однофазных входных сигналов реализует лишь элементарные логические функции И/ИЛИ. Более сложные логические и арифметические операции на уровне каскада логики не могут выполняться из-за отсутствия дополняющих парафазных сигналов. Для их получения необходимы дополнительные элементы, а для их использования и реализации более сложных функций с фиксацией результатов требуются дополнительные каскады логики, синхросигналы и связанные с ними временные затраты.

Технической задачей, решаемой в изобретении, является расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что каскадное логическое устройство на КМДП транзисторах, содержащее в каждом каскаде первый инвертор, первый транзистор p-типа и логический блок, содержащий прямые ключевые цепи, которые включены между прямым выходом логического блока и его общим выводом, причем каждая прямая ключевая цепь состоит из последовательно соединенных транзисторов n-типа, затворы которых являются одними из входов каскада, прямой выход логического блока подключен к шине питания через первый транзистор p-типа и соединен со входом первого инвертора, выход которого подключен к одному из входов последующего каскада, общий вывод логического блока первого каскада подключен к шине земли через тактовый транзистор n-типа, затвор которого соединен с затворами первых транзисторов p-типа всех каскадов и подключен к тактовой шине, а выход первого инвертора последнего каскада является первым выходом устройства, дополнительно содержит в каждом каскаде второй инвертор, второй транзистор p-типа и триггер-фиксатор, в первом каскаде - первый и второй дополнительные транзисторы p-типа, а в остальных каскадах - третий, четвертый, пятый и шестой транзисторы p-типа, каждый каскад дополнительно имеет парафазные входы, а логический блок в каждом каскаде содержит также инверсные ключевые цепи, которые включены между инверсным выходом логического блока и его общим выводом, и прямые и инверсные дополнительные ключевые цепи, которые подключены с одной стороны соответственно к прямому и инверсному дополнительным выходам логического блока, а с другой - к общему выводу логического блока в первом каскаде и к шине земли - во всех других каскадах, инверсные ключевые цепи и дополнительные ключевые цепи во всех каскадах выполнены из последовательно соединенных транзисторов n-типа, затворы которых подключены к входам и соответствующим парафазным входам каскада, инверсный выход логического блока подключен к шине питания через второй транзистор p-типа и соединен с входом второго инвертора, прямой дополнительный выход логического блока подключен к шине питания в первом каскаде через первый дополнительный транзистор p-типа, а в других каскадах - через последовательно включенные третий и пятый транзисторы p-типа, инверсный дополнительный выход логического блока подключен к шине питания в первом каскаде через второй дополнительный транзистор p-типа, а в других каскадах - через последовательно включенные четвертый и шестой транзисторы p-типа, затворы второго транзистора p-типа в каждом каскаде, а также дополнительных транзисторов p-типа подключены к тактовой шине, а общие выводы логических блоков объединены, выход первого инвертора подключен к затворам третьего и четвертого транзисторов p-типа и к первому входу последующего каскада, а выход второго инвертора - к затворам пятого и шестого транзисторов p-типа и к первому парафазному входу последующего каскада, причем первые входы указанных каскадов подключены к затворам тех транзисторов n-типа в прямых и инверсных ключевых цепях, истоки которых непосредственно соединены с общим выводом логического блока и с затворами тех транзисторов n-типа в дополнительных ключевых цепях, истоки которых соединены с шиной земли, дополнительные выходы логического блока подключены к парафазным входам триггера-фиксатора, выходы которого являются выходами каскада, а выход второго инвертора последнего каскада является вторым выходом устройства, прямой и инверсный выходы логического блока последнего каскада подключены к парафазным входам дополнительного триггера фиксатора, идентичного основному, выходы которого являются дополнительными выходами устройства.

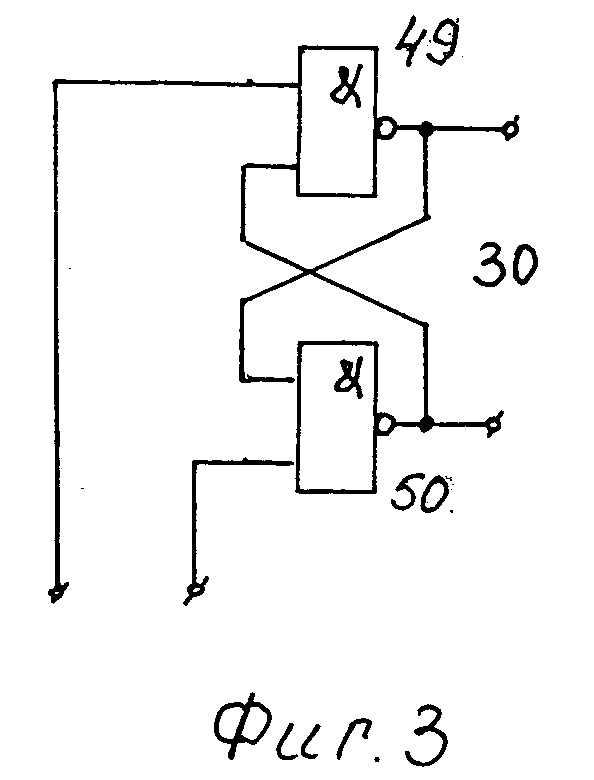

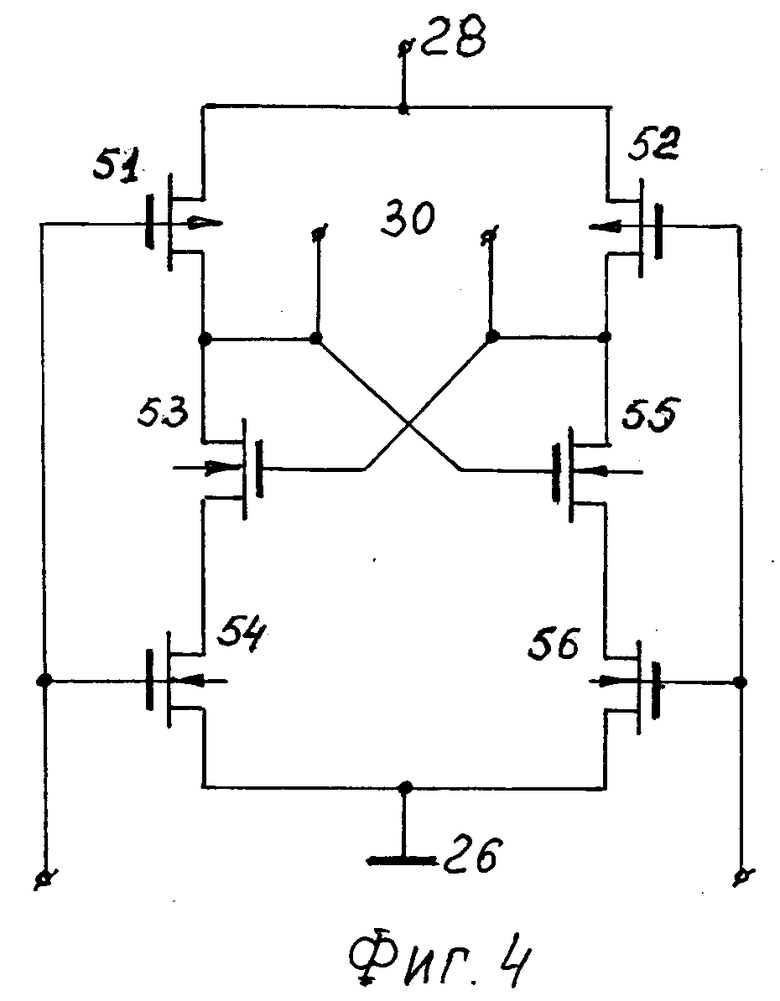

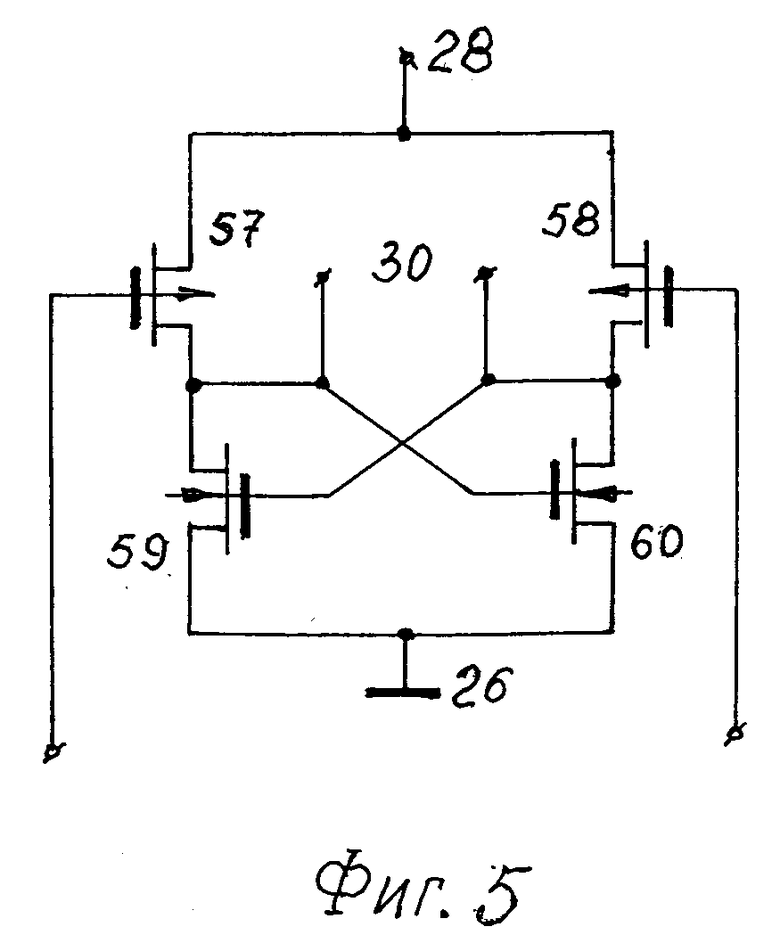

При этом триггер-фиксатор выполнен либо на двух элементах 2И-НЕ, которые включены между шиной питания и шиной земли, первые входы которых являются входами обратной связи и одновременно выходами триггера-фиксатора, а вторые входы являются парафазными входами триггера-фиксатора, либо выполнен из двух цепей, включенных между шиной питания и шиной земли, каждая из которых содержит последовательно включенные транзистор p-типа и два транзистора n-типа, причем в каждой цепи затвор транзистора p-типа и затвор транзистора n-типа, исток которого подключен к шине земли, объединены и являются парафазными входами триггера-фиксатора, а затворы вторых транзисторов n-типа в каждой из цепей соединены с общей точкой транзисторов p- и n-типов другой цепи и являются одновременно выходами триггера-фиксатора, либо выполнен из двух цепей, включенных между шиной питания и шиной земли, каждая из которых содержит транзистор p-типа и транзистор n-типа, причем затворы транзисторов p-типа являются парафазными входами триггера-фиксатора, а затворы транзисторов n-типа, истоки которых подключены к шине земли, в каждой из цепей соединены с общей точкой транзисторов другой цепи, и являются одновременно выходами триггера- фиксатора.

Существенными отличительными признаками в указанной совокупности признаков является использование парафазных входов каскада, введение в логический блок инверсных ключевых цепей, а также дополнительных ключевых цепей, введение в каскад второго инвертора, триггера-фиксатора и новых транзисторов p-типа в сочетании с особенностями выполнения логического блока и связей между каскадами.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - расширение функциональных возможностей устройства. Действительно, использование и формирование в самом устройстве парафазных сигналов благодаря наличию новых признаков значительно расширяет комбинационные возможности на уровне каскада и устройства в целом и позволяет выполнять более сложные функции, которые требуют как прямых, так и дополнительных логических сигналов, причем без увеличения числа каскадов, т.е. без потери быстродействия. Парафазные выходы логического блока позволяют естественным образом, асинхронно без дополнительной синхронизации включить в каскад триггер-фиксатор для запоминания результата в данном каскаде, причем в каждом каскаде реализуются одновременно две функции: одна промежуточная на дополнительных ключевых цепях и вторая передаточная на прямых и инверсных ключевых цепях. Каскады работают последовательно в асинхронном режиме в течение одного такта и дополнительный триггер-фиксатор запоминает состояние выхода устройства на время такта. Причем токи перезаряда в дополнительных цепях текут на шину земли, минуя тактовый транзистор, который работает один на все каскады. Выполнение логического блока и связей между каскадами, блокирование проводимости ключевых цепей путем запирания транзисторов, подключенных к выходам инверторов, позволяет уменьшить число и размеры транзисторов и за счет этого реализовать дополнительные функции.

Выполнение триггера-фиксатора (п. 2-4 формулы) обеспечивает сохранение состояния триггера при наличии двух логических "1" на его парафазных входах в режиме хранения и его переключение при появлении парафазного входного сигнала.

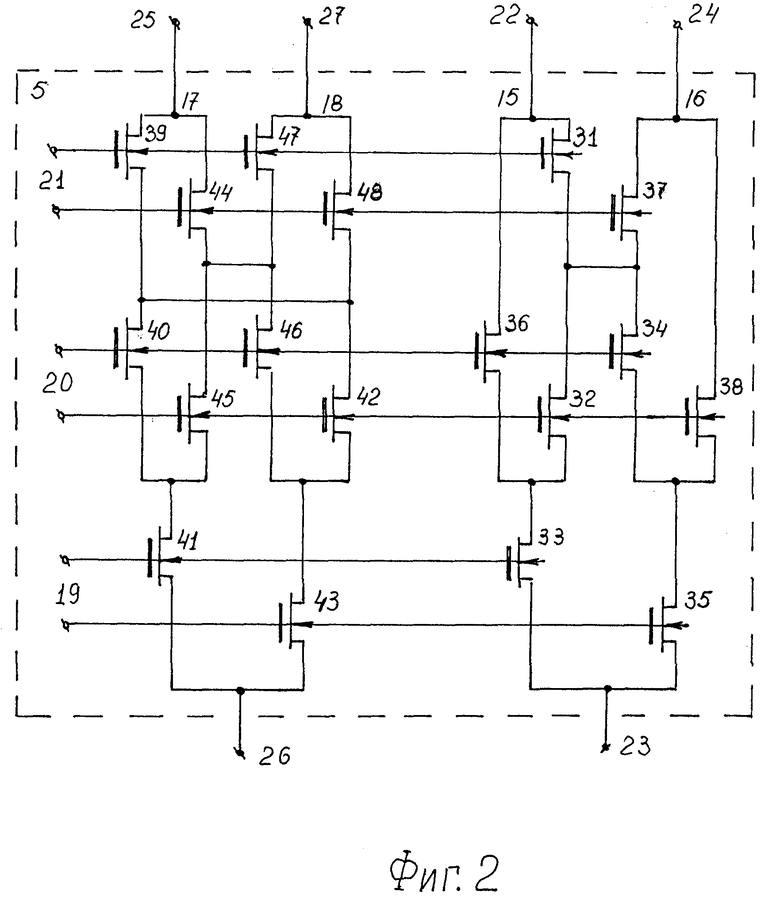

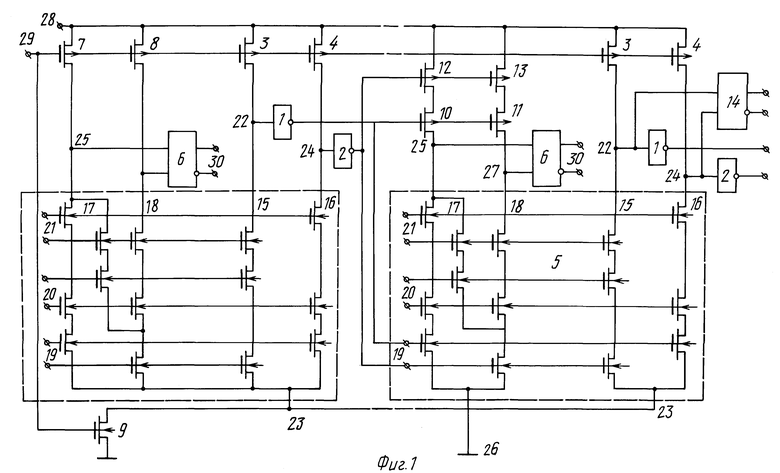

На фиг. 1 приведена принципиальная схема каскадного логического устройства на КМДП транзисторах, представленного в виде первого и последнего каскадов, на фиг. 2 приведен пример реализации логического блока каскада, представляющего собой разряд многоразрядного сумматора, на фиг. 3-5 даны принципиальные схемы вариантов триггера-фиксатора.

Каскадное логическое устройство на КМДП транзисторах содержит в каждом каскаде (фиг. 1) первый 1 и второй 2 инверторы, первый 3 и второй 4 транзисторы p-типа, логический блок 5, триггер-фиксатор 6. Первый каскад содержит, кроме того, первый 7 и второй 8 дополнительные транзисторы p-типа и тактовый транзистор 9 n-типа. Все другие каскады, кроме первого, содержат третий 10, четвертый 11, пятый 12 и шестой 13 транзисторы p-типа. В последнем каскаде, кроме того, есть дополнительный триггер-фиксатор 14.

Логический блок 5 каждого каскада содержит прямые 15 и инверсные 16 ключевые цепи, прямые дополнительные 17 и инверсные дополнительные 18 ключевые цепи. Ключевые цепи 15-18 состоят из последовательно соединенных транзисторов n-типа, затворы которых подключены к входам 19-21 каскада, число пар которых равно числу логических переменных.

Прямые ключевые цепи 15 включены между прямым выходом 22 логического блока 5 и его общим выводом 23, а инверсные ключевые цепи 16 включены между инверсным выходом 24 логического блока 5 и его общим выводом 23.

Прямые дополнительные ключевые цепи 17 включены между прямым дополнительным выходом 25 логического блока 5 и общим выводом 23 логического блока 5 в первом каскаде или шиной земли 26 в других каскадах. Инверсные дополнительные ключевые цепи 18 включены между инверсным дополнительным выходом 27 логического блока 5 и общим выводом 23 логического блока в первом каскаде или шиной земли 26 в других каскадах.

Первый транзистор 3 p-типа включен между прямым выходом 22 логического блока 5 и шиной питания 28, а второй транзистор 4 p-типа включен между инверсным выходом 24 логического блока 5 и шиной питания 28. В первом каскаде первый дополнительный транзистор 7 p-типа включен между прямым дополнительным выходом 25 логического блока 5 и шиной питания 28, а второй дополнительный транзистор 8 p-типа включен между инверсным дополнительным выходом 27 логического блока 5 и шиной питания 28. Во всех других каскадах прямой дополнительный выход 25 логического блока 5 подключен к шине питания 28 через последовательно соединенные третий 10 и пятый 12 транзисторы p-типа, а инверсный дополнительный выход 27 логического блока 5 подключен к шине питания 28 через последовательно соединенные четвертый 11 и шестой 13 транзисторы p-типа.

Затворы первых 3, 7 и вторых 4, 8 транзисторов p-типа объединены и подключены к тактовой шине 29, к которой подключен также затвор тактового транзистора 9 n-типа, который включен между объединенными общими выводами 23 логических блоков 5 всех каскадов и шиной земли 26.

К прямому 22 и инверсному 24 выходам логического блока 5 подключены входы соответственно первого 1 и второго 2 инверторов. Прямой 25 и инверсный 27 дополнительные выходы логического блока 5 подключены к парафазным входам триггера-фиксатора 6, выходы которого являются выходами 30 каскада. Выходы первого и второго инверторов последнего каскада являются первым и вторым выходами устройства, а входы тех же инверторов подключены к парафазным входам дополнительного триггера-фиксатора 14, выходы которого являются дополнительными выходами устройства.

Выход первого инвертора 1 подключен к затворам третьего 10, четвертого 11 транзисторов p-типа и к первому 19 входу последующего каскада, а выход второго инвертора 2 подключен к затворам пятого 12, шестого 13 транзисторов p-типа и к первому 19 парафазному входу последующего каскада. Причем в ключевых цепях истоки транзисторов n-типа, затворы которых подключены к первым входам каскада, соединены с шиной земли 26 непосредственно или через тактовый транзистор 9 n-типа.

Логический блок 5 каскада, представляющего собой один разряд многоразрядного сумматора (фиг. 2), выполнен на восемнадцати транзисторах n-типа 31-38. На дополнительных ключевых цепях 17 и 18 реализуется функция суммы, на ключевых цепях 15 и 16 реализуются функция переноса.

Все ключевые цепи строятся на основе правил комбинационных цепей ключевого типа - проводящему состоянию цепи соответствует логический "0" на выходе логического блока и, соответственно, логическая "1" на выходе инвертора и непроводящему состоянию цепи - наоборот. По таблице истинности для каждой функции и для каждого набора логических сигналов на входах каскада строится ключевая цепь из проводящих транзисторов - прямая, если значение функции равно "1", и инверсная, если значение функции равно "0". Проводящему состоянию транзистора n-типа соответствует наличие логической "1" на том входе каскада, к которому подключен затвор данного транзистора. В соответствии с числом состояний от трех переменных логический блок 5 должен содержать по четыре ключевых цепи каждого типа. Причем каждая цепь, в общем случае, состоит из трех транзисторов, а при наличии только двух значимых переменных (от логического состояния на третьем входе значение функции не зависит) число транзисторов в цепи уменьшается. Таким образом, в состав прямых ключевых цепей 15 входят цепи: первая - транзисторы первый 31, второй 32 и третий 33, вторая - транзисторы первый 31, четвертый 34 и пятый 35, третья и четвертая - транзисторы шестой 36 и третий 33. В состав инверсных ключевых цепей 16 входят следующие цепи: пятая - транзисторы седьмой 37, четвертый 34 и пятый 35, шестая - транзисторы седьмой 37, второй 32 и третий 33, седьмая и восьмая - транзисторы восьмой 38 и пятый 35.

В состав прямых дополнительных ключевых цепей 17 входят следующие цепи: первая - транзисторы девятый 39, десятый 40 и одиннадцатый 41, вторая - транзисторы девятый 39, двенадцатый 42 и тринадцатый 43, третья - транзисторы четырнадцатый 44 , пятнадцатый 45 и одиннадцатый 41, четвертая - транзисторы четырнадцатый 44, шестнадцатый 46 и тринадцатый 43. В состав инверсных дополнительных ключевых цепей 18 входят цепи: пятая - транзисторы семнадцатый 47, шестнадцатый 46 и тринадцатый 43, шестая - транзисторы семнадцатый 47, пятнадцатый 45 и одиннадцатый 41, седьмая - транзисторы восемнадцатый 48, двенадцатый 42 и тринадцатый 43, восьмая - транзисторы восемнадцатый 48, десятый 40 и одиннадцатый 41.

Соответственно, затворы одиннадцатого 41 и третьего 33 транзисторов подключены к первому входу 19 каскада, затворы тринадцатого 43 и пятого 35 подключены к первому парафазному входу каскада. Затворы десятого 40, шестнадцатого 46, шестого 36 и четвертого 34 транзисторов подключены ко второму входу 20 каскада, а затворы пятнадцатого 45, двенадцатого 42, второго 32 и восьмого 38 транзисторов подключены ко второму парафазному входу каскада. Затворы девятого 39, семнадцатого 47 и первого 31 транзисторов подключены к третьему входу 21 каскада, а затворы четырнадцатого 44, восемнадцатого 48 и седьмого 37 транзисторов подключены к третьему парафазному входу каскада.

При выполнении триггера-фиксатора (фиг. 3) на двух элементах 2И-НЕ - 49, 50 первые входы элементов являются входами обратной связи и одновременно выходами 30 триггера-фиксатора, а вторые входы являются парафазными входами триггера-фиксатора.

Упрощенный вариант выполнения триггера-фиксатора (фиг. 4) состоит из двух цепей, включенных между шиной питания 28 и шиной земли 26. Каждая цепь содержит последовательно включенные транзистор p-типа 51 или 52 и по два транзистора n-типа 53, 54 и 55, 56. В каждой цепи затвор транзистора p-типа и затвор транзистора n-типа, исток которого подключен к шине земли 26, объединены и являются парафазными входами триггера-фиксатора. Затвор другого транзистора n-типа в каждой из цепей соединен с общей точкой транзисторов p- и n-типов другой цепи. Общие точки указанных транзисторов являются выходами 30 триггера-фиксатора.

Триггер-фиксатор (фиг. 5) содержит две цепи, каждая из которых состоит из транзистора p-типа 57 или 58 и транзистора n-типа 59 или 60. Транзисторы разного типа включены последовательно между шиной питания 28 и шиной земли 26. Затворы транзисторов p-типа являются парафазными входами триггера-фиксатора. Затворы транзисторов n-типа в каждой цепи соединены с общей точкой транзисторов другой цепи и являются одновременно выходами 30 триггера-фиксатора.

Устройство работает следующим образом. В исходном состоянии при отсутствии сигнала на тактовой шине 29 происходит процесс предзаряда узловых емкостей всех выходов 22, 24 и 25, 27 логических блоков 5. Поскольку тактовый транзистор 9 n-типа закрыт, а дополнительные транзисторы 7 и 8 и первые 3 и вторые 4 транзисторы p-типа открыты, узловые емкости прямого 22 и инверсного 24 выходов логического блока заряжаются до уровня логической "1". На выходах первого 1 и второго 2 инверторов формируются логические "0". Этими сигналами запираются транзисторы n-типа, затворы которых подключены к первым входам 19 последующего каскада, и отпираются третий, четвертый, пятый и шестой транзисторы 10-13 p-типа. Поэтому дополнительные выходы 25 и 27 логического блока 5 также принимают уровни логической "1". Триггеры-фиксаторы 6 и 14 находятся при этом в режиме хранения, поскольку наличие двух логических "1" на парафазных входах не ведет к их переключению. На свободные входы 20 и 21 каскадов (а также на первый вход 19 первого каскада) от внешних устройств подаются наборы сигналов, которые удерживаются все время, пока на тактовой шине 29 действует тактовый сигнал высокого уровня.

После подачи тактового сигнала на шину 29 происходит последовательное срабатывание каскадов, которое заключается в появлении значимых парафазных сигналов на выходах первого 1 и второго 2 инверторов. Первые 3 и вторые 4, а также дополнительные 7, 8 транзисторы p-типа закрываются, а тактовый транзистор 9 отпирается. При любом наборе сигналов на входах 19-21 первого каскада среди прямых 15 или инверсных 16 ключевых цепей в логическом блоке 5 первого каскада существует одна проводящая ключевая цепь 15. Узловая емкость прямого выхода 22 логического блока 5 через данную цепь из открытых транзисторов n-типа и тактовый транзистор 9 n-типа разряжается на шину земли 26. Тоже происходит, например, с прямым дополнительным выходом 25 логическою блока 5 в первом каскаде. На парафазные входы триггера-фиксатора 6 поступает парафазный сигнал (0, 1) и происходит установка триггера-фиксатора. Первый элемент 2И-НЕ 49 закрывается, а транзисторы p-типа 51, 57 отпираются. После срабатывания цепей обратной связи на выходах 30 триггера-фиксатора устанавливается парафазный сигнал (1, 0), соответствующий функции, реализованной на дополнительных ключевых цепях 17, 18 логического блока 5 первого каскада. Этот результат будет храниться в триггере-фиксаторе в течение такта.

При появлении на выходе первого инвертора 1 в первом каскаде логической "1" запираются цепи предзаряда в следующем каскаде, состоящие из транзисторов 10 и 11 p-типа. Одновременно возникает путь для тока в одной из дополнительных ключевых цепей 15 или 16, поскольку на первом входе 19 этого каскада сформировалась логическая "1". Допустим, в соответствии с набором сигналов на входах 20, 21 каскада в проводящем состоянии оказываются инверсная ключевая цепь 16 и прямая дополнительная ключевая цепь 17 в логическом блоке 5 второго представленного на фиг.1 каскада. Узловая емкость прямого дополнительного выхода 25 логического блока 5 разряжается через транзисторы n-типа непосредственно на шину земли, минуя тактовый транзистор 9 n-типа. Для каскада на три входа отсутствие четвертого транзистора (тактового) в цепи разряда ведет к повышению эффективности логической части на 25%.

Как и в первом каскаде происходит установка триггера-фиксатора 6. Разряд узловой емкости инверсного выхода 24 логического блока 5 второго каскада происходит через инверсную ключевую цепь 16 и тактовый транзистор 9 n-типа. Таким образом, для работы многокаскадного устройства требуется всего один тактовый транзистор. На выходах дополнительного триггера-фиксатора 14 формируется результат, который возникает в процессе взаимной работы уже двух каскадов и который хранится также в течение всего такта. Первый и второй выходы устройства могут быть использованы для передачи данных в другое устройство, работающее в синхронном режиме.

После окончания действия тактового сигнала первые 3 и 7 и вторые 4 и 8 транзисторы p-типа открываются, а тактовый транзистор 9 n-типа запирается. Происходит восстановление уровней логической "1" на узловых емкостях всех выходов логических блоков 5 каскадов. Причем сначала восстанавливается уровень логической "1" на прямом выходе 22 логического блока 5 предыдущего каскада, а затем происходит отпирание третьего 10 и четвертого 11 транзисторов p-типа с одновременным запиранием соответствующих транзисторов n-типа в прямой ключевой цепи 17. Наличие двух транзисторов p-типа в цепи предзаряда обусловлено тем, что при общих транзисторах n-типа в прямых и инверсных ключевых цепях в логическом блоке как первый 1, так и второй 2 инверторы предыдущего каскада должны обеспечить блокирование цепи предзаряда к любому дополнительному выходу логического блока. Использование же таких транзисторов ведет к значительному сокращению числа транзисторов n-типа в ключевых цепях.

Так, например, функция суммирования реализуется на 10 транзисторах n-типа (фиг.2). При независимом выполнении прямых и инверсных ключевых цепей потребовалось бы для восьми цепей по три транзистора - в сумме 24 транзистора n-типа. Поэтому для расширения функциональных возможностей так важно минимизировать число транзисторов, необходимых для реализации сложной функции с помощью указанных взаимосвязанных конструктивных признаков.

Рассмотрим работу логического устройства в качестве двухразрядного сумматора. Логические блоки в каждом каскаде одинаковые и соответствуют фиг.2. Допустим в первом разряде суммируются три переменных - (1, 1 и 0) и на входы 19-21 каскада поданы соответствующие парафазные сигналы. (На верхнюю клемму входа 21 каскада поступает единичный сигнал, на нижнюю - нулевой сигнал и т. д. ). Среди ключевых цепей 15 и 16 проводящей оказывается вторая прямая - транзисторы первый 31, четвертый 34 и пятый 35 Среди дополнительных ключевых цепей 17 и 18 проводящей оказывается пятая инверсная - транзисторы семнадцатый 47, шестнадцатый 46 и тринадцатый 43.

В результате на выходе первого инвертора 1 формируется логическая "1", что свидетельствует о том, что функция переноса в первом разряде равна "1". С инверсного дополнительного выхода 27 логического блока 5 сигнал логического "0" устанавливает триггер-фиксатор 6 в "0", что соответствует функции суммы, равной "0".

Допустим во втором каскаде суммируются переменные (0, 0) и соответствующие сигналы поданы на входы 21 и 20 этого каскада. На вход 19 каскада с предыдущего каскада поступает перенос, равный "1". Проводящими ключевыми цепями при этом наборе входных сигналов становятся шестая инверсная ключевая цепь (транзисторы 37, 32 и 33) и третья прямая дополнительная ключевая цепь (транзисторы 44, 45 и 41). В результате на выходе второго инвертора 2 формируется логическая "1" , а дополнительный триггер-фиксатор 14 устанавливается в "0". Таким образом, значение функции переноса на выходе второго разряда равно нулю. Поскольку на прямом дополнительном выходе 25 также сформирован логический "0", триггер-фиксатор 6 устанавливается в состояние логической "1", что свидетельствует о том, что значение суммы равно единице.

Таким образом из заданного числа каскадов может быть построен сумматор на требуемое число разрядов, выполняющий операцию суммирования за один такт с фиксацией результатов в каждом разряде.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КАСКАДНЫХ УСТРОЙСТВ НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209508C1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| ТАКТИРУЕМЫЙ ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2382490C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2258303C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2515225C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

Изобретение относится к области вычислительной техники и может быть использовано в сверхбольших интегральных схемах в качестве элементной базы устройств каскадной логики и конвейерной обработки данных, в частности при реализации арифметических и логических устройств. В каждом каскаде устройства используются парафазные входы, введены в логический блок 5 инверсные ключевые цепи 16, а также дополнительные ключевые цепи 17, 18, в каждый каскад введены второй инвертор 2, триггер-фиксатор 6 и дополнительные транзисторы р-типа 7, 8 и 10 - 13, а также осуществлены новые связи между каскадами устройства. Технический результат: расширение функциональных возможностей устройства. 3 з.п.ф-лы, 5 ил.

| US 4668880 A, 26.05.87 | |||

| US 4780626 A, 25.10.88 | |||

| Кармазинский А.Н | |||

| Синтез принципиальных схем цифровых элементов на МДП-транзисторах | |||

| - М.: Радио и связь, 1983, с.127-136 | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

| ШАРНИРНЫЙ ОТКЛОНИТЕЛЬ КОМПОНОВКИ БУРИЛЬНОЙ КОЛОННЫ | 1992 |

|

RU2082864C1 |

| Машина для разделения сыпучих материалов и размещения их в приемники | 0 |

|

SU82A1 |

| DE 3047222 A1, 15.07.82. | |||

Авторы

Даты

1999-06-27—Публикация

1998-04-24—Подача