Устройство относится к вычислительной технике и предназначено для вычисления натурального логарифма двоичного числа, представленного в формате "фиксированная запятая".

Известен цифровой логарифмический функциональный преобразователь [1] , содержащий генератор импульсов, первый и второй счетчики, блок сравнения кодов, вычислитель кодов, счетчик с предварительной установкой, регистр результата и блок задержки.

Недостатки преобразователя - низкое быстродействие, наличие динамических элементов, большой объем оборудования.

Наиболее близким техническим решением к изобретению, выбранным в качестве прототипа, является устройство для вычисления логарифма [2] , содержащее первый и второй регистры, первые выходы которых подключены к первым информационным входам соответствующих сумматоров, и блок хранения констант.

Недостатками данного устройства являются низкое быстродействие, наличие n-1 итераций, где 2-n - абсолютная погрешность вычисления, большой объем оборудования. Хотя выбранное в качестве прототипа устройство работает в диапазоне целых чисел в формате "фиксированная запятая", а предлагаемое устройство - в диапазоне аргументов [1/4, 1[ в формате "фиксированная запятая", но по принципу вычисления логарифма, а также конструктивно и схематически, наличием общих блоков и связей прототип является наиболее близким техническим решением к изобретению.

Цель изобретения - повышение быстродействия устройства.

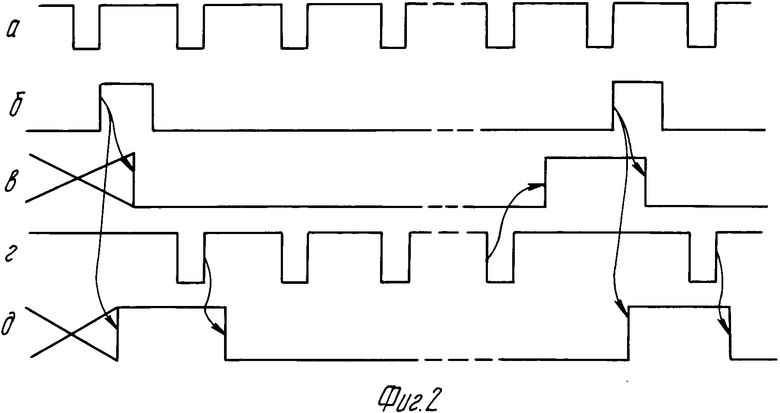

На фиг. 1 представлена блок-схема предлагаемого устройства для вычисления натурального логарифма; на фиг. 2 - временные диаграммы работы устройства, где а - сигнал на входе синхронизации устройства, б - сигнал на входе исходного состояния устройства, в - сигнал с первого выхода узла формирования унитарного кода, г - сигнал с выхода элемента ИЛИ, д - сигнал с выхода D-триггера.

Устройство для вычисления натурального логарифма содержит первый 1 и второй 2 регистры, первые выходы которых подключены к первым информационным входам соответствующих сумматоров 3 и 4, D-триггер 5, вход установки в единицу которого объединен с входами установки в ноль первого 1 и второго 2 регистров и является входом 6 исходного состояния устройства. Вход синхронизации D-триггера 5 объединен с входами синхронизации первого 1 и второго 2 регистров и подключен к выходу элемента ИЛИ 7. Первый вход элемента ИЛИ 7 является входом 8 синхронизации устройства. Второй вход элемента ИЛИ 7 объединен с информационным входом D-триггера 5 и управляющим входом первого мультиплексора 9 и подключен к первому выходу узла 10 формирования унитарного кода. Второй выход узла 10 подключен к управляющему входу узла 11 сдвига и адресному входу блока 12 хранения констант, подключенного выходом к первому информационному входу первого мультиплексора 9. Выход мультиплексора 9 подключен к второму информационному входу второго сумматора 4, выход которого объединен с информационным входом второго регистра 2 и является информационным выходом 13 устройства. Второй информационный вход первого мультиплексора 9 подключен к второму выходу первого регистра 1, третий выход которого подключен к входу узла 10 формирования унитарного кода. Первый выход первого регистра 1 подключен через узел 11 сдвига к второму информационному входу первого сумматора 3, подключенного выходом к первому информационному входу второго мультиплексора 14. Управляющий вход мультиплексора 14 подключен к выходу D-триггера, выход - к информационному входу первого регистра 1, а второй информационный вход второго мультиплексора 14 является информационным входом 15 устройства.

Первый выход первого регистра 1 равен знаковому разряду и мантиссе аргумента. Второй выход первого регистра 1 равен инверсному знаковому разряду и мантиссе аргумента. Третий выход первого регистра 1 равен m/2 старшим разрядам мантиссы аргумента, где m - мультипликативная разрядность.

Устройство может быть реализовано на базовом матричном кристалле 1515хМ1, заказных БИС, микросхемах серии 533: регистры - 553 ИР 13, мультиплексоры - 533 ЛР 1, узел сдвига - 533 ЛИ 2, 533 ЛЛ 1, сумматоры - 533 ИМ 6, узел формирования унитарного кода - 533 ЛЛ 2, элемент ИЛИ - 533 ЛЛ 1, D-триггер, блок хранения констант - 533 ЛА 16, 533 ЛА 2.

В основу работы устройства для вычисления натурального логарифма положены мультипликативные алгоритмы

xk+1 = xk + 2-jk+1xk; x ∈ [ 1/4 , 1[

yk+1 = yk - ln (1 + 2-jk+1); xo = x, yo = 0, где хо, yo - начальные условия для вычисления ln x;

xk, yk - значения операндов предыдущей итерации;

xk+1, yk+1 - значения операндов текущей итерации;

jk+1 - величина сдвига текущей итерации, равная порядковому номеру старшего нуля в мантиссе аргумента;

ln(1 + 2-jk+1) - значение константы текущей итерации.

Таким образом, вычисление ln x сводится к заданию начальных условий хо, yo, определению величины сдвига jk+1, равной порядковому номеру старшего нуля в мантиссе аргумента xk, сдвига хk на jk+1 двоичных разрядов в сторону младших разрядов, параллельному суммированию операнда хk со сдвинутым значением xk ˙2-jk+1 и суммированию yk с константой -ln(1 + 2-jk+1).

Вычисления прекращаются по достижении  старшими разрядами мантиссы значений 1 0

старшими разрядами мантиссы значений 1 0 . При этом

. При этом

yh=  (1+2-jk+1)+xh-1= lnx.

(1+2-jk+1)+xh-1= lnx.

Таким образом, исходя из свойств натурального логарифма, достаточно обработать лишь  разрядов аргумента х, где m - мультипликативная разрядность аргумента, 2-n - абсолютная погрешность вычислений, m = n + 1.

разрядов аргумента х, где m - мультипликативная разрядность аргумента, 2-n - абсолютная погрешность вычислений, m = n + 1.

V ≥ n + log2n, где V - полная разрядность операндов х и y для обеспечения точности вычислений в 2-n.

Доказательство алгоритма

ln(1+x)= x-x2/2+x3/3. . .

При 0≅x<2-m/2 ln(1 + x)≈ x;

x (1+2-jk+1)= 1+xh-1;

(1+2-jk+1)= 1+xh-1;

ln[x (1+2-jk+1)] = ln(1+xh-1);

(1+2-jk+1)] = ln(1+xh-1);

lnxo= - ln(1+2-jk+1)+xh-1.

ln(1+2-jk+1)+xh-1.

П р и м е р. Вычислить ln x, х = 0,62890625; ln x = 0,4637732;

n = 8; m = 8 + 1 = 9;  =

=  4,5

4,5 = 5;

= 5;

V = 8 + 3 = 11.

ln x = 1,10001001 (дополнительный код).

Прямой код 0,01110111, ln x = -0,46484375; 2-8 = 0,00390625, Δ = 0,0010705 < 2-8.

Устройство работает следующим образом.

По сигналу б (см. фиг. 2) исходного состояния (0-1-0), поступающему на вход 6 первый 1 и второй 2 регистры устанавливаются в состояние "0". Это обеспечивает запись yo = 0 во второй регистр 2, установку первого выхода узла 10 формирования унитарного кода в "0", причем сигнал с первого выхода узла формирования унитарного кода формируется в соответствии с выражением

STOP= x1∧x2∧ . . . ∧xm/2=  xi=1i, где П - логическое умножение;

xi=1i, где П - логическое умножение;

xi - i-разряды мантиссы аргумента, при этом STOP = 0 деблокирует прохождение синхроимпульсов через элемент ИЛИ 7, установку в "1" D-триггера 5. Если управляющий вход второго мультиплексора 14 находится в состоянии "1", то пропускается сигнал с второго входа второго мультиплексора 14, т. е. информационного входа 15 (хо) устройства. По переднему фронту синхроимпульса с выхода элемента ИЛИ 7 (1-0-1) в первый регистр 1 записыва- ется значение аргумента хо, во второй регистр 2 - yo = 0. Причем по заднему фронту синхроимпульса в D-триггер 5 записывается "0", так как (STOP = 0) управляющий вход второго мультиплексора 14 устанавливается в "0" и на информационный вход первого регистра 1 поступает первый информационный вход второго мультиплексора 14. Третий выход первого регистра 1, соответствующий  старшим разрядам мантиссы аргумента, поступает на вход узла 10 формирования унитарного кода для формирования jK+1.

старшим разрядам мантиссы аргумента, поступает на вход узла 10 формирования унитарного кода для формирования jK+1.

Пусть Zi - i-разряд унитарного кода jk+1, xi - i-й разряд мантиссы аргумента, тогда

Zi= x xi.

xi.

Унитарный код jk+1 поступает на управляющий вход узла 11 сдвига, который работает в соответствии с логикой xk+1∧[( )∨(2

)∨(2 Z1∨2-2∧Z2∨. . . ∨2-m/2∧Zm/2)] xk+1∧(

Z1∨2-2∧Z2∨. . . ∨2-m/2∧Zm/2)] xk+1∧(

2-i∧Z1), где xk+1 - третий выход первого регистра 1;

2-i∧Z1), где xk+1 - третий выход первого регистра 1;

Σ - логическое сложение, т. е. сдвиг xk+1 соответствует значению унитарного кода jk+1.

Блок 12 хранения констант содержит  констант типа -ln(1 +2-jk+1), записанных по адресам jk+1 = 1,2, . . . , m/2. В качестве адреса поступает унитарный код jk+1, при этом по нулевому адресу записаны все нули, для обеспечения записи во второй регистр 2 по первому синхроимпульсу yo = 0. Первый выход первого регистра 1, соответствующий полному значению аргумента xk, поступает на вход узла 11 сдвига и первый вход первого сумматора 3, который осуществляет операцию сложения xk + 2-jk+1 xk. Второй сумматор 4 выполняет операцию yk-ln(1 + +2-jk+1). По сигналу STOP = 1 блокируется прохождение синхроимпульсов на входы синхронизации регистров 1, 2, а первый мультиплексор 9 переключается на второй информационный вход, подключенный к второму выходу первого регистра 1, соответствующий значению 1 - xh, т. е. знаковый разряд равен единице, а мантисса берется без изменений. На выходе 13 второго сумматора 4 формируется результат

констант типа -ln(1 +2-jk+1), записанных по адресам jk+1 = 1,2, . . . , m/2. В качестве адреса поступает унитарный код jk+1, при этом по нулевому адресу записаны все нули, для обеспечения записи во второй регистр 2 по первому синхроимпульсу yo = 0. Первый выход первого регистра 1, соответствующий полному значению аргумента xk, поступает на вход узла 11 сдвига и первый вход первого сумматора 3, который осуществляет операцию сложения xk + 2-jk+1 xk. Второй сумматор 4 выполняет операцию yk-ln(1 + +2-jk+1). По сигналу STOP = 1 блокируется прохождение синхроимпульсов на входы синхронизации регистров 1, 2, а первый мультиплексор 9 переключается на второй информационный вход, подключенный к второму выходу первого регистра 1, соответствующий значению 1 - xh, т. е. знаковый разряд равен единице, а мантисса берется без изменений. На выходе 13 второго сумматора 4 формируется результат

lnx0= -Σln(1+2-jk+1)+xh-1.

Таким образом, существенное увеличение быстродействия предлагаемого устройства по сравнению с прототипом достигается в 2 раза за счет применения мультипликативных алгоритмов, что позволяет снизить количество итераций до  (

(

- целая часть числа, взятая сверху, например

- целая часть числа, взятая сверху, например  4,1

4,1 = 5), при этом m = n+1, где 2-n - абсолютная погрешность вычислений, а m - мультипликативная разрядность, равная для данного метода определения величины сдвига m = n+1, обработки лишь половины аргумента, а также за счет параллельности обработки операндов. Кроме того, заявляемое техническое решение обеспечивает простоту схемотехнического решения, уменьшение оборудования в 2 раза, точность в 2-n и уменьшение числа итераций в 2 раза по сравнению с прототипом. (56) 1. Авторское свидетельство СССР N 1160405, кл. G 06 F 7/556, 1983,

= 5), при этом m = n+1, где 2-n - абсолютная погрешность вычислений, а m - мультипликативная разрядность, равная для данного метода определения величины сдвига m = n+1, обработки лишь половины аргумента, а также за счет параллельности обработки операндов. Кроме того, заявляемое техническое решение обеспечивает простоту схемотехнического решения, уменьшение оборудования в 2 раза, точность в 2-n и уменьшение числа итераций в 2 раза по сравнению с прототипом. (56) 1. Авторское свидетельство СССР N 1160405, кл. G 06 F 7/556, 1983,

2. Авторское свидетельство СССР N 1179328, кл. G 06 F 7/556, 1984.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИВЕДЕНИЯ ФУНКЦИЙ К МУЛЬТИПЛИКАТИВНОМУ АЛГОРИТМУ ВЫЧИСЛЕНИЙ | 1990 |

|

RU2028659C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА КОМПЛЕКСНОГО ЧИСЛА | 1991 |

|

RU2010312C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ S-ИЧНЫХ ЦИФР В ПОЗИЦИОННО-ОСТАТОЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ | 1991 |

|

RU2006919C1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1612374A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для деления | 1990 |

|

SU1742815A1 |

| Преобразователь комплексных сигналов | 1983 |

|

SU1104525A1 |

Изобретение относится к вычислительной технике и предназначено для вычисления натурального логарифма двоичного числа, представленного в формате "фиксированная запятая". Устройство содержит два регистра, два сумматора, D-триггер, элемент ИЛИ, два мультиплексора, узел формирования унитарного кода, узел сдвига и блок хранения констант. Быстродействие повышается за счет мультипликативного алгоритма обработки половины аргумента. 2 ил.

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ НАТУРАЛЬНОГО ЛОГАРИФМА, содержащее два сумматора, узел сдвига, блок хранения констант и два регистра, первые выходы которых подключены к первым информационным входам соответствующих сумматоров, выход второго сумматора является выходом устройства, отличающееся тем, что оно содержит два мультиплексора, узел формирования унитарного кода, элемент ИЛИ, D-триггер, вход установки в "1" которого объединен с входами установки в "0" первого и второго регистров и является входом исходного состояния устройства, вход синхронизации D-триггера объединен с входами синхронизации первого и второго регистров и подключен к выходу элемента ИЛИ, первый вход которого является входом синхронизации устройства, второй вход элемента ИЛИ объединен с информационным входом D-триггера и управляющим входом первого мультиплексора и подключен к первому выходу узла формирования унитарного кода, второй выход которого подключен к управляющему входу узла сдвига и адресному входу блока хранения констант, выход которого подключен к первому информационному входу первого мультиплексора, выход которого подключен к второму информационному входу второго сумматора, выход которого соединен с информационным входом второго регистра, второй информационный вход первого мультиплексора подключен к второму выходу первого регистра, третий выход которого подключен к входу узла формирования унитарного кода, первый выход первого регистра подключен к информационному входу узла сдвига, выход которого подключен к второму информационному входу первого сумматора, выход которого подключен к первому информационному входу второго мультиплексора, управляющий вход которого подключен к выходу D-триггера, выход второго мультиплексора подключен к информационному входу первого регистра, а его второй информационный вход является информационным входом устройства.

Авторы

Даты

1994-01-30—Публикация

1991-07-25—Подача