Изобретение относится к вычислительной технике, а именно к кодирующим устройствам, и может быть использовано в цифровых моделирующих, управляющих и вычислительных системах как общего, так и специального назначения.

Известно устройство для последовательного выделения единиц, выделяющие порядковый номер каждой единицы входного кода числа.

Недостатком известного устройства являются ограниченные функциональные возможности и низкое быстродействие из-за последовательной обработки входного кода.

Наиболее близким техническим решением к заявляемому устройству является "Устройство для вычисления функций", взятое в качестве прототипа и содержащее первый и второй регистры, узел памяти кода функций, коммутатор анализируемых разрядов, сумматор, узел определения длины сдвига, узел памяти весовых коэффициентов, первый и второй элементы И, первый и второй мультиплексоры, счетчик, причем выходы первого и второго мультиплексоров соединены со входами соответственно первого и второго слагаемых сумматора, выход которого соединен с первым выходом блока анализа аргумента и подключен к первым информационным входам первого и второго мультиплексовров, второй информационный вход второго мультиплексора соединен с адресным входом узла памяти весовых коэффициентов и первым выходом узла определения длины сдвига, вход которого подключен к выходу второго регистра, второй выход узла определения длины сдвига соединен со вторым выходом блока анализа аргумента и первым входом первого элемента И, второй вход которого соединен со входом шестого разряда второго информационного входа блока анализа аргумента, выход первого элемента подключен к счетному входу счетчика, вход записи которого соединен со входом начальной установки блока анализа аргумента, выход переноса счетчика соединен с четвертым выходом блока анализа аргумента к управляющему входу узла памяти кода функции, адресный вход которого соединен со входом задания режима блока анализа аргумента, выход узла памяти кода функции в первой группе разрядов информационного входа второго регистра, вход второй группы разрядов информационного входа которого соединен со вторым адресным входом узла памяти весовых коэффициентов, соответствующими входами второго элемента И и выходом счетчика, третий адресный вход узла памяти весовых коэффициентов соединен со входом задания режима блока анализа аргумента, выход узла памяти весовых коэффициентов соединен с информационным выходом блока анализа аргумента, третий выход которого соединен с выходом второго элемента И, пятый выход блока анализа аргумента подключен к четвертому адресному входу узла памяти весовых коэффициентов, третьей группе разрядов информационного входа второго регистра и к выходу старшего разряда первого регистра, информационный выход которого соединен с информационным входом коммутатора анализируемых разрядов, выход которого соединен с четвертой группой разрядов информационного входа второго регистра, информационный вход первого регистра соединен со вторым информационным входом блока анализа аргумента, вход третьего разряда первого информационного входа которого соединен с первыми управляющими входами первого и второго мультиплексоров, вход второго разряда первого информационного входа блока анализа аргумента соединен со вторым управляющим входом первого мультиплексора, второй информационный вход которого соединен со входом логической единицы блока анализа аргумента, третий информационный вход первого мультиплексора соединен со входом логического нуля блока анализа аргумента, третий управляющий вход мультиплексора соединен со вторым управляющим входом второго мультиплексора и входом первого разряда информационного входа блока анализа аргумента, входы четвертого и пятого разрядов первого информационного входа которого соединены со входами разрешения записи соответственно первого и второго регистров.

Недостаток устройства: низкое быстродействие, обусловленное суммарной задержкой селектора, временем переключения счетчика из 0 в 33, задержками регистра, блока определения длины сдвига, мультиплексора, шестиразрядного сумматора, а также наличие большого количества вспомогательных управляющих сигналов, что усложняет стыковку с другими устройствами.

Цель изобретения - повышение быстродействия за счет параллельно-последовательной обработки входного кода.

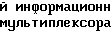

Поставленная цель достигается посредством того, что устройство для приведения функций к мультипликативному алгоритму вычислений, содержащее тридцатипятиразрядный регистр, блок задания режима, блок хранения весовых коэффициентов, первый и второй мультиплексоры, причем выход блока хранения весовых коэффициентов соединен с выходом весовых коэффициентов устройства, выход второго мультиплексора является выходом величины сдвига устройства, управляющие входы с первого по третий второго мультиплексора соединены соответственно с первого по третий управляющими входами устройства, вход синхронизации и информационный вход тридцатипятиразрядного регистра соединены соответственно со входом запуска и информационным входом устройства, прямой выход первого разряда тридцатипятиразрядного регистра подключен к первому адресному входу блока хранения весовых коэффициентов и является выходом знакового разряда устройства, первый информационный вход блока задания режима соединен со вторым адресным входом блока хранения весовых коэффициентов и является входом задания кода функции устройства, дополнительно содержит блок формирования признаков обнуления, блок анализа старшего байта, с первого по третий блоки анализа младших разрядов, первый и второй шифраторы, причем выход первого шифратора подключен к третьему адресному входу блока хранения весовых коэффициентов и первому информационному входу второго мультиплексора, второй и третий информационные входы которого подключены соответственно к первому и второму выходам второго шифратора, первый информационный вход которого соединен с первым информационным входом первого шифратора и подключен к выходу блока анализа старшего байта, вторые, третьи и четвертые информационные входы первого и второго шифраторов соответственно объединены и соединены с выходами соответственно первого, второго и третьего блоков анализа младших разрядов, входы первых разрядов с первого по третий блоков анализа и вход первого разряда блока анализа старшего байта подключены к первому выходу блока задания режима, второй выход которого подключен к управляющему входу первого мультиплексора, второй информационный вход блока задания режима подключен к прямому выходу первого разряда тридцатипятиразрядного регистра, инверсные и прямые выходы со второго по тридцать четвертый разрядов которого подключены соответственно к первому и второму информационным входам первого мультиплексора, выходы с первого по тридцать третий и с тридцать четвертого по шестьдесят седьмой которого являются соответственно прямыми и инверсными выходами первого мультиплексора, выходы с первого по тридцать третий разрядов которого подключены ко входу блока формирования признаков обнуления, выходы девятого, седнадцатого и двадцать пятого разрядов первого мультиплексора подключены соответственно к объединенным входам десятого разряда блока анализа старшего байта и второго разряда второго блока анализа младших разрядов, к объединенным входам десятого разряда второго блока анализа младших разрядов и второго разряда третьего блока анализа младших разрядов, выходы с первого по восьмой, с десятого по шестнадцатый, с восемнадцатого по двадцать четвертый и с двадцать шестого по тридцать третий разрядов первого мультиплексора подключены соответственно к входам со второго по девятый разрядов первого блока анализа младших разрядов и с третьего по десятый разрядов третьего блока анализа младших разрядов, выход сорок второго разряда первого мультиплексора подключен к входам девятнадцатого разряда блока анализа старшего байта и одиннадцатого разряда первого блока анализа младших разрядов, выход сорок третьего разряда первого мультиплексора соединен со входами двадцатого разряда блока анализа старшего байта и двенадцатого разряда первого блока анализа младших разрядов, выход пятидесятого разряда первого мультиплексора соединен с входами девятнадцатого разряда первого блока анализа младших разрядов и одиннадцатого разряда второго блока анализа младших разрядов, выход пятьдесят первого разряда первого мультиплексора соединен с входом двадцатого разряда первого блока анализа младших разрядов и двенадцатого разряда второго блока анализа и младших разрядов, выход пятьдесят восьмого разряда первого мультиплексора соединен с входами девятнадцатого разряда второго блока анализа младших разрядов и одиннадцатого разряда третьего блока анализа младших разрядов, выход пятьдесят девятого разряда мультиплексора соединен с входами двадцатого разряда второго блока анализа младших разрядов и двадцатого разряда третьего блока анализа младших разрядов, выхода разрядов с тридцать четвертого по сорок первый, с сорок четвертого по сорок девятый, с пятьдесят второго по пятьдесят седьмой и с шестидесятого по шестьдесят седьмой первого мультиплексора подключены к входам разрядов соответственно с одиннадцатого по восемнадцатый блока анализа старшего байта, с тринадцатого по восемнадцатый первого блока анализа младших разрядов, с тринадцатого по восемнадцатый третьего блока анализа младших разрядов, входы двадцать первых разрядов с первого по третий блоков анализа младших разрядов соединены соответственно с первого по третий выходами блока формирования признаков обнуления, четвертый выход которого соединен с выходом признака обнуления устройства, блок анализа старшего байта содержит элемент НЕ, с первого по пятый элементы И-НЕ, с первого по третий элементы ИЛИ-НЕ, с первого по четвертый узлы прямого выделения единицы, с первого по четвертый узлы обратного выделения единицы, причем входы первого разряда с первого по четвертый узлов прямого и обратного выделения единицы соединены с первым входом первого элемента И-НЕ и являются входом первого разряда блока, вход второго разряда которого подключен к второму входу первого элемента И-НЕ и входам второго разряда первого узла прямого выделения единицы, вход третьего разряда блока соединен с третьим входом первого элемента И-НЕ, входом третьего разряда первого узла прямого выделения единицы и входом пятого разряда первого узла обратного выделения единицы, вход четвертого разряда блока соединен с входами четвертого разряда первого узла прямого выделения единицы, шестого разряда первого узла обратного выделения единицы и второго разряда второго узла прямого выделения единицы, вход шестого разряда блока соединен с входами четвертого разряда второго узла прямого выделения единицы, шестого разряда второго узла обратного выделения единицы и второго разряда третьего узла прямого выделения единицы, вход восьмого разряда блока соединен с входами четвертого разряда третьего узла прямого выделения единицы, шестого разряда третьего узла обратного выделения единицы и второго разряда четвертого узла прямого выделения единицы, вход четырнадцатого разряда блока соединен с входами четвертого разряда первого узла обратного выделения единицы, шестого разряда второго узла прямого выделения единицы и второго разряда второго узла обратного выделения единицы, вход шестнадцатого разряда блока соединен со входами четвертого разряда второго узла обратного выделения единицы и второго разряда третьего узла обратного выделения единицы, вход восемнадцатого разряда блока соединен с входами четвертого разряда третьего узла обратного выделения единицы, шестого разряда четвертого узла прямого выделения единицы и второго разряда четвертого узла обратного выделения единицы, вход пятого разряда блока соединен с входами третьего разряда второго узла прямого выделения единицы и пятого разряда второго узла обратного выделения единицы, вход седьмого разряда блока соединен с входами третьего разряда третьего узла прямого выделения единицы и пятого разряда третьего узла обратного выделения единицы, вход девятого разряда блока соединен с входами третьего разряда четвертого узла прямого выделения и пятого разряда четвертого узла обратного выделения единицы, входы тринадцатого, пятнадцатого и семнадцатого разрядов блока соединены с входами третьего разряда соответственно второго, третьего и четвертого узлов прямого выделения единицы, вход десятого разряда блока соединен с входами четвертого и шестого разрядов четвертых узлов прямого и обратного выделения единицы, вход одиннадцатого разряда блока соединен с входом пятого разряда первого узла прямого выделения единицы, вход двенадцатого разряда блока соединен с входами шестого разряда первого узла прямого выделения единицы и второго разряда первого блока обратного выделения единицы, вход седьмого разряда блока соединен с входами третьего разряда третьего узла прямого выделения единицы и пятого разряда третьего узла обратного выделения единицы, вход девятого разряда блока соединен с входами третьего разряда четвертого узла прямого выделения единицы и пятого разряда четвертого узла обратного выделения единицы, входы тринадцатого, пятнадцатого и семнадцатого разрядов блока соединены с входами третьего разряда, соответственно второго, третьего и четвертого узлов прямого выделения единицы, вход десятого разряда блока соединен с входами четвертого и шестого разрядов четвертых узлов прямого и обратного выделения единицы, вход одиннадцатого разряда блока соединен с входом пятого разряда первого узла прямого выделения единицы, вход двадцатого разряда блока соединен с входами шестого разряда первого узла прямого выделения единицы и второго разряда первого блока обратного выделения единицы, входы девятнадцатого и двадцатого разрядов блока соединены с входами соответственно третьего и четвертого разрядов четвертого блока обратного выделения единицы, выход элемента НЕ, первые входы первых, вторых, третьих и четвертых узлов прямого и обратного выделения единицы соединены с выходами соответственно с первого по девятый блок, вход элемента НЕ подключен к выходу первого элемента И-НЕ и управляющим входом первого узла прямого выделения единицы, вторые и третьи выходы с первого по четвертый блоков прямого выделения единицы подключены соответственно к первым и вторым входам соответственно со второго по пятый элементов И-НЕ, выходы которых подключены к управляющим входам с первого по четвертый узлов обратного выделения единицы, вторые и третьи выходы с первого по третий узлов обратного выделения единицы подключены соответственно к первому и второму входам соответственно с первого по третий элементов ИЛИ-НЕ, выходы которых подключены к управляющим входам соответственно со второго по четвертый узлов прямого выделения единицы, блок анализа младших разрядов содержит восемь элементов И и узел анализа старшего байта, входы с первого по двадцатый разрядов которого соединены с входами соответствующих разрядов блока, выходы со второго по девятый узла анализа старшего байта соединены с первыми входами соответственно с первого по восьмой элементов И, вторые входы которых соединены с входом двадцать первого разряда блока, выходы элементов И являются выходами соответствующих разрядов блока, причем узел анализа старшего байта выполнен в виде блока анализа старшего байта, узел прямого выделения единицы содержит пять элементов И-НЕ, первый и второй элементы НЕ, причем вход первого элемента НЕ, соединен с первыми входами первого и второго элементов И-НЕ и соединены с входом первого разряда узла, выход первого элемента НЕ подключен к первому входу третьего элемента И-НЕ, второй вход которого соединен со вторым входом второго элемента И-НЕ и входом второго разряда узла, входы с третьего по шестой разрядов которого соединены соответственно со второго по четвертый входами первого элемента И-НЕ и третьим входом второго элемента И-НЕ, выход которого соединены соответственно с первым и вторым входами четвертого элемента И-НЕ, третий вход и выход которого подключены соответственно к выходу третьего элемента И-НЕ и первому входу пятого элемента И-НЕ, второй вход которого соединен с управляющим входом узла и соединен со вторым выходом узла, третий выход которого подключен к выходу пятого элемента И-НЕ и входу второго элемента НЕ, выход которого соединен с первым выходом узла, узел обратного выделения единицы содержит пять элементов ИЛИ-НЕ, элемент НЕ, вход которого соединен с первым входом первого элемента ИЛИ-НЕ и входом первого разряда узла, выход элемента НЕ соединен с первыми входами второго и третьего элементов ИЛИ-НЕ, вторые входы первого и второго элементов ИЛИ-НЕ соединены со входом второго разряда узла, входы с третьего по шестой разрядов которого подключены соответственно ко второму, третьему и четвертому входам третьего элемента ИЛИ-НЕ и третьему входу второго элемента ИЛИ-НЕ, входы которых подключены соответственно к первому и второму входам четвертого элемента ИЛИ-НЕ, третий вход которого подключен к выходу первого элемента ИЛИ-НЕ, выход четвертого элемента ИЛИ-НЕ соединен с первым входом пятого элемента ИЛИ-НЕ, второй вход которого соединен со вторым выходом узла и управляющим входом узла, третий выход которого соединен с первым выходом узла и выходом пятого элемента ИЛИ-НЕ.

Сопоставительный анализ с прототипом показывает, что предлагаемое устройство отличается наличием новых блоков и их связями с остальными элементами схемы.

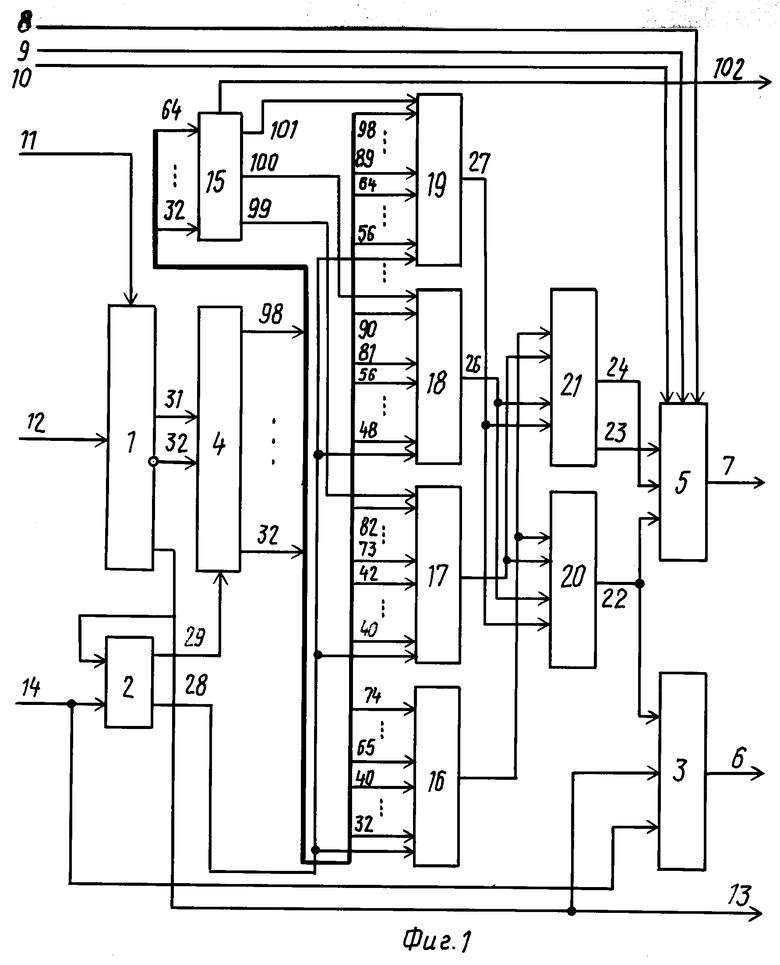

На фиг. 1 представлена блок-схема устройства, где:

1 - тридцатипятиразрядный регистр устройства;

2 - блок задания режима устройства,

3 - блок хранения весовых коэффициентов устройства.

й

й

6 - выход блока хранения весовых коэффициентов, являющийся выходом весовых коэффициентов устройства,

7 - выход второго мультиплексора, являющийся выходом величины сдвига устройства, с

с

й

й

11 - вход запуска устройства,

12 - информационный вход устройства,

13 - выход знакового разряда устройства,

14 - вход задания кода функции устройства,

15 - блок формирования признаков обнуления устройства,

16 - блок анализа старшего байта устройства,

с

с т

т

в

в

22 - выход первого шифратора устройства, в

в ы второго

ы второго

е

е /

/

и

и й

й ка

ка й

й о

о ы

ы

32-64 - с первого по тридцать третий инверсные выходы первого мультиплексора устройства,

65-98 - с тридцать четвертого по шестьдесят седьмой прямые выходы первого мультиплексора устройства, т

т

102 - выход признака обнуления устройства.

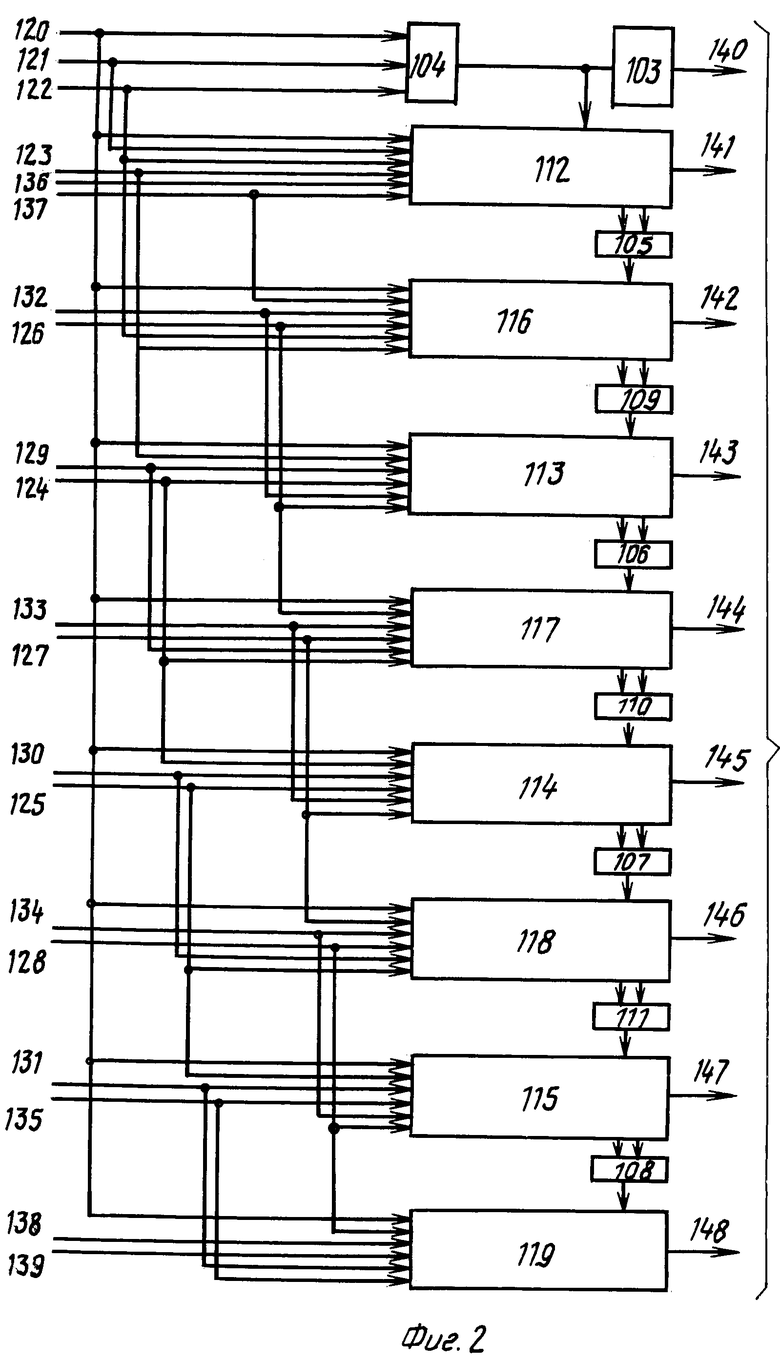

На фиг. 2 - блок-схема блока анализа старшего байта, где :

103 - элемент НЕ блока анализа старшего байта,

элементы

элементы г

г й

й

т

т

124 - вход шестого разряда блока анализа старшего байта,

125 - вход восьмого разряда блока анализа старшего байта,

126 - вход четырнадцатого разряда блока анализа старшего байта,

127 - вход шестнадцатого разряда блока анализа старшего байта,

128 - вход восемнадцатого разряда блока анализа старшего байта,

129 - вход пятого разряда блока анализа старшего байта,

130 - вход седьмого разряда блока анализа старшего байта,

131 - вход девятого разряда блока анализа старшего байта, о

о надцатого/ семнадцатого

надцатого/ семнадцатого о

о надцатый

надцатый в

в ц

ц

г

г

140-148 - с первого по девятый выходы блока анализа старшего байта.

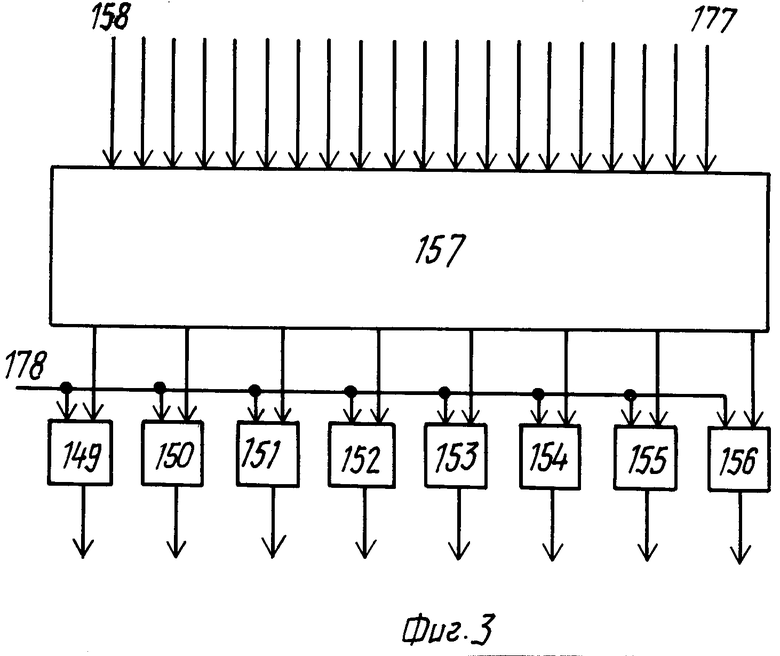

На фиг. 3 - блок-схема блока анализа младших разрядов, где:

149-156 - с первого по восьмой элементов И блока анализа младших разрядов,

157 - узел анализа старшего байта блока анализа младших разрядов,

158-178 - входы с первого по двадцать первый разрядов блока анализа младших разрядов.

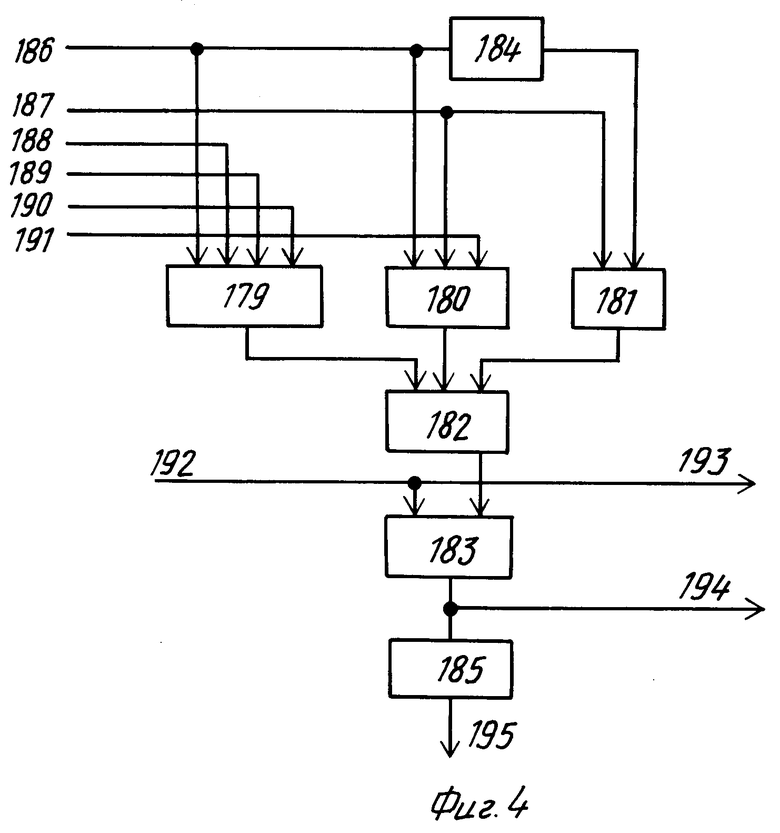

На фиг. 4 - блок-схема узла прямого выделения единицы, где :

179-183 - с первого по пятый элементы И-НЕ узла прямого выделения единицы ы

ы р

р т

т

186-191 - входы с первого по шестой разрядов узла прямого выделения единицы,

192 - управляющий вход узла прямого выделения единицы, и

и ы

ы а

а

195 - первый выход узла прямого выделения единицы.

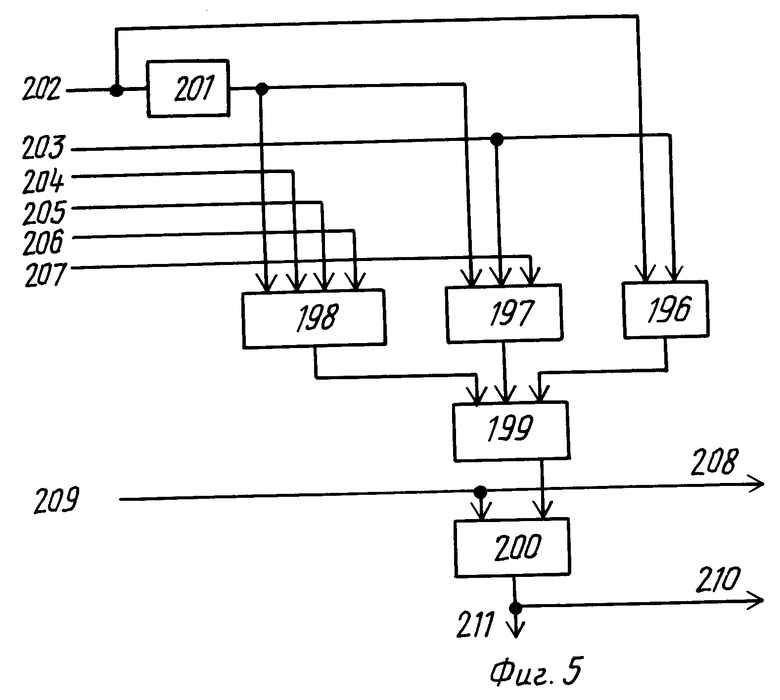

На фиг. 5 - блок-схема узла обратного выделения единицы, где:

196-200 - с первого по пятый элементы ИЛИ-НЕ узла обратного выделения единицы,

201 - элемент НЕ узла обратного выделения единицы,

202-207 - входы с первого по шестой разрядов узла обратного выделения единицы,

208 - второй выход узла обратного выделения единицы,

209 - управляющий вход узла обратного выделения единицы,

210 - третий выход узла обратного выделения единицы,

211 - первый выход узла обратного выделения единицы.

Устройство для приведения функций к мультипликативному алгоритму вычислений (фиг.1) содержит тридцатипятиразрядный регистр 1, блок задания режима 2, блок хранения весовых коэффициентов 3, первый и второй мультиплексоры 4, 5, причем выход 6 блока хранения коэффициентов 3 соединен с выходом весовых коэффициентов устройства, выход 7 второго мультиплексора 5 является выходом величины сдвига, управляющие входы 8,9,10 с первого по третий второго мультиплексора 5 соединены соответственно с первого по третий 8,9,10 управляющими входами устройства, вход запуска 11 и информационный вход 12 тридцатипятиразрядного регистра 1 соединены соответственно со входом запуска 11 и информационным входами устройства 12, прямой выход первого разряда тридцатипяти- разрядного регистра 1 подключен к первому адресному входу блока хранения весовых коэффициентов 3 и является выходом знакового разряда устройства 13, первый информационный вход 14 блока задания режима 2 соединен со вторым адресным входом блока хранения весовых коэффициентов 3 и является входом задания кода функции устройства. Устройство дополнительно содержит блок формирования признаков обнуления 15, блок анализа старшего байта 16, с первого по третий блоки анализа младших разрядов 17, 18, 19, первый и второй шифраторы 20, 21, причем выход 22 первого шифратора 20 подключен к третьему адресному входу блока хранения весовых коэффициентов 3 и первому информа- ционному входу второго мультиплексора 5, второй 23 и третий 24 информационные входы которого подключены соответственно к первому и второму выходам второго шифратора 21, первый информационный вход которого соединен с первым информационным входом первого шифратора 20 и подключен к выходу блока анализа старшего байта 16, вторые 25, третьи 26 и четвертые 27 информационные входы первого и второго шифратора 20, 21 соответственно объединены и соединены с выходами соответственно первого 17, второго 18 и третьего 19 блоков анализа младших разрядов, входы первых разрядов с первого по третий блоков анализа 17, 18, 19 и вход первого разряда блока анализа старшего байта 16 подключены к первому выходу 28 блока задания режима 2, второй выход 29 которого подключен к управляющему входу первого мультиплексора 4, второй информационный вход 29 блока задания режима 2 подключен к прямому выходу первого разряда тридцатипятиразрядного регистра 1, инверсные и прямые выходы со второго по тридцать четвертый разрядов которого подключены соответственно к первому 30 и второму 31 информационным входам первого мультиплексора 4, выходы с первого по тридцать третий 32-64 и с тридцать четвертого по шестьдесят седьмой 65-98 которого являются соответственно прямыми и инверсными выходами первого мультиплексора 4, выходы с первого по тридцать третий разрядов 32-64 которого подключены ко входу блока формирования признаков обнуления 15, выходы девятого 40, семнадцатого 48 и двадцать пятого 56 разрядов первого мультиплексора 4 подключены соответственно к объединенным входам десятого разряда блока анализа старшего байта 16 и второго разряда первого блока анализа младших разрядов 17, к объединенным входам десятого разряда первого блока анализа младших разрядов 17 и второго разряда второго блока анализа младших разрядов 18, к объединенным входам десятого разряда второго блока анализа младших разрядов 18 и второго разряда третьего блока анализа младших разрядов 19, выходы с первого по восьмой 32-39, с десятого по шестнадцатый 41-47, с восемнадцатого по двадцать четвертый 48-55 и с двадцать шестого по тридцать третий 57-64 разрядов первого мультиплексора 4 подключены соответственно ко входам с второго по девятый разрядов блока анализа старшего байта 16, с третьего по девятый разрядов первого блока анализа младших разрядов 17, с третьего по девятый разрядов второго блока анализа младших разрядов 19, выход сорок второго разряда 73 первого мультиплексора 4 подключены к входам девятнадцатого разряда блока анализа старшего байта 16 и одиннадцатого разряда первого блока анализа младших разрядов 17, выход сорок третьего разряда 74 первого мультиплексора 4 соединен с входами двадцатого разряда блока анализа старшего байта 16 и двенадцатого разряда первого блока анализа младших разрядов 17, выход пятидесятого разряда 81 первого мультиплексора 4 соединен с входами девятнадцатого разряда первого блока анализа младших разрядов 16 и одиннадцатого разряда второго блока анализа младших разрядов 18, выход пятьдесят первого 29 разряда первого мультиплексора 4 соединен с входами двадцатого разряда первого блока анализа младших разрядов 17 и двенадцатого разряда второго блока анализа младших разрядов 18, выход пятьдесят восьмого 89 разряда первого мультиплексора 4 соединен с входами девятнадцатого разряда второго блока анализа младших разрядов 18 и одиннадцатого разряда третьего блока анализа младших разрядов 19, выход пятьдесят девятого разряда 80 первого мультиплексора 4 соединен с входами двадцатого разряда второго блока анализа младших разрядов 18 и двенадцатого разряда третьего блока анализа младших разрядов 19, выходы разрядов с тридцать четвертого по сорок первый 65-72, с сорок четвертого по сорок девятый 75-80, с пятьдесят второго по пятьдесят седьмой 83-88 и с шестидесятого по шестьдесят седьмой 91-98 первого мультиплексора 4 подключены к входам разрядов соответственно с одиннадцатого по восемнадцатый блока анализа старшего байта 16, с тринадцатого по восемнадцатый первого блока анализа младших разрядов 17, с тринадцатого по восемнадцатый второго блока анализа младших разрядов 18, с тринадцатого по восемнадцатый третьего блока анализа младших разрядов 19, входы двадцать первых разрядов с первого по третий блоков анализа младших разрядов 17-19 соединены соответственно с первого по третий выходами 99, 100, 101 блока формирования признаков обнуления 15, четвертый выход которого соединен с выходом признака обнуления устройства 102.

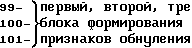

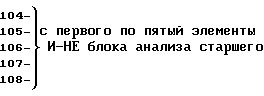

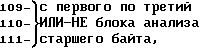

Блок анализа старшего байта (фиг.2) содержит элемент НЕ 103, с первого по пятый элементы И-НЕ, 104-108 с первого по третий элементы ИЛИ-НЕ 109-111, с первого по четвертый узлы прямого выделения единицы 112-115, с первого по четвертый узлы обратного выделения единицы 116-119, причем входы первого разряда с по четвертый узлов прямого и обратного выделения единицы 112-119 соединены с первым входом первого элемента И-НЕ 104 и являются входом первого разряда блока 120, вход второго разряда которого 121 подключен к второму входу первого элемента И-НЕ 112 и входам второго разряда первого узла прямого выделения единицы 112, вход третьего разряда блока 122 соединен с третьим входом первого элемента И-НЕ 104, входом третьего разряда первого узла прямого выделения единицы 112 и входом пятого разряда первого узла обратного выделения единицы 116, вход четвертого разряда блока 123 соединен с входами четвертого разряда первого узла прямого выделения единицы 119, шестого разряда первого узла обратного выделения единицы 116 и второго разряда второго узла прямого выделения единицы 113, вход шестого разряда блока 124 соединен с входами четвертого разряда второго узла прямого выделения единицы 113, шестого разряда второго узла обратного выделения единицы 117 и второго разряда третьего узла прямого выделения единицы 114, вход восьмого разряда блока 125 соединен с входами третьего узла прямого выделения единицы 114, шестого разряда третьего узла обратного выделения единицы 118 и второго разряда четвертого узла прямого выделения единицы 115, вход четырнадцатого разряда блока 126 соединен с входами четвертого разряда первого узла обратного выделения единицы 116, шестого разряда второго узла прямого выделения единицы 113 и второго разряда второго узла обратного выделения единицы 117, вход шестнадцатого разряда блока 127 соединен с входами четвертого разряда второго узла обратного выделения единицы 117, шестого разряда третьего узла прямого выделения единицы 114 и второго разряда третьего узла обратного выделения единицы 118, вход восемнадцатого разряда блока 128 соединен с входами четвертого разряда третьего узла обратного выделения единицы 118, шестого разряда четвертого узла прямого выделения единицы 115 и второго разряда четвертого узла обратного выделения единицы 119, вход пятого разряда блока 129 соединен с входами третьего разряда второго узла прямого выделения единицы 119 и пятого разряда второго узла обратного выделения единицы 117, вход седьмого разряда блока 113 соединен с входами третьего разряда третьего узла прямого выделения единицы 114 и пятого разряда третьего узла обратного выделения единицы 118, вход девятого разряда блока 131 соединен с входами третьего разряда четвертого узла прямого выделения единицы 115 и пятого разряда четвертого узла обратного выделения единицы 119, входы тридцатого 132, пятнадцатого 133 и семнадцатого 134 разрядов блока соединены с входами третьего разряда соответственно первого 116, второго 117 и третьего 118 узлов обратного выделения единицы и входами пятого разряда соответственно второго 113, третьего 114 и четвертого 115 узлов прямого выделения единицы, вход десятого разряда блока 135 соединен с входами четвертого и шестого разрядов четвертых узлов прямого и обратного выделения единицы 115, 119, вход одиннадцатого разряда блока 136 соединен с входом пятого разряда первого узла прямого выделения единицы 112, вход двенадцатого разряда блока 137 соединен с входами шестого разряда первого узла прямого выделения единицы 112 и второго разряда первого блока обратного выделения единицы 116, входы девятнадцатого 138 и двадцатого 139 разрядов блока соединены с входами соответственно третьего и четвертого разрядов четвертого блока обратного выделения единицы 119, выход элемента НЕ 103, первые выходы первых, вторых, третьих и четвертых узлов прямого и обратного выделения единицы 112-119 соединены с выходами с соответственно с первого по девятый 140-148 блока, вход элемента НЕ 103 подключен к выходу первого элемента И-НЕ 104 и управляющим входом первого узла прямого выделения единицы 112, вторые и третьи выходы с первого по четвертый блоков прямого выделения единицы 112-115 подключены соответственно к первым и вторым входам соответственно со второго по пятый элементов И-НЕ 105-108, выходы которых подключены к управляющим входам с первого по четвертый узлов обратного выделения единицы 116-119, вторые и третьи выходы с первого по третий узлов обратного выделения единицы 116-118 подключены соответственно к первому и второму входам соответственно с первого по третий элементов ИЛИ-НЕ 109-111 в выходы которых подключены к управляющим входам соответственно с второго по четвертый узлов прямого выделения единицы 113-115.

Блок анализа младших разрядов (фиг. 3) содержит восемь элементов И 149-156 и узел анализа старшего байта 157, входы с первого по двадцатый разрядов которого соединены с входами соответствующих разрядов блока 158-177, выходы с второго по девятый узла анализа старшего байта 157 соединены с первыми входами соответственно с первого по восьмой элементов И 149-156, вторые входы которых соединены с входом двадцать первого разряда блока 178, выходы элементов И являются выходами соответствующих разрядов блока, причем узел анализа старшего байта 157 выполнен в виде блока анализа старшего байта 16.

Узел прямого выделения единицы (фиг.4) содержит пять элементов И-НЕ 179-183, первый и второй элементы НЕ 184, 185, причем вход первого элемента НЕ 184 соединен с первыми входами первого и второго элементов И-НЕ 179, 180 и соединен с входом первого разряда узла 186, выход первого элемента НЕ 184 подключен к первому входу третьего элемента И-НЕ 181, второй вход которого соединен с вторым входом второго элемента И-НЕ 180 и входом второго разряда узла 187, входы с третьего по шестой разрядов которого 188, 189, 190, 191 соединены соответственно со второго по четвертый входами первого элемента И-НЕ 179 и третьим входом второго элемента И-НЕ 180, выходы которых соединены соответственно с первым и вторым входами четвертого элемента И-НЕ 182, третий вход и выход которого подключены соответственно к выходу третьего элемента И-НЕ 181 и первому входу пятого элемента И-НЕ 183, второй вход которого соединен с управляющим входом узла 192 и соединен со вторым выходом узла 193, третий выход которого 194 подключен к выходу пятого элемента И-НЕ 183 и входу второго элемента НЕ 185, выход которого соединен с первым выходом узла 195.

Узел обратного выделения единицы содержит пять элементов ИЛИ-НЕ 196-200, элемент НЕ 201, вход которого соединен с первым входом первого элемента ИЛИ-НЕ 196 и входом первого разряда узла 202, выход элемента НЕ 201 соединен с первыми входами второго и третьего элементов ИЛИ-НЕ, вторые входы первого и второго элементов ИЛИ-НЕ 196, 197 соединены с входом второго разряда узла 203, входы с третьего по шестой 204, 205, 206, 207 разрядов которого подключены соответственно ко второму, третьему и четвертому входам третьего элемента ИЛИ-НЕ 188 и третьему входу второго элемента ИЛИ-НЕ 197, выходы которых подключены соответственно к первому и второму входам четвертого элемента ИЛИ-НЕ 199, третий вход которого подключен к выходу первого элемента ИЛИ-НЕ 196, выход четвертого элемента ИЛИ-НЕ 199 соединен с первым входом пятого элемента ИЛИ-НЕ 200, второй вход которого соединен со вторым выходом 208 узла и управляющим входом узла 209, третий выход которого 210 соединен с первым выходом узла 211 и выходом пятого элемента ИЛИ-НЕ 200.

Устройство реализовано на базовом матричном кристалле 1515ХМ1, причем занимает 65% площади кристалла.

Устройство может быть реализовано на микросхемах серии 133, 533, 555.

Н а п р и м е р: тридцатипятиразрядный регистр 1 - 533ИР2, первый и второй мультиплексоры 4,5 - 533ЛС2, блок задания режима 2, блок формирования признаков обнуления, блок хранения весовых коэффициентов 3, блок анализа старшего байта 16, с первого по третий 17,18,19 блоки анализа младших разрядов, шифраторы 20, 21 - 533ЛС2, 533ЛА8, 533ЛН2, 533ЛЕ10, 533ЛП11, узел прямого выделения единицы - 533ЛА9, 533ЛА8, 533ЛА7, 533ЛЕ2, узел обратного выделения единицы - 533ЛН2, 533ЛЕ5, 533ЛЕ6, 533ЛЕ10.

Устройство фиг. 1 предназначено для определения величины сдвига kj, kj+1, 2kj+2 и весовых коэффициентов для мультиплекативных алгоритмов вычисления функций, преобразования координат, поворота вектора. Мультиплекативные алгоритмы вычисления функций имеют вид

exp x, x∈ [0,1]

xj+1= xj-ln(1+εj2 )

)

yj+1= yj+εj2 yj

yj

Х0 = Х, Y0 = 1

lnx, x∈ [1/4,1]

xj+1= xj+εj2 xj

xj

yj+1= yj-ln(1+εj2 )

)

X0 = X, Y0 = 0 , x∈ [1/4,1]

, x∈ [1/4,1]

xj+1= xj + εj 2 xj + 2

xj + 2 xj

xj

yj+1= yj+ εj 2 yj

yj

X0 = X, Y0 = X

y/x, x∈ [1/4,1]

xj+1= xj+ εj 2 xj

xj

yj+1= yj+ εj yj

yj

X0 = X, Y0 = Y

arctg x, x∈ [0,1]

xj+1= xj- εj 2 uj

uj

uj+1= uj+εj2 xj

xj

yj+1= yj+ εj arctg 2

X0 = X, U0 = 1, Y0 = 0

arth x, x∈ [0,1]

xj+1= xj-εj2 uj

uj

uj+1= uj-εj2 xj

xj

yj+1= yj+εj· ln

X0 = X, U0 = 1, Y0 = 0

sin X, cos X, tgX, ctgX

xj+1= xj-εj2 arctg 2

Zj+1= zj-  yj - 2

yj - 2 zj

zj

yj+1= yj+ εj2 zj- 2

zj- 2 yj

yj

uj+1= uj- εj2 uj

uj

U0 = 1, X0 = X, Y0 = 0, Z0 = 1

sin X = Ys/Us tgX = Ys/Zs

cosX = Zs/Us ctgX = Zs/Ys

shX, chX, thX, cthX

xj+1= xj-εj ln

zj+1= zj+ εj2 yj + 2

yj + 2 zj

zj

yj+1= yj+ εj2 zj + 2

zj + 2 yj

yj

uj+1= uj- 2 uj

uj

U0 = 1, X0 = X, Y0 = 0, Z0 = 1

shX = Ys/Us thX = Ys/Zs

chX = Zs/Us cthX = Zs/Ys где Хj - значение аргумента в текущей j-ой итерации;

Zj, Uj, Yj - значения операндов в текущей j-ой итерации;

Xj+1 - значение аргумента, полученного в результате j-ой итерации.

Yj+1, Zj+1, Uj+1 - значения операндов, полученные в результате j-ой итерации.

εj=

Zs, Ys, Us - конечные значения операндов.

Для функций expX, sinX, cosX, tgX, ctgX, shX, chX, thX, cthX алгоритм определения Кj следующий. Если первый разряд тридцатипятиразрядного регистра 1 Xs= 0; в мантиссе аргумента определяется порядковый номер "К" старшей 1:0.00110101 и анализируется разряд, следующий за ней.

В случае комбинации 10, Кj = K, если 11, то Kj = К-1.

Если Xs = "1", то в мантиссе аргумента определяется порядковый номер "К" старшего 0: 1.111001 и анализируется разряд, следующий за ним. Если комбинация имеет вид 01, то Кj = K, если 00, то Кj=K-1. На последнем шаге Хкон примет значение, равное 0.(0.000 либо 1.111).

Для функций lnX, Y/X, алгоритм определения Кj следующий. Если Xs = 0, то в мантиссе аргумента определяется порядковый номер К старшего 0 и анализируется разряд, следующим за ним. Если 01, то Кj = К, если 00, то Кj = K - 1. Если Xs = 1, то определяется порядковый номер "К" старший 1 в мантиссе аргумента и анализируется следующий за ним разряд. Если 10, то Kj = K, если 11, то Кj = 11-1. На последнем шаге Хкон.примет значение, равное 1 (1.000 либо 0.111).

алгоритм определения Кj следующий. Если Xs = 0, то в мантиссе аргумента определяется порядковый номер К старшего 0 и анализируется разряд, следующим за ним. Если 01, то Кj = К, если 00, то Кj = K - 1. Если Xs = 1, то определяется порядковый номер "К" старший 1 в мантиссе аргумента и анализируется следующий за ним разряд. Если 10, то Kj = K, если 11, то Кj = 11-1. На последнем шаге Хкон.примет значение, равное 1 (1.000 либо 0.111).

Для функций arctg X, arthX алгоритм определения Кj следующий. Если Xs = 0, определяется в мантиссе аргумента порядковый номер К старшей 1 и Кj = K. Если Xs = 1, то определяется порядковый номер "К" старшего 0 и Кj = K.

На последнем шаге Хкон примет значение, равное 0(0.000 либо 1.111).

Для функций expX, sinX, cosX, tgX, ctgX, shX, chX, ctgX, thX.

εj= +1, если Xs = 0, εj= -1, если Хs = 1. Для остальных функций εj= +1, если Xs = 0, εj= -1, если Хs = 1.

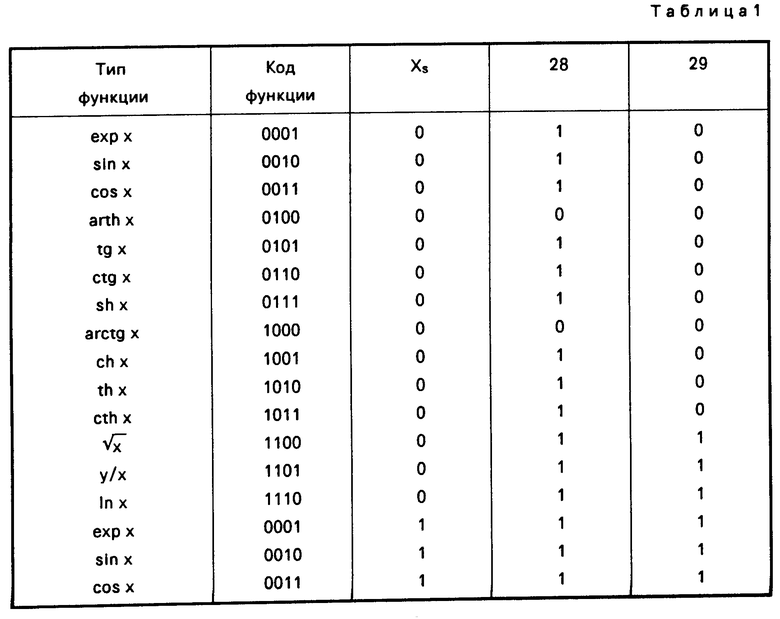

Блок задания режима 2 работает в соответствии с табл.1. фиг.1.

В зависимости от управляющего сигнала 29 первый мультиплексор 4 пропускает прямой (29 = 0), либо инверсный (29 = 1) код 3-х разрядной мантиссы входного кода, записанного в тридцатипятиразрядном регистре 1.

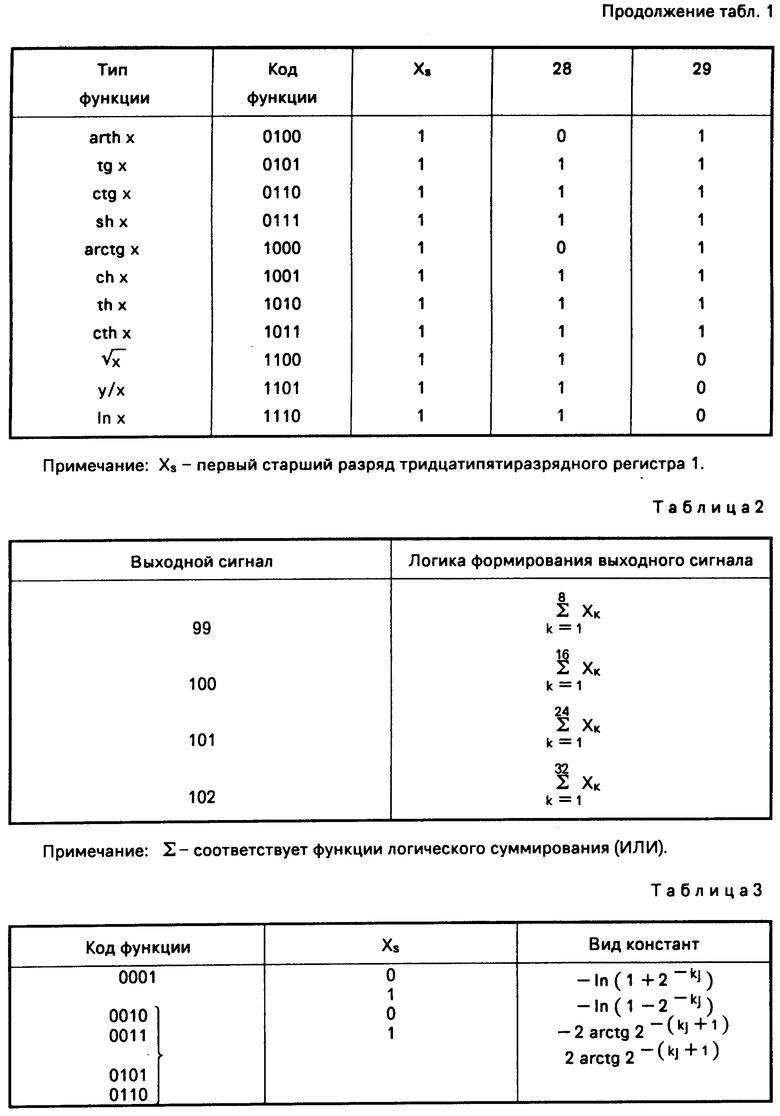

Прямые значения группы выходов 32-64 мультиплексора 4 поступают на вход блока формирования признаков обнуления 15, работающего в соответствии с табл.2.

На выходе блока анализа старшего байта 16, первого 17, второго 18, третьего 19 блоков анализа младших разрядов формируется унитарный код величины Кj, который поступает на вход первого 20 и второго 21 шифраторов для параллельного получения 5-разрядных значений Кj и Kj + 1. Причем для шифрации величины Kj + 1 достаточно сдвинуть унитарный код Kjна один разряд в сторону старших разрядов и подать на вход второго шифратора 21. Значения кода функции (5 разряда), знаковый разряд и величина Kj поступают на вход блока хранения весовых коэффициентов 3, где в соответствии с табл. 3 хранятся 36-разрядные весовые коэффициенты.

На информационные входы второго мультиплексора 5 одновременно поступают 5- разрядные значения Kj, Kj+1, 2Kj+2, причем 2 Kj + 2 формируется путем сдвига величины Kj+1 на один разряд в сторону старших разрядов. В зависимости от значений управляющих сигналов второго мультиплексора 5 на выходе устройства формируются либо Kj, либо Kj+1, либо 2Kj+2 в соответствии с табл.4.

Блок анализа старшего байта 16 формирует старшие девять разрядов унитарного кода Kj, причем первый разряд группы выходов блока анализа старшего байта принимает значение "1", если величина сдвига Kj = 0. Т.о. время формирования унитарного кода старшего байта не превышает суммарной задержки прохождения сигнала через узел прямого выделения единицы 112, четыре двухвходовых 105-108 элемента И-НЕ, три элемента ИЛИ-НЕ 109-111. Обозначим Xi i - разряд мантиссы входного кода на выходе первого мультиплексора 4. Тогда на шестиразрядне группы входов блоков прямого и обратного выделения единицы поступают значения в соответствии с табл.5.

Если "1" сформировалась на выходе старшего разряда унитарного кода, то с помощью элементов И-НЕ со второго 105 по пятый 108 и элементов ИЛИ-НЕ с первого 109 по третий 111 последовательно формируется сигнал запрета на прохождение "1" унитарного кода младших разрядов. Т.о. принцип формирования унитарного кода параллельно-последовательный. Параллельно посредством первого элемента И-НЕ, 101 с первого по четвертый блоками прямого и обратого выделения единицы 112-115, 116-119 формируются с первого по девятый разряды унитарного кода старшего байта. Последовательно формируется сигнал запрета, если в младшем разряде унитарного кода сформировалась "1". Последовательное чередование блоков прямого и обратного выделения единицы, элементов И-НЕ и элементов ИЛИ-НЕ позволяют избавиться от применения дополнительных инверторов в последовательной цепочке формирования сигналов запрета, что существенно повышает быстродействие.

Блок анализа младших разрядов фиг.3 в своем составе имеет узел анализа старшего байта 157 и восемь элементов И 149-156, которые пропускают унитарный код соответствующего байта только при условии, если на двадцать первом 178 входе блока анализа младших разрядов сформировался сигнал управления, равный "1". Если на двадцать первом входе 178 блока анализа 17, 18, 19 сформировался логический "0", то группа выходов 25, 26, 27 блока анализа 17, 18, 19 принимает нулевое значение.

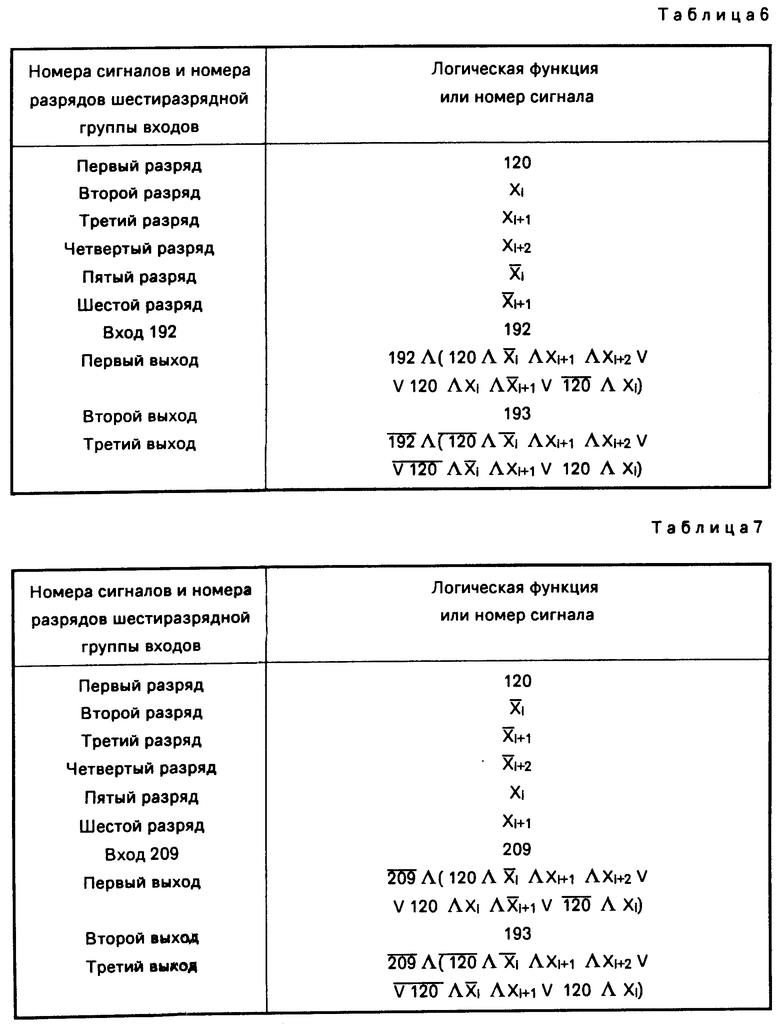

Узел прямого выделения единицы фиг. 4 предназначен для формирования на первом выходе 195 i-го разряда унитарного кода Kj .... Если Xii-разряд группы выходов первого мультиплексора 4, а  - его инверсное значение, то узел прямого выделения единицы формирует сигналы в соответствии с табл.6.

- его инверсное значение, то узел прямого выделения единицы формирует сигналы в соответствии с табл.6.

Узел обратного выделения единицы фиг. 5 предназначен для формирования на первом выходе 211 i-го разряда унитарного кода Kj. Если Xi i-разряд группы выходов первого мультиплексора 5, а  - его инверсное значение, то узел обратного выделения единицы формирует сигналы в соответствии с табл.7.

- его инверсное значение, то узел обратного выделения единицы формирует сигналы в соответствии с табл.7.

Устройство работает следующим образом. На информационный вход 12 устройства фиг. 1 поступает тридцатипятиразрядный входной код, на вход задания кода функции 14 устройства - код функции. По импульсу записи, поступающему на вход запуска 11 устройства, входной код записывается в тридцатипятиразрядный регистр 1. В зависимости от кода функции и старшего разряда входного кода блоком 2 задания режима вырабатывается сигнал 29, управляющий первым мультиплексором 4. Если сигнал 29 равен "1", то первый мультиплексор 4 пропускает инверсный тридцатичетырехразрядный выход 20 тридцатипятиразрядного регистра 1, если сигнал 29 равен "0", то первый мультиплексор 4 пропускает прямой тридцатичетырехразрядный выход 21 тридцатипятиразрядного регистра 1. Заметим, что первый старший разряд входного кода на информационные входы 20 и 21 первого мультиплексора 4 не поступает.

Прямые 32-64 инверсные 65-98 разряды группы выходов первого мультиплексора 4 поступают на соответствующие группы входов блока анализа старшего байт 16, с первого по третий блоков анализа младших разрядов 17, 18, 19. Причем прямые разряды 32-64 групп выходов первого мультиплексора также поступают на группу входов блока формирования признаков обнуления 15, выходы которого с первого по третий блокируют группы выходов с первого по третий блоков анализа 17, 18, 19 соответственно, если находятся в состоянии "0" и разрешают прохождениеа соответствующих сигналов, если находятся в состоянии "1".

Т.о. суть работы устройства состоит в параллельно-последовательном формировании унитарного кода величины сдвига Кj в пределах одного байта и параллельного формирования унитарных кодов каждого байта блоком анализа старшего байта 16, с первого по третий 17, 18, 19 блоками анализа младших разрядов. Разбиение на группы, в данном случае по 8 разрядов, т.е. побайтно, зависит от разрядности входного кода. А именно, с целью получения максимального быстродействия время параллельно-последовательного формирования унитарного кода в пределах группы должно быть равным времени формирования блокирующего сигнала младшей группы. В предлагаемом устройстве блокирующей сигнал младшей группы равен  и является третьим выходом блока формирования признаков обнуления 15.

и является третьим выходом блока формирования признаков обнуления 15.

Т. о., время формирования унитарного кода Kj равно времени формирования двадцатичетырехвходовой функции ИЛИ.

Первый выход 28 блока задания режима 2 управляет типом формирования унитарного кода Кj. Если сигнал 28 равен "1", то формирование Kj идет для функций arctgX, arcthX, если сигнал 28 равен "0", то для остальных функций.

Далее с помощью первого 20 и второго 21 шифраторов формируются пятиразрядные величины Kj, Kj+1, 2Kj+2, поступающие соответственно на первый 22, второй 23, третий 24 информационные входы второго мультиплексора 5. При появлении логической "1" на первом 8 или втором 9 или третьем 10 управляющих входах устройства на его информационном выходе 7 соответственно появляются.

Выход признака обнуления устройства 102 принимает значение, равное "1", если с первого по тридцать третий разряды 32-64 группы входов первого мультиплексора 4 находятся в состоянии логического "0".

На выходе весовых коэффициентов устройства 6 формируется соответствующий весовой коэффициент в зависимости от кода функции, старшего разряда входного кода и Kj.

Преимущества предлагаемого устройства по сравнению с прототипом заключаются в следующем:

- уменьшение количества управляющих сигналов, что повышает надежность работы устройства и простоту стыковки с другими устройствами;

- отсутствует динамический элемент счетчик, шестиразрядный сумматор;

- объем оборудования предлагаемого устройства несколько меньше объема оборудования прототипа;

- экономический эффект достигается за счет существенного повышения быстродействия по сравнению с прототипом. Минимальное время выдачи результата преобразования кода эквивалентно суммарной задержке двухвходового мультиплексора, двадцатичетырехвходовых операций ИЛИ, шифратора и трехвходового мультиплексора, которое в библиотечных элементах базового матричного кристалла 1515ХМ1 не превышает tΣиз= 120 нс. При этом суммарная задержка в прототипе равна задержке селектора, времени переключения счетчика из 0 в состояние 33, задержки регистра, блока определения длины сдвига, мультиплексора, шестиразрядного сумматора, которая в той же элементной базе составит tΣпр= 400 нс. При обработке 35 - разрядного входного кода в мультиплекативных алгоритмах быстродействие предлагаемого устройства по сравнению с прототипом увеличится в 3,3 раза

K=  =

=  = 3/3

= 3/3

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Устройство для предсказания четности результата сдвигателя | 1988 |

|

SU1649545A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных, управляющих и моделирующих системах как общего, так и специального назначения, использующих мультипликативные алгоритмы вычисления функций, преобразования координат, поворота вектора. Цель изобретения повышение быстродействия за счет параллельно-последовательной обработки входного кода. Быстродействие предлагаемого устройства повышается в 3 раза по сравнению с прототипом. 4 з.п. ф-лы, 5 ил., 7 табл.

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-02-09—Публикация

1990-04-12—Подача