Изобретение относится к вычислительной технике, а именно к классу арифметических устройств для вычисления трансцедентных функций, и может быть использовано в цифровых моделирующих, управляющих и вычислительных системах как общего, так и специального назначения.

Целью изобретения является расширение класса решаемых задач за счет возможности вычисления тригонометрических, гиперболических, логарифмической, степенной, показательной и функции отношения.

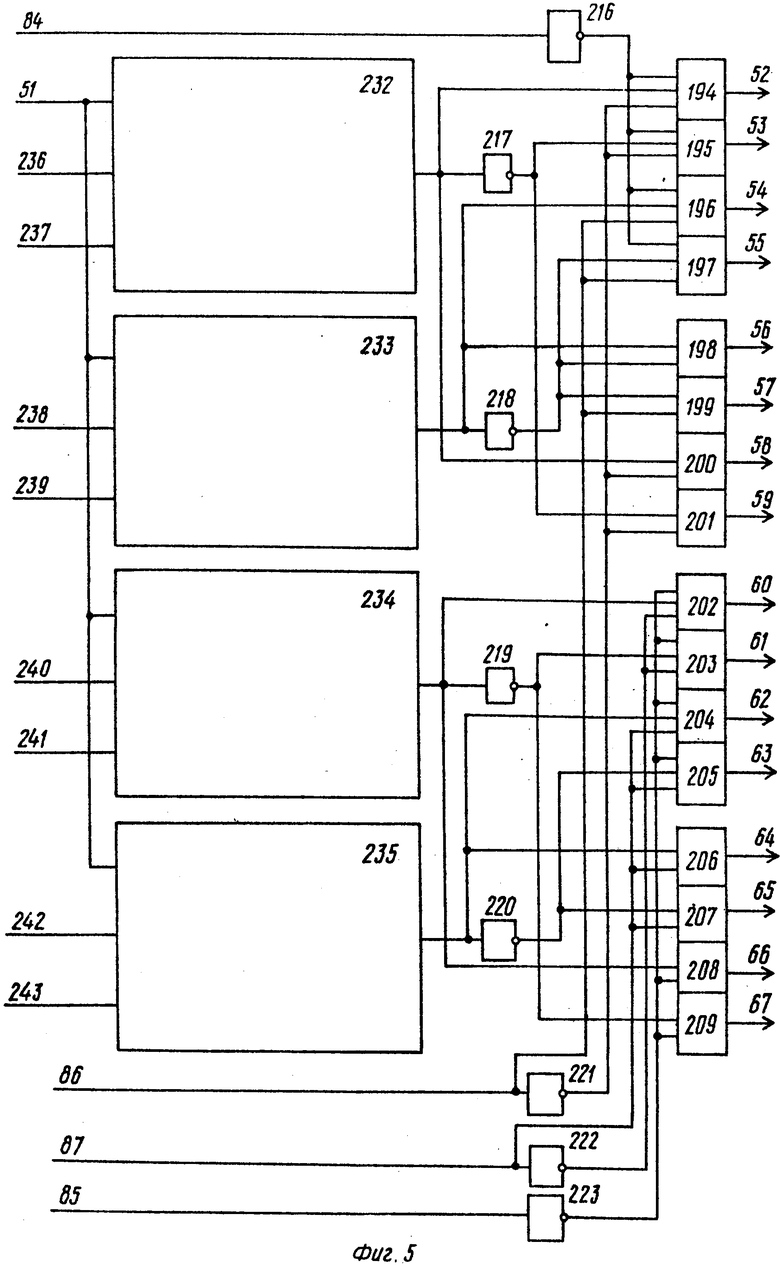

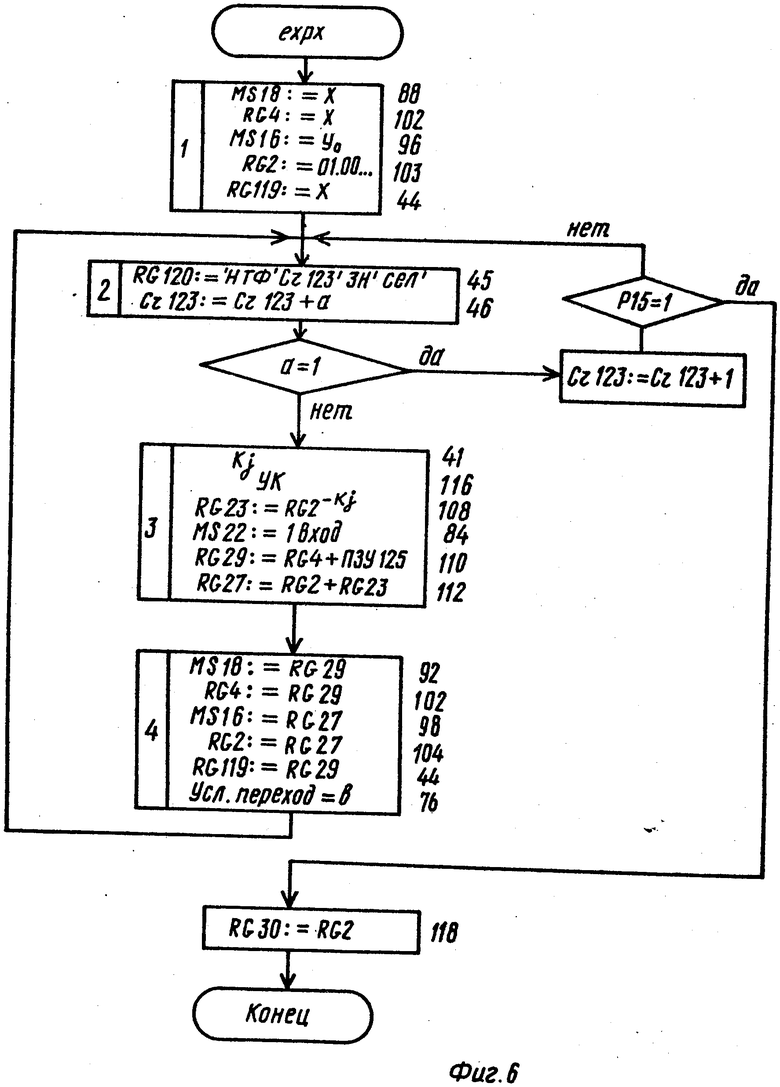

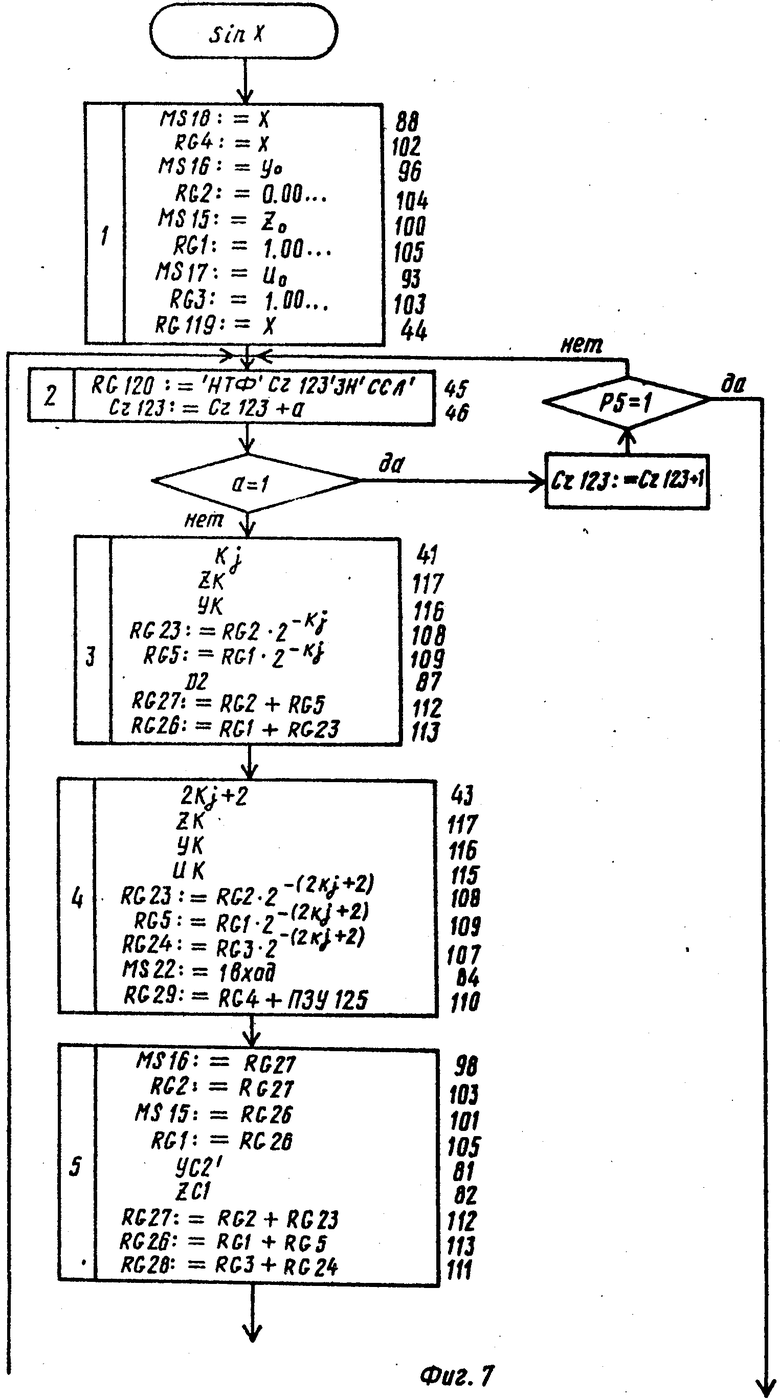

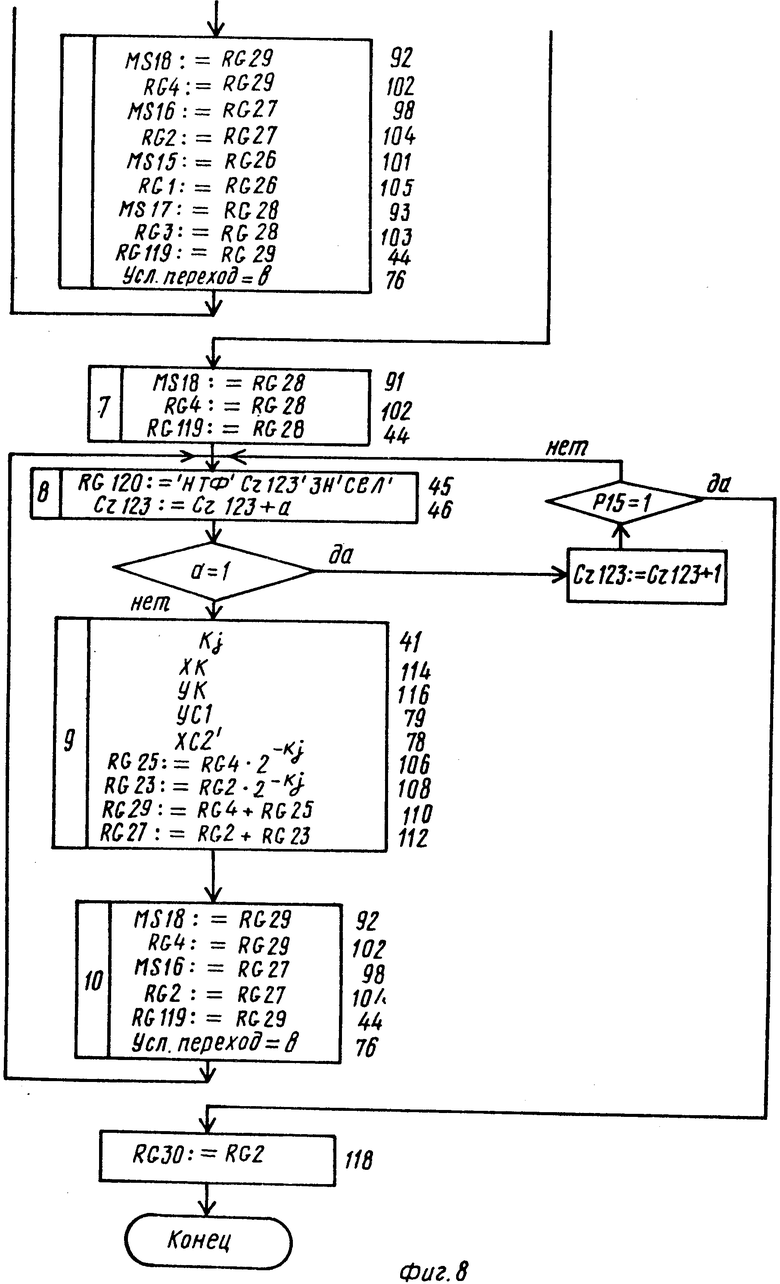

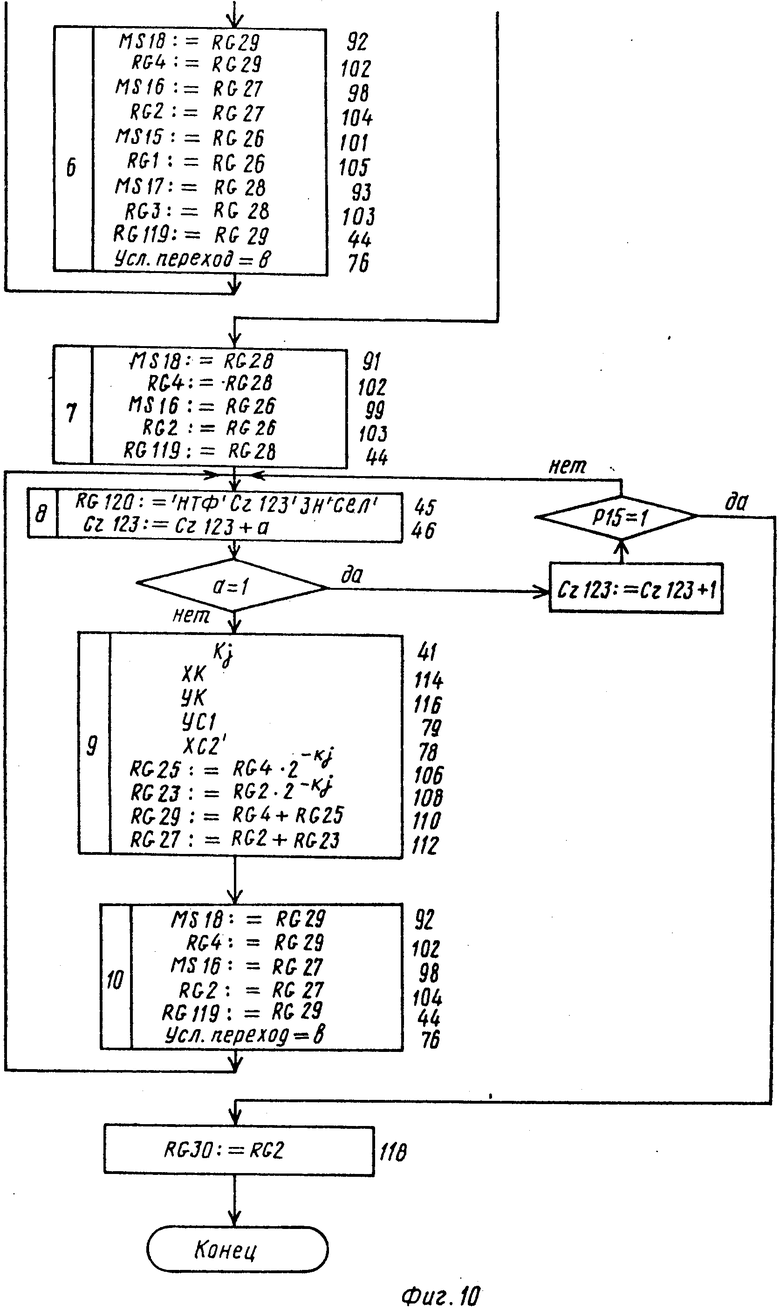

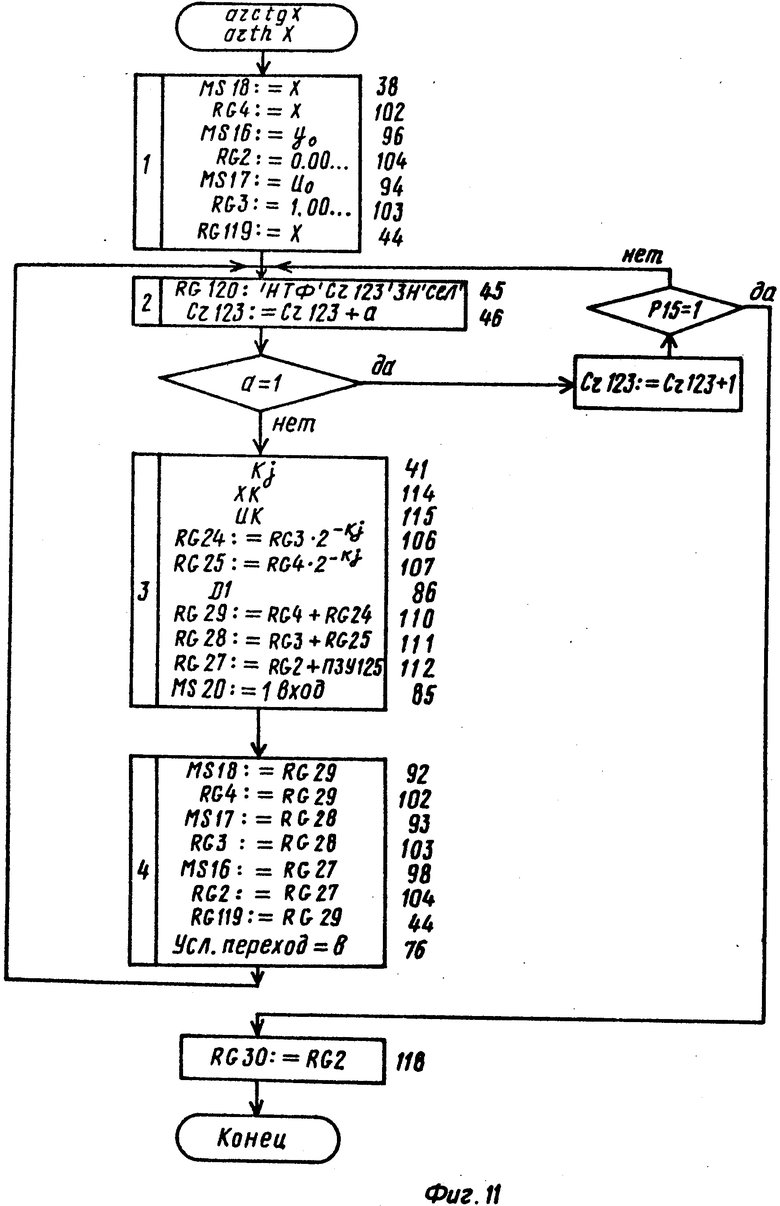

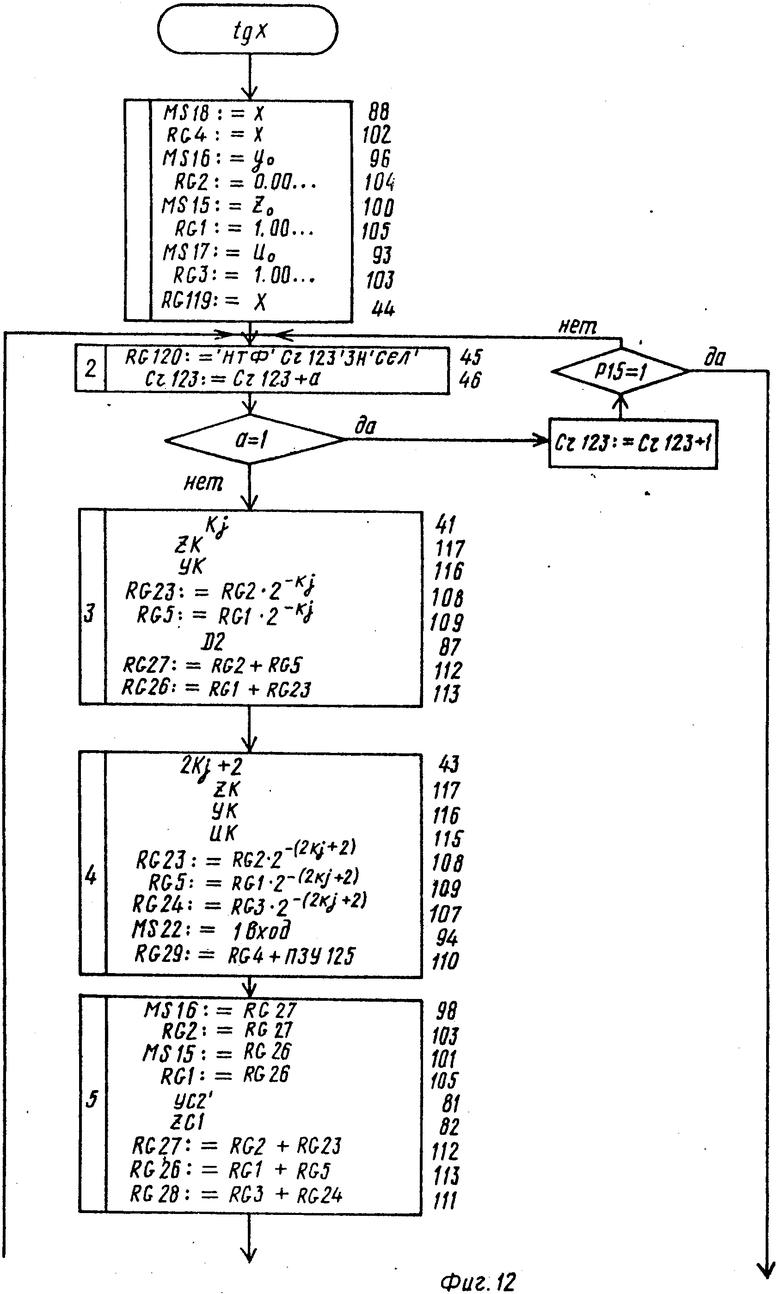

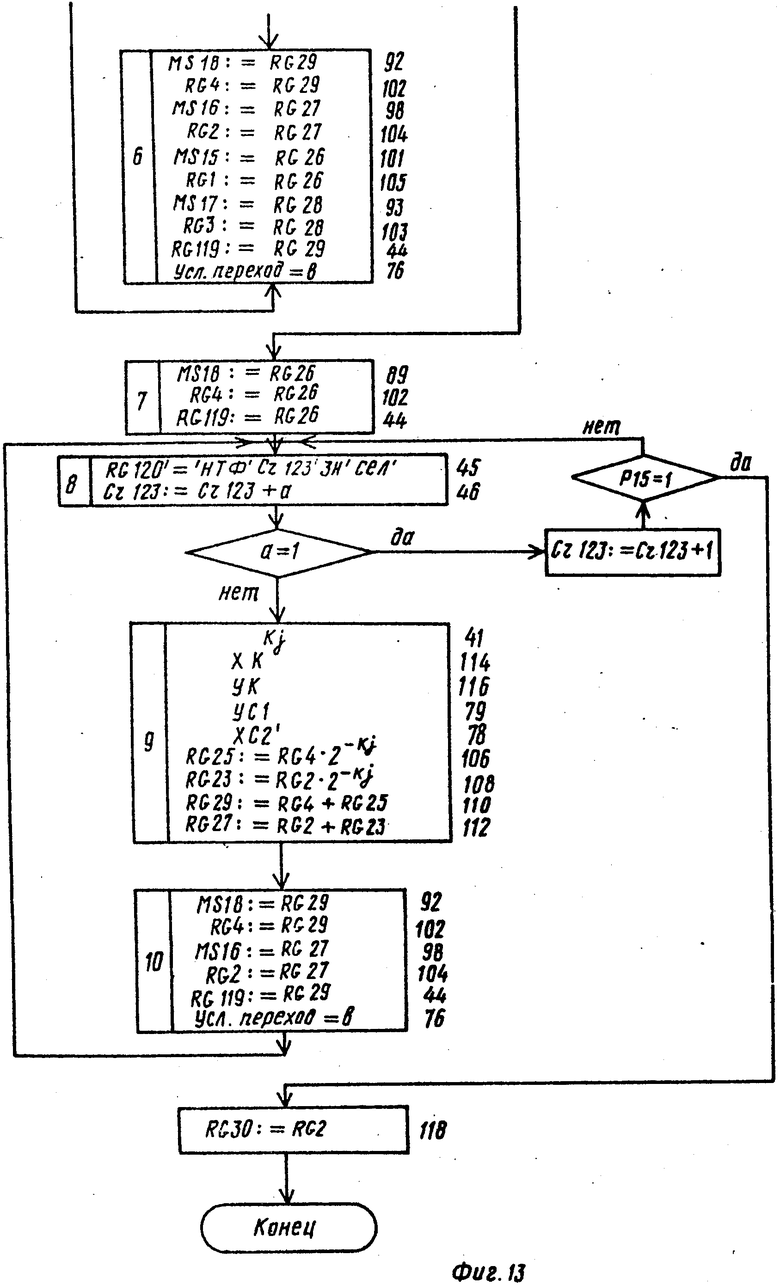

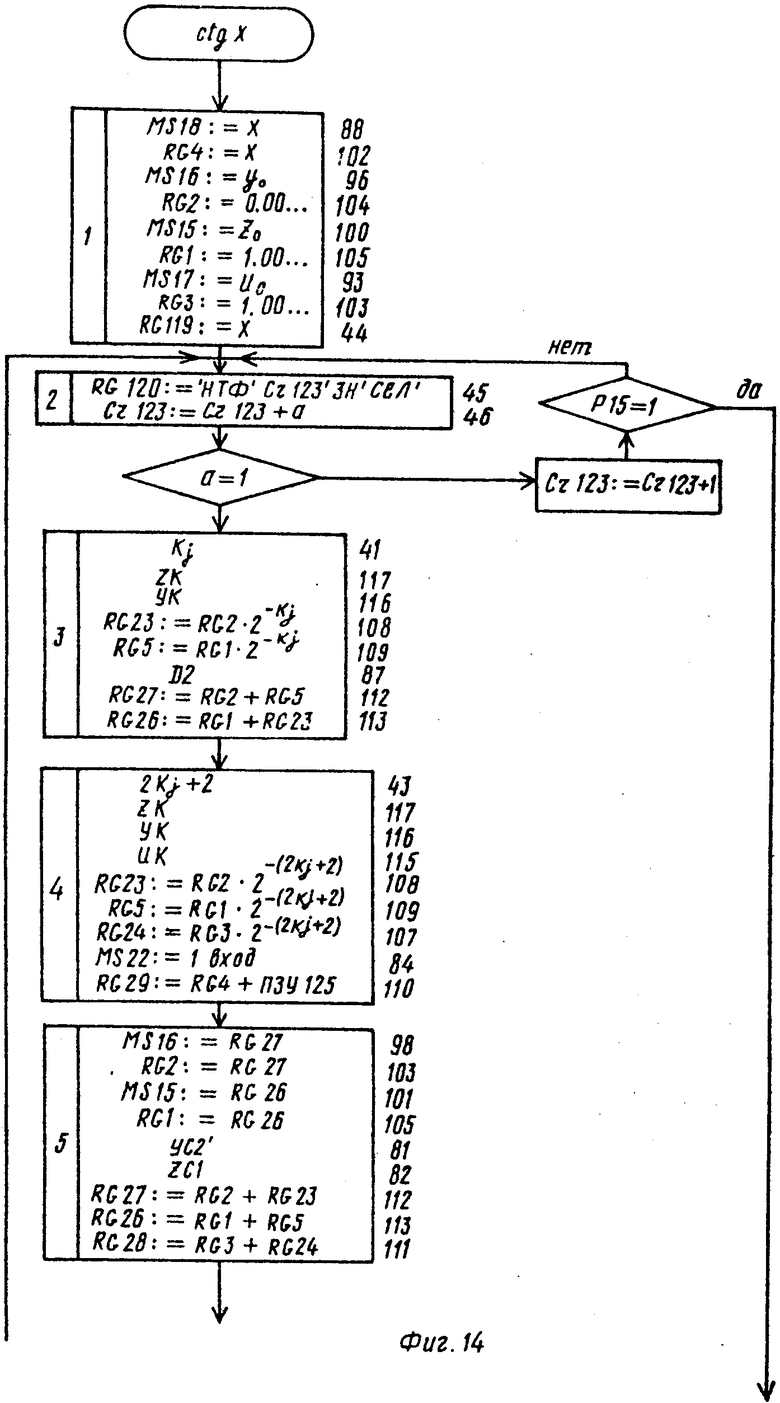

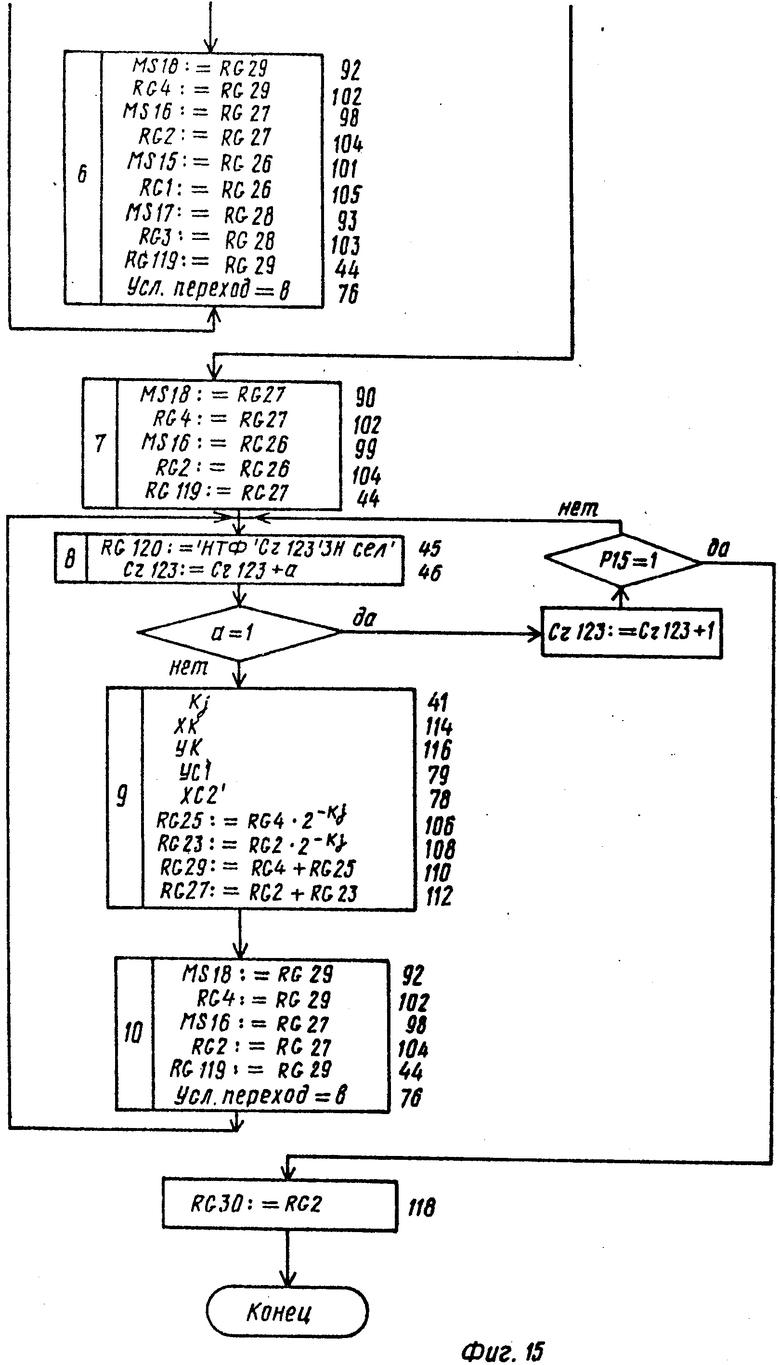

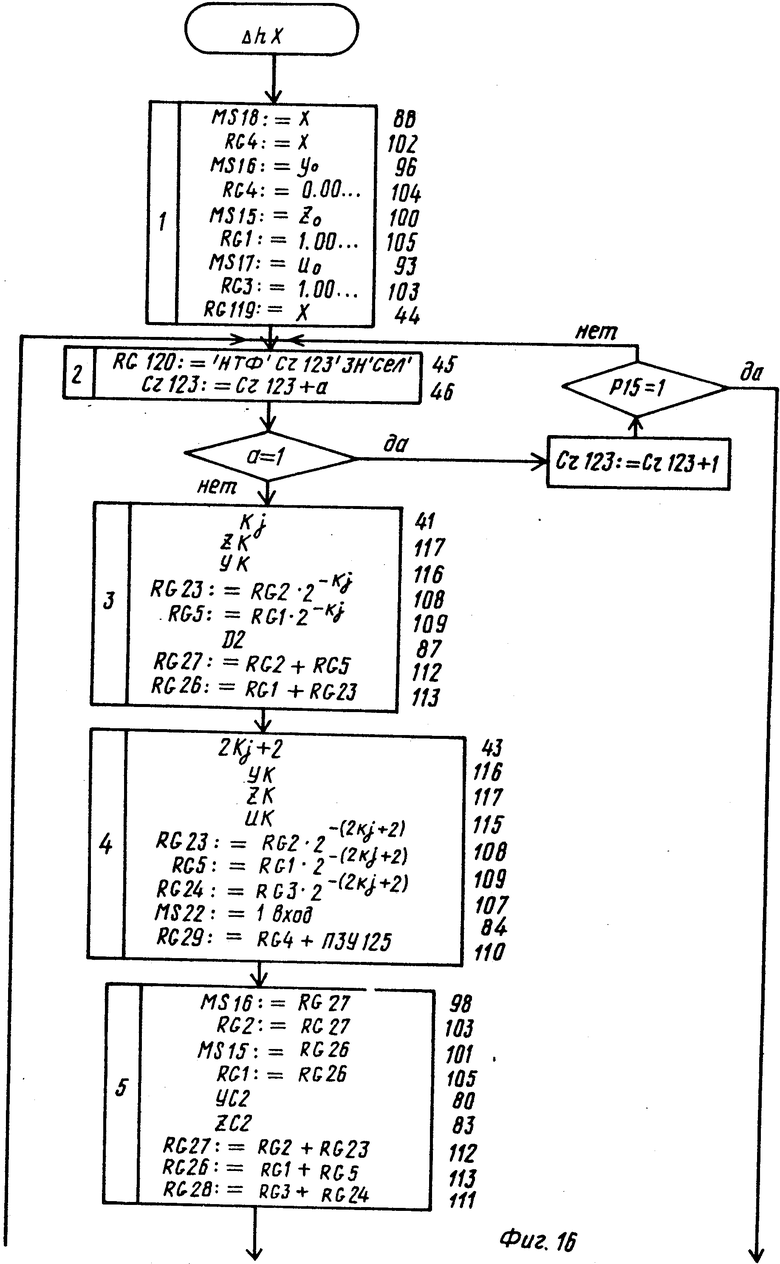

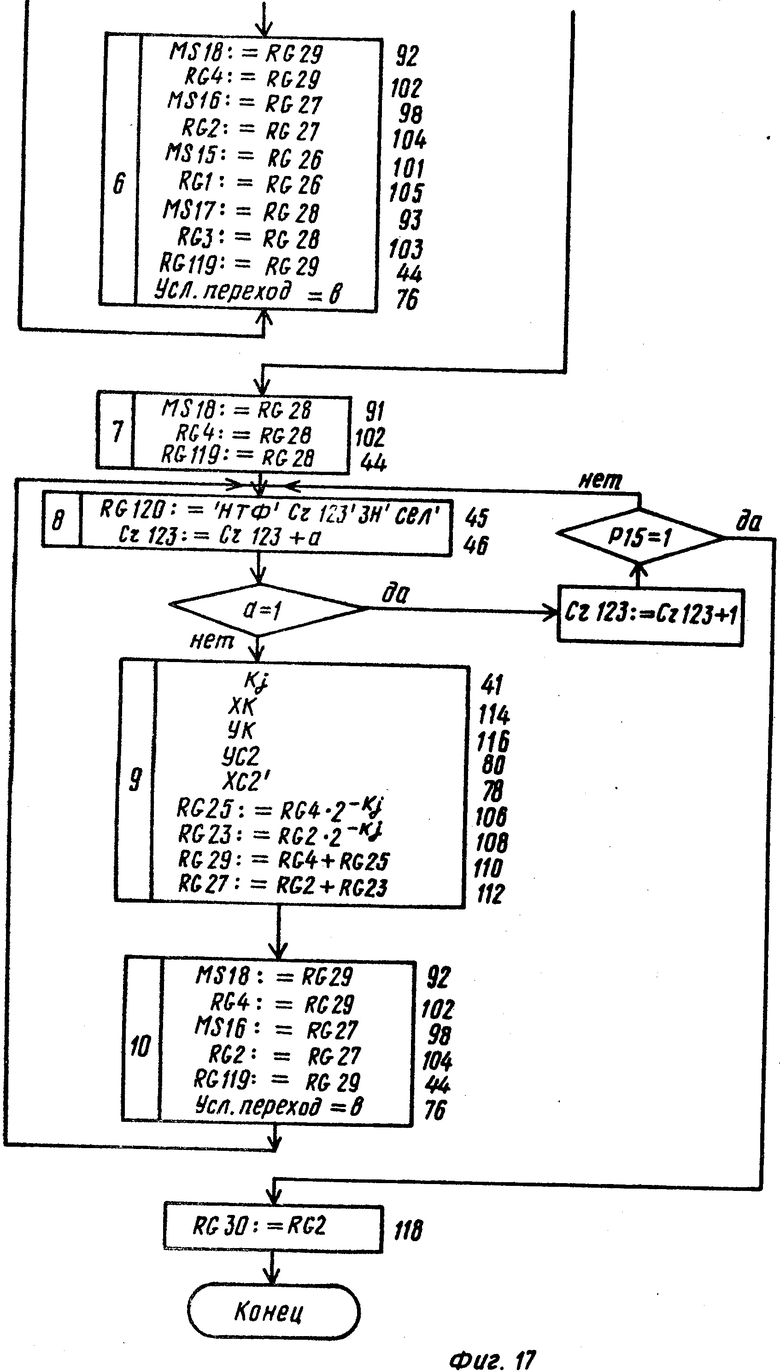

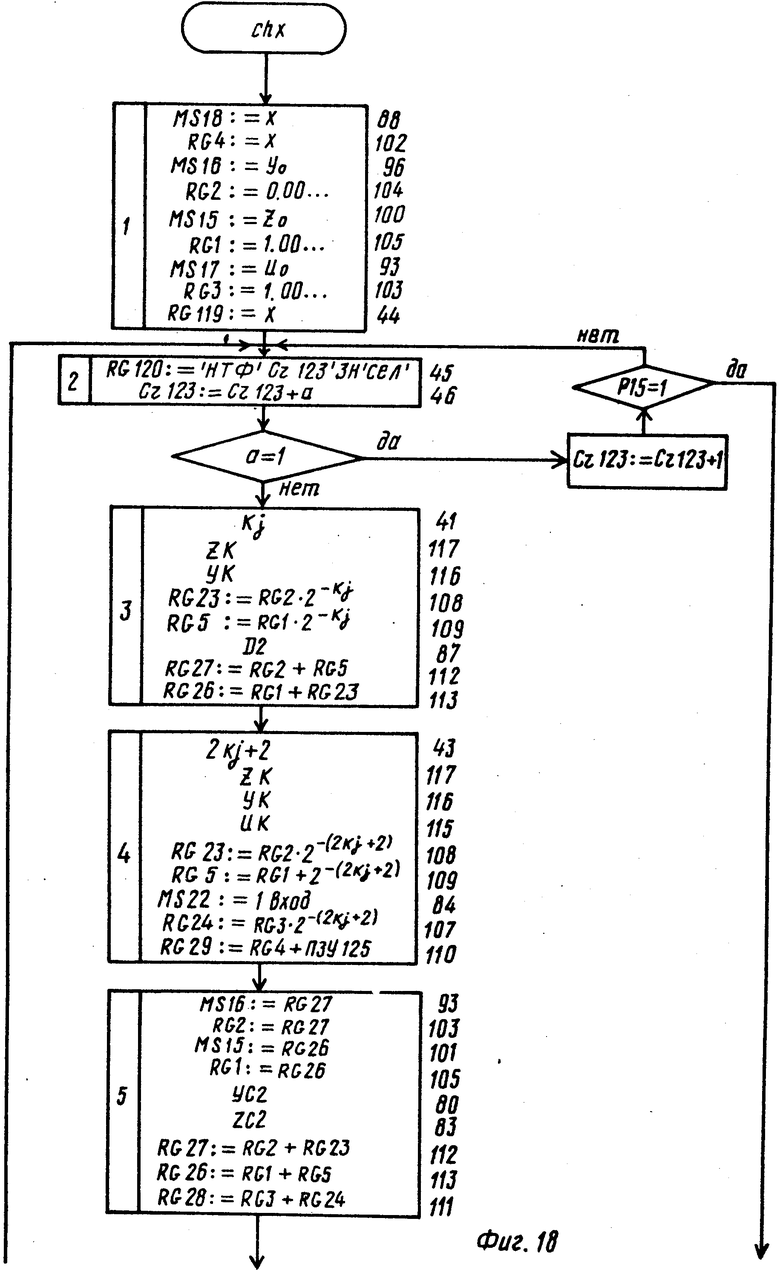

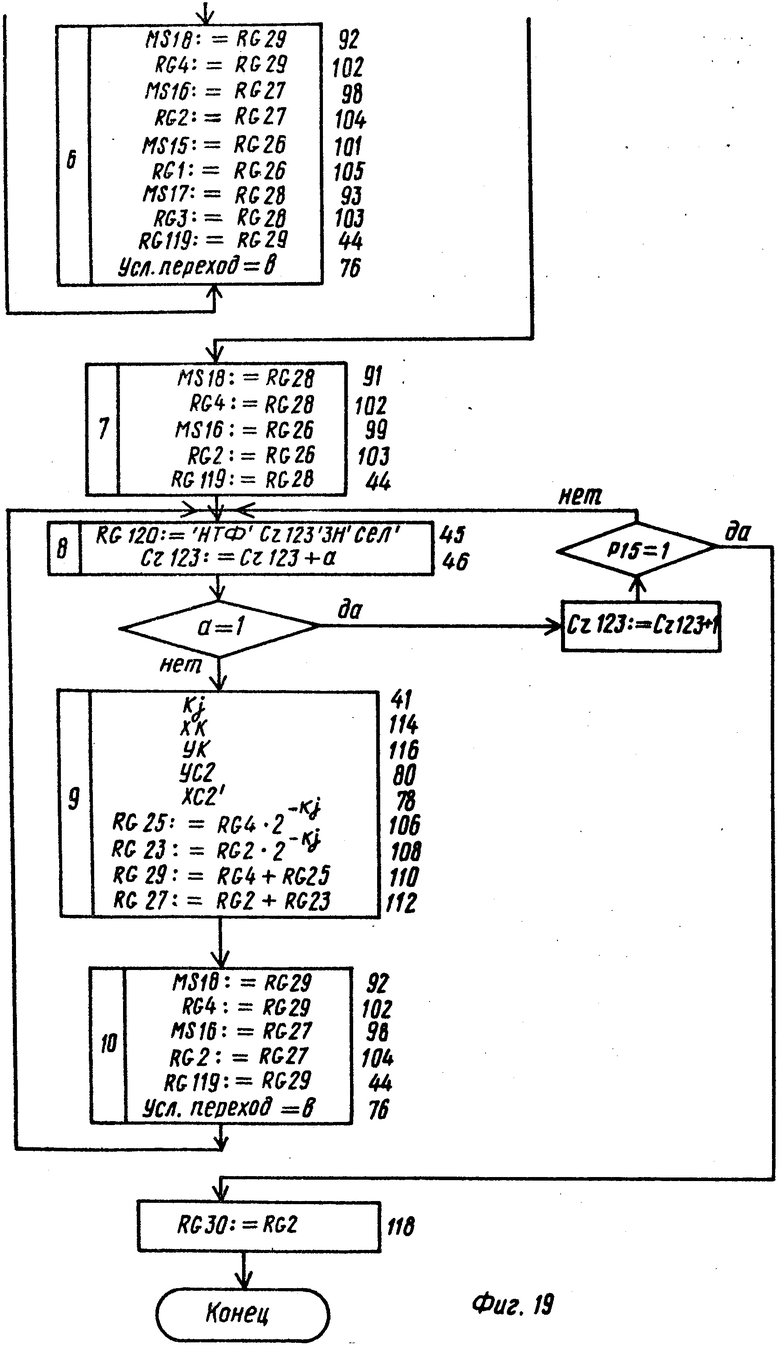

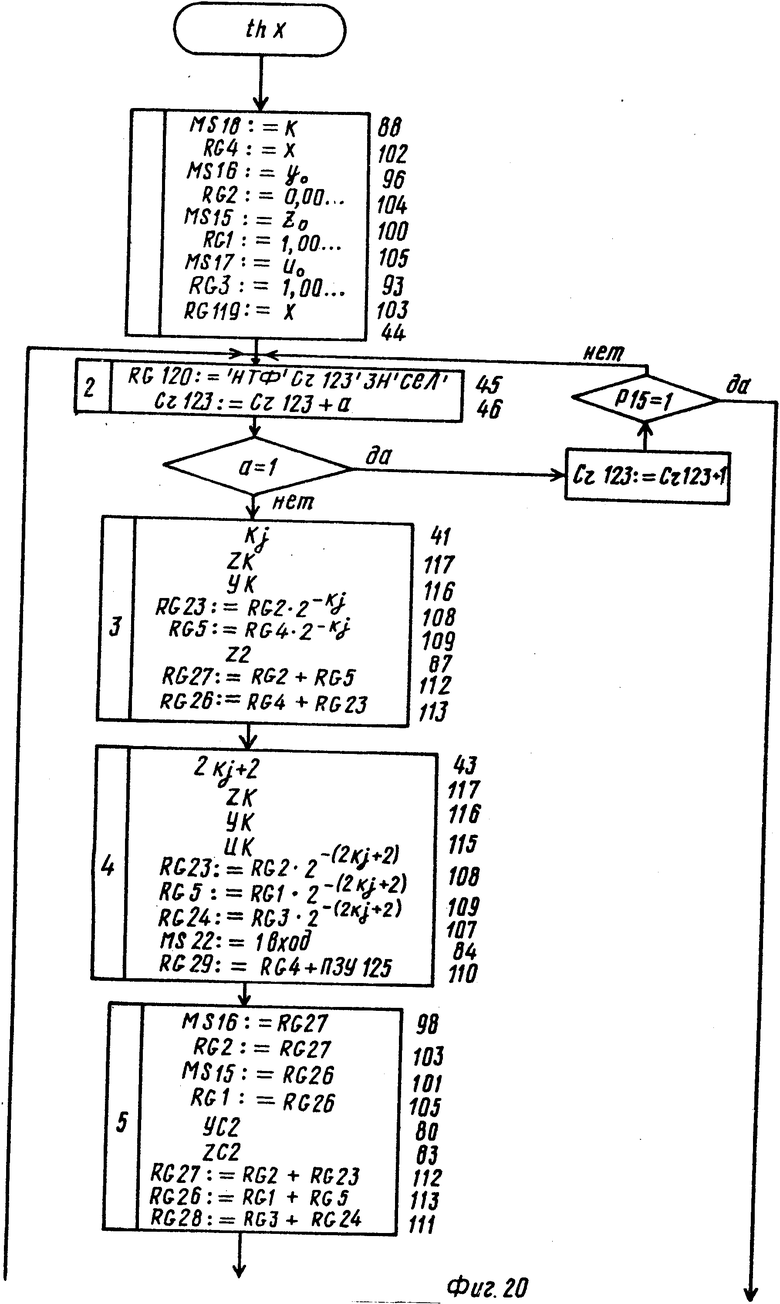

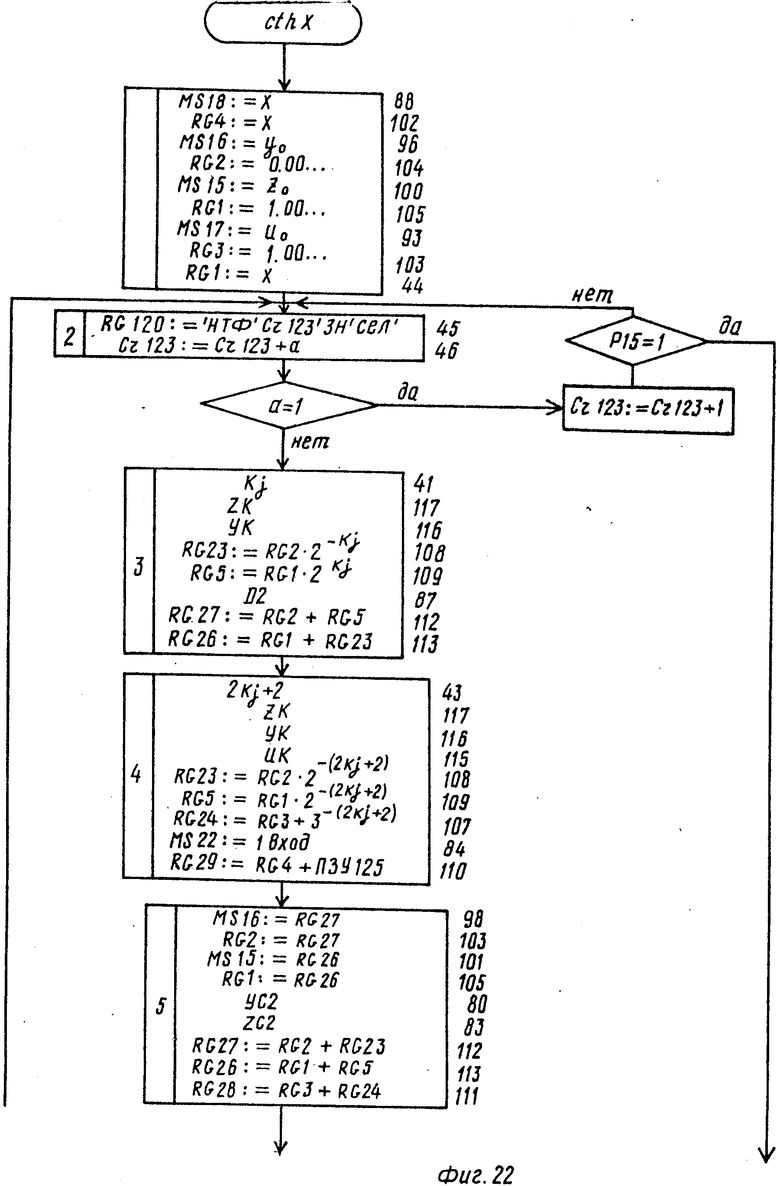

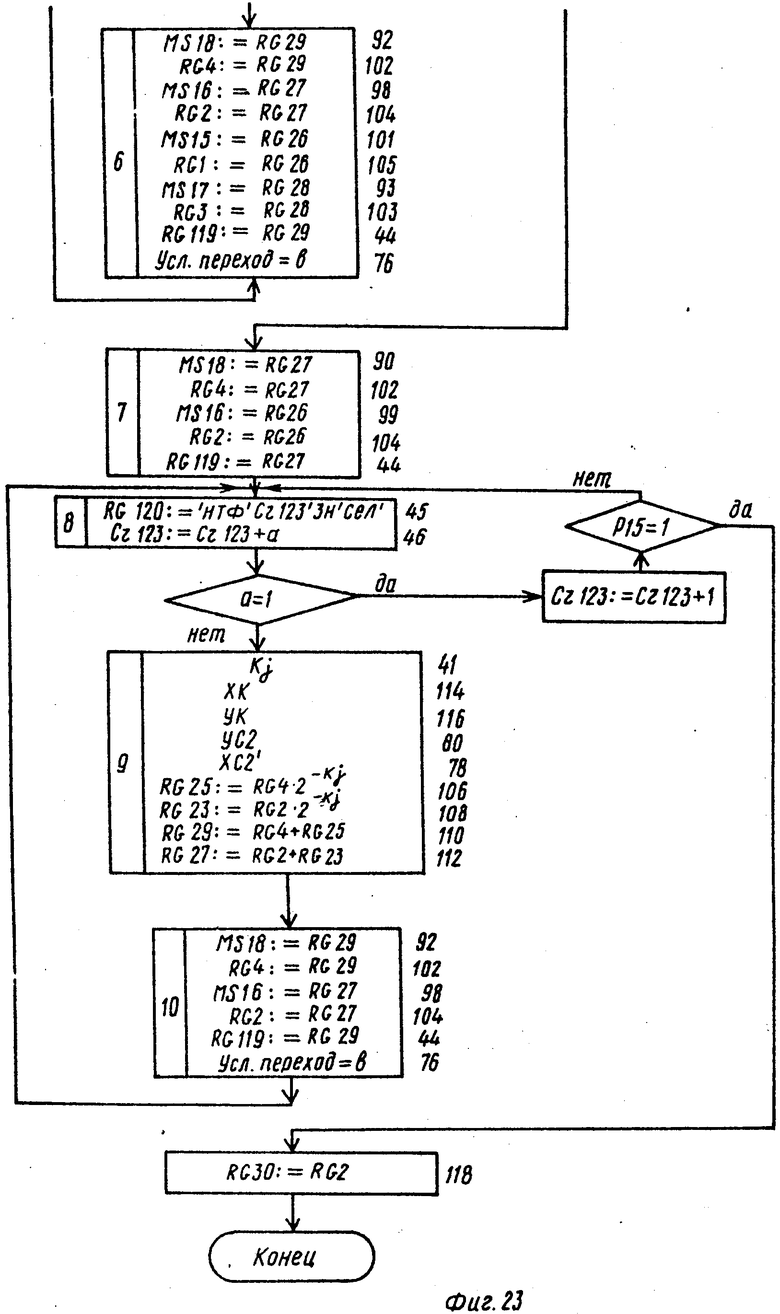

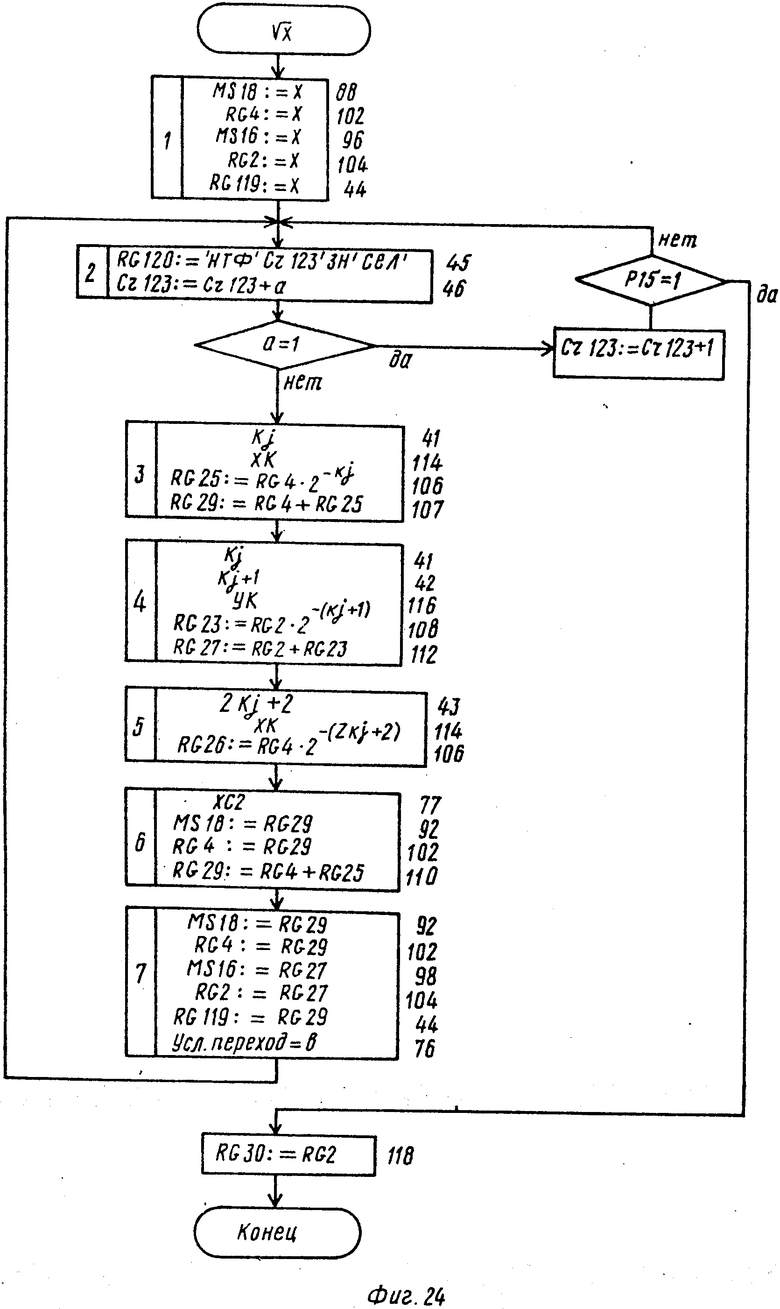

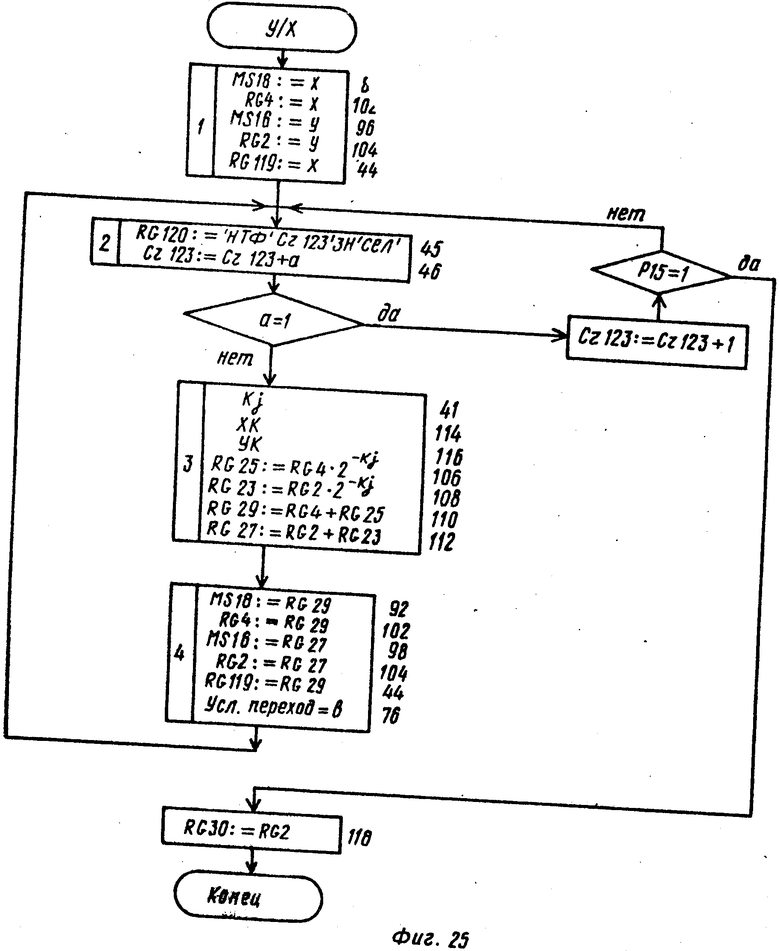

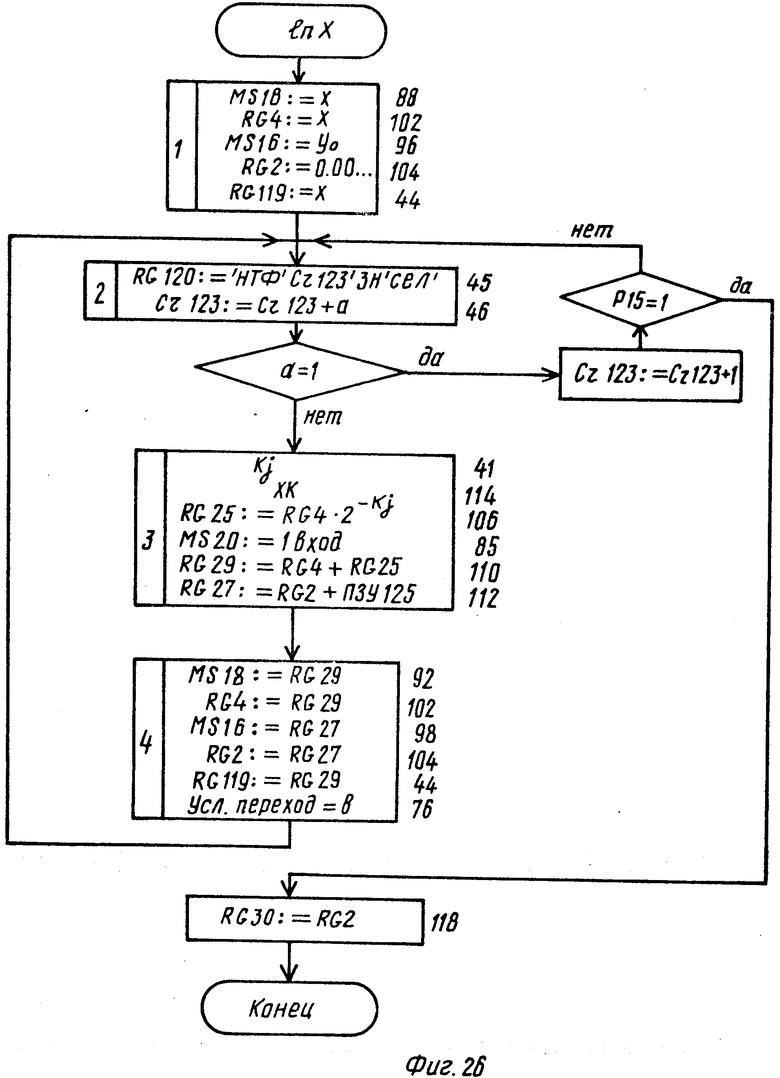

На фиг. 1 представлена структурная схема устройства: на фиг. 2 - структурная схема блока анализа аргумента; на фиг. 3 - структурная схема блока управления; на фиг. 4, 5 - структурная схема блока анализа знака; на фиг. 6 - структурная схема микропрограммы вычисления функции ехр(Х): на фиг. 7, 8 - структурная схема микропрограммы вычисления функции sin(X); на фиг. 9, 10 - структурная схема микропрограммы вычисления функции cos(X); на фиг. 11 - структурная схема микропрограммы вычисления функции arctg(X), arth(X); на фиг. 12, 13 - структурная схема микропрограммы вычисления функции tg(Х); на фиг. 14, 15 - структурная схема микропрограммы вычисления функции сtg(X); на фиг. 16, 17 - структурная схема микропрограммы вычисления функции sh(X); на фиг. 18, 19 - структурная схема микропрограммы вычисления функции ch(X); на фиг. 20, 21 - структурная схема микропрограммы вычисления функции tg(X); на фиг. 22, 23 - структурная схема микропрограммы вычисления функции cth(X); на фиг. 24 - структурная схема микропрограммы вычисления функции  ; на фиг. 25 - структурная схема микропрограммы вычисления функции Y/X; на фиг. 26 - структурная схема микропрограммы вычисления функции ln(X).

; на фиг. 25 - структурная схема микропрограммы вычисления функции Y/X; на фиг. 26 - структурная схема микропрограммы вычисления функции ln(X).

Устройство содержит регистры 1-5, сумматоры 6-9, блоки сдвига 10, 11, блок анализа знака 12, блок управления 13, вход пуска устройства 14, мультиплексоры 15-22, регистры 23-30, блоки сдвига 31, 32, блок анализа аргумента 33, блок формирования начальных условий 34, вход задания режима 35 блока управления, вход задания режима 36 блока анализа знака, вход задания режима 37 блока анализа аргумента, входы начальной установки 38-40 соответственно блока анализа аргумента, блока управления и блока анализа знака, первый информационный вход 41-46 блока анализа аргумента, вход признака аргумента 47-50 блока управления, вход признака аргумента 51 блока анализа знака, выходы 52-67 блока анализа знака, информационный выход 68 и второй информационный вход 69 блока анализа аргумента, информационный вход устройства 70, информационный вход 71 мультиплексора 18, выход 72 устройства, информационные входы 73-75 мультиплексора 18, выходы 76-118 блока управления.

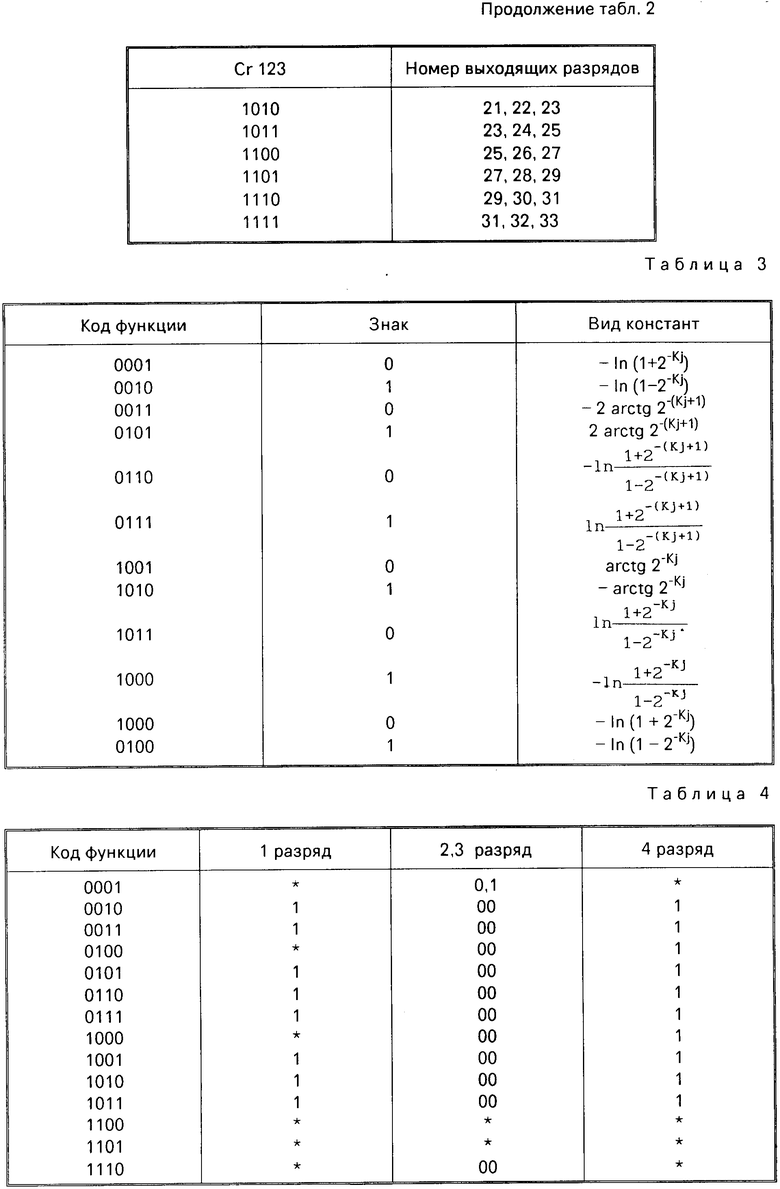

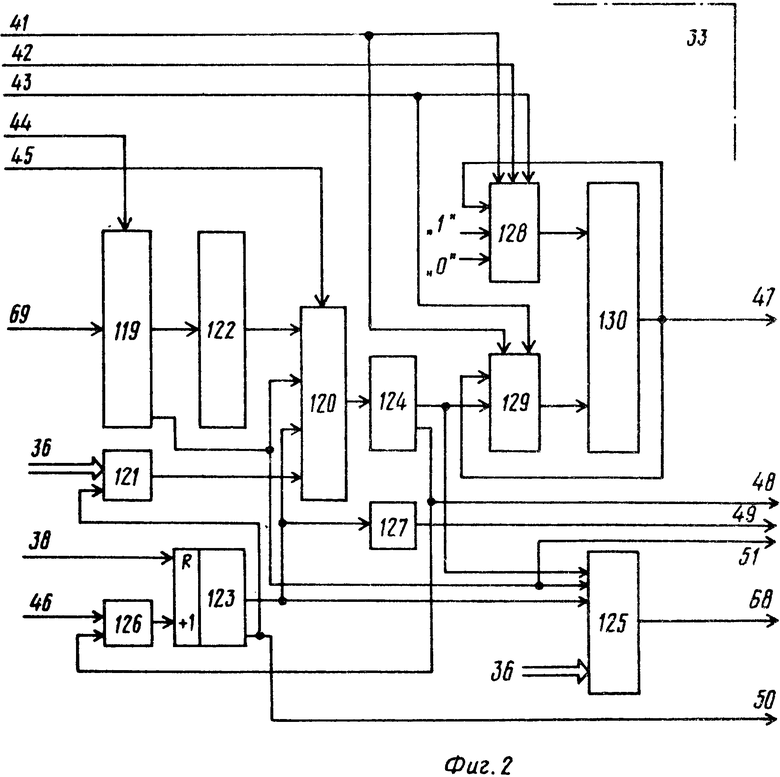

Блок анализа аргумента (см. фиг. 2) содержит регистры 119, 120, узел памяти кода функции 121, коммутатор анализируемых разрядов 122, счетчик 123, узел определения длины сдвига 124, блок памяти весовых коэффициентов 125, элементы И 126 и 127, мультиплексоры 128 и 129, сумматор 130.

Блок управления (см. фиг. 3) содержит элементы ИЛИ 131, 132, счетчик микрокоманд 133, узел памяти 134, регистр 135, триггер 136, генератор импульсов 137, узел формирования условного перехода 138, элементы И 139-160, группы элементов И 161-164, элемент задержки 165, элемент НЕ 166, формирователь синхросерий 167, дешифратор 168.

Блок анализа знака (фиг. 4, 5) содержит дешифратор 169, элементы ИЛИ 170-181, элементы И 182-209, элементы НЕ 210-223, триггеры 224-231, узлы формирования знака 232-235.

В основу работы устройства положены алгоритмы вычисления функций, построенные на общем мультипликативном подходе. Устройство позволяет вычислять следующие функции:

exp(X), ln(X),  , Y/X, arctg(X), arcth(X), sin(X), cos(X), tg(X), ctg(X), sh(X), ch(X), th(X), cth(X).

, Y/X, arctg(X), arcth(X), sin(X), cos(X), tg(X), ctg(X), sh(X), ch(X), th(X), cth(X).

Рекуррентные соотношения для перечисленных функций имеют следующий вид:

exp(X), X [0, 1]

Xj+1= Xj-ln(1+εj2 ) _→ 0..

) _→ 0..

Yj+1= exp(X)

exp(X)

X0 = X; Y0 = 1.

ln(X), X ∈ [1/4, 1]

Xj+1= 1

1

Yj+1= Yj-ln(1+εj2 ) _→ ln(X)..

) _→ ln(X)..

X0 = X, Y0 = 0.

, X∈[1/4,1]

, X∈[1/4,1]

Xj+1=

1

1

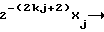

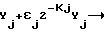

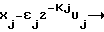

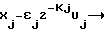

Yj+1= Yj+ εj2-(2kj+1)Yj_→

X0 = X, Y0 = X

Y/X, X ∈ [0,1]

Xj+1= 1

1

Yj+1= Y/X

Y/X

X0 = X, Y0 = Y

arctg (X), X ∈ [0,1]

Xj+1= 0

0

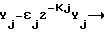

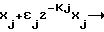

Uj+1=Uj +εj 2-Kj Xj

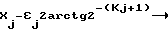

Yj+1= Yj+ εjarctg2-Kj_→ arctgX

X0 = X, Y0 = 0, U0=1

arth(X), X ∈ [0,097]

Xj+1= 0

0

Uj+1=Uj +εj 2-Kj Xj

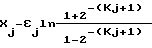

Yj+1= Yj+ εjln _→ arthX

_→ arthX

X0 = X, Y0 = 0, U0=1

sin(X), cos(X), tg(X), ctg(X), X ∈ [0,1]

Xj+1= 0

0

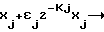

Zj+1= Zj-εj2-KjYj-2-(2Kj+2)Zj_→ Zs

Yj+1= Yj+εj2-KjZj-2-(2Kj+2)Yj_→ Ys

Uj+1= Uj+2-(2Kj+2)Uj_→ Us

X0 = X, Y0 = 0, U0=1, Z0=1

sin(X)=Ys/Us; tg(X)=Ys/Zs;

cos(X)=ZsUs; ctg(X)=Zs/Ys;

sh(X), ch(X), th(X), cth(X), X ∈ [0,1]

Xj+1= _→0

_→0

Zj+1= Zj-εj2-KjZj+2-(2Kj+2)Zj_→ Zs

Yj+1= Yj+εj2-KjZj+2-(2Kj+2)Yj_→ Ys

Uj+1= Uj-2-(2Kj+2)Uj_→ Us

X0 = X, Y0 = 0, U0=1, Z0=1

sh(X) = Ys/Us;

th(X) = Ys/Zs;

ch(X) = Zs/Us;

cth(X) = Zs/Ys, где Xj - значение аргумента в текущей j-й итерации;

Yj, Zj, Uj - значения операндов в текущей j-й итерации.

Zj+1 - значение аргумента, полученное в результате j-й итерации.

Yj+1, Zj+1, Uj+1 - значения операндов, полученные в результате j-й итерации.

ε =

Ys, Zs, Us - конечные значения операндов.

Процесс вычисления функции данным устройством сводится к заданию начальных значений вспомогательных величин Yo, Uo, Zo, аргумента Хо = Х, анализу аргумента Х с целью определения Кj в каждой j-й итерации. По результату анализа аргумента происходит сдвиг соответствующих величин на Кj, либо Kj+1, либо 2Кj+2 двоичных разрядов вправо (в сторону младших разрядов) и суммированию сдвинутого значения с несдвинутым, например Yj+1 = Yj + 2-Kj. Yj. По результату анализа из памяти извлекается соответствующая Kj константа вида ln(1 + εj +2-Kj), arctg 2-Kj , ln , которая суммируется со значением соответствующей величины, например

, которая суммируется со значением соответствующей величины, например

Xj+1 = Xj - ln(1 + εj 2-Кj), εj принимает значение + 1 либо -1 в зависимости от функции и знакового разряда аргумента Xj.

Для функций exp(X), sin(X), cos(X), tg(X), ctg(X), sh(X), ch(X), th(X), cth(X) алгоритм определения Kj следующий. Если знаковый разряд аргумента 3Н = 0, в мантиссе аргумента определяется порядковый номер К старшей 1: 0,00110101 и анализируется разряд, следующий за ней.

В случае комбинации 10, Кj = K, если 11, то Кj = K - 1.

Если знаковый разряд 3Н = "1", то в мантиссе аргумента определяется порядковый номер К старшего 0:1,111001 и анализируется разряд, следующий за ним. Если комбинация имеет вид 01, то Kj = К, если 00, то Kj = K - 1. На последнем шаге Хкон примет значение, равное 0 (0,000, либо 1,111).

Для функций ln(X), Y/X,  алгоритм определяется Kj следующий. Если целая часть аргумента ЦЧ = 0, то в мантиссе аргумента определяется порядковый номер К старшего 0 и анализируется разряд, следующий за ним. Если 01, то Кj = K, то 00, то Кj = K - 1. Если целая часть ЦЧ = 1, то определяется порядковый номер К старшей 1 в мантиссе аргумента и анализируется следующий за ней разряд. Если 10, то Кj = К, если 11, то Kj = K-1. На последнем шаге Хкон примет значение, равное 1(1,000, либо 0,111).

алгоритм определяется Kj следующий. Если целая часть аргумента ЦЧ = 0, то в мантиссе аргумента определяется порядковый номер К старшего 0 и анализируется разряд, следующий за ним. Если 01, то Кj = K, то 00, то Кj = K - 1. Если целая часть ЦЧ = 1, то определяется порядковый номер К старшей 1 в мантиссе аргумента и анализируется следующий за ней разряд. Если 10, то Кj = К, если 11, то Kj = K-1. На последнем шаге Хкон примет значение, равное 1(1,000, либо 0,111).

Для функций arth(X), arctg(X) алгоритм определения Kj следующий. Если знаковый разряд аргумента 3Н = 0 определяется в мантиссе аргумента порядковый номер К старшей 1 и Кj = К. Если 3Н = 1, то определяется порядковый номер К старшего 0 и Кj = К.

На последнем шаге Хкон примет значение, равное 0(0,000).

Для функций exp(X), sin(X), cos(X), tg(X), ctg(X), sh(X), ch(X), th(X), cth(X), arctg(X), arth(X) εj = +1, если 3Н = 0, εj = -1 если 3Н = =1. Для остальных функций εj = +1, если ЦЧ= = 0, εj = -1, если ЦЧ = 1.

Анализ двух разрядов с целью определения Кj позволяет сократить максимальное число итераций до n/2 и в 4 раза увеличить быстродействие предлагаемого устройства по сравнению с прототипом, где n - разрядность аргумента. Для обеспечения точности вычислений в n двоичных разрядов разрядность операндов и регистра должна составлять n + 1, где l ≅ log2n.

В устройстве разрядность операндов составляет 36 разрядов, при этом точность вычисления функции 32 двоичных разряда. Входной аргумент поступает с разрядностью 32, а в устройстве обрабатывается 36-разрядное поле 32 + 4, 4 младших разряда аргумента вначале заполняются нулями.

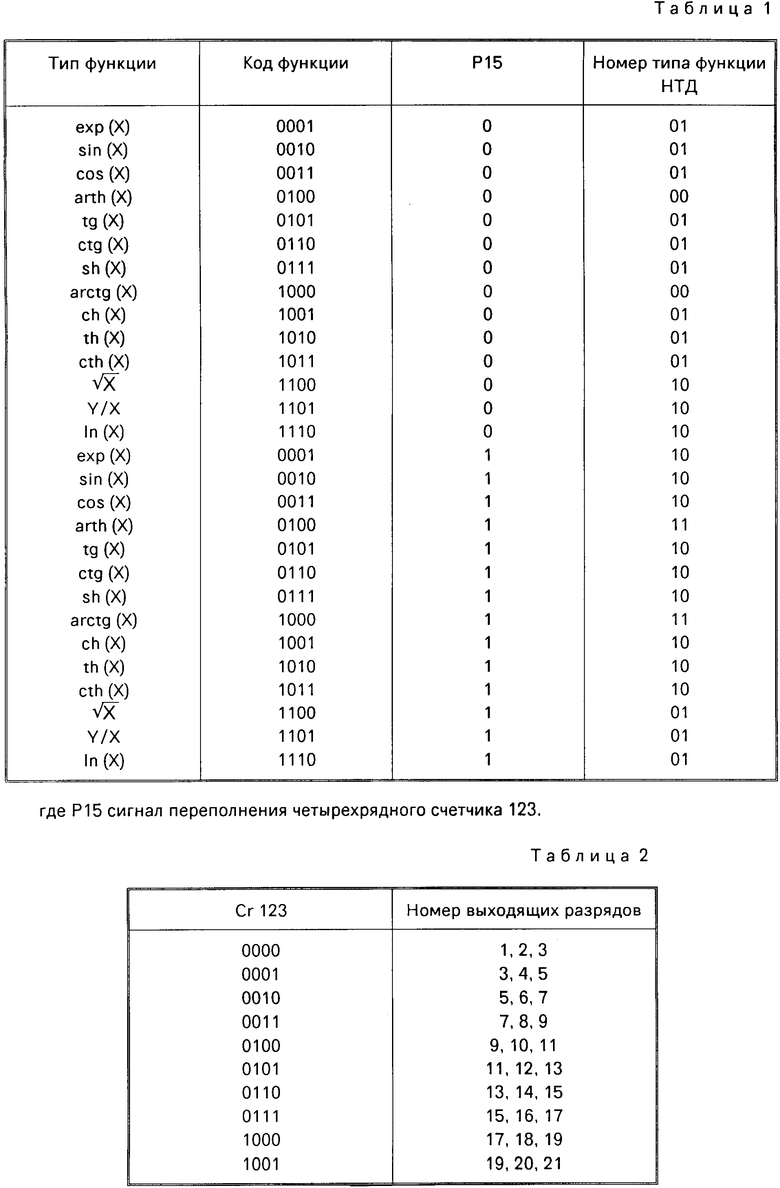

Узел памяти кода функции 121 работает в соответствии с табл. 1.

На вход коммутатора анализируемых разрядов 122 поступают n разрядов аргумента, на выходе коммутатора анализируемых разрядов в соответствии со значением счетчика 123 выделяются три разряда аргумента по правилу: 0,123456789101112...n.

В табл. 2 приведен пример соответствия показания счетчика 123 и номеров выходящих из коммутатора разрядов.

Формат десятиразрядного регистра 120 адреса блока определения длины сдвига имеет следующий вид: НТФ' Cr 123' 3H сел' (номер типа функции - 2 разряда, счетчик 123 - 4 разряда, знаковый разряд регистра 119 - 1 разряд или разряд целой части аргумента, выход коммутатора анализируемых разрядов 122 - 3 разряда).

Содержимое десятиразрядного регистра 120 адреса узла определения длины сдвига поступает на вход узла определения длины сдвига 124, с первого и второго выходов которого снимаются соответственно значения Кj, а. Вспомогательная величина а принимает значение "1" или "0".

В случае, если нужная комбинация разрядов не найдена и следует перейти к анализу следующих трех разрядов, величина а принимает значение "1". По совокупности сигналов из блока 13 управления 46 и а = 1, поступающих на вход элемента И 126, счетчик 123 к своему содержимому прибавляет единицу (Сr 123 = Сr 123 + 1) и переходит к анализу следующих трех разрядов аргумента. При а = 0 состояние счетчика 123 не меняется.

Узел определения длины сдвига 124 работает в соответствии со следующей логикой.

Обозначим К1, К2 соответственно старший и младший разряды номера типа функции, а1 - знаковый разряд аргумента, а2, а3, а4 - выходные разряды коммутатора анализируемых разрядов 122, где а2 - старший разряд, а4 - младший разряд, С1, С2, С3, С4- соответственно старшие и младшие разряды счетчика 123. Для понимания соотношений введем промежуточные величины Х1, Х2, Х3, Х4, Y2, Y3, Y4, K, Z5, Z6. Обозначим

"." - операция логического умножения.

"+" - операция логического сложения.

Х1 = а1

X2 = K1 +

+ a2

a2

X3 = K1 +

+ a3

a3

X4 = K1 +

+ a4

a4

Y2 = X1 +

+ X2

X2

Y3 = X1 +

+ X3

X3

Y4 = X1 +

+ X4

X4

a =

K =

Z5 =  Y3

Y3 +

+ Y3·Y4·K

Y3·Y4·K

Z6 = K·Y2+ Y2

Y2 +

+ Y

Y Y3·Y4

Y3·Y4

B1 = C2 ˙ C3 ˙C4 ˙ Z5 + C1 ˙ Z5 + C1˙ Z6

B2 = C2 ˙  ˙ Z5 +

˙ Z5 +  ˙ C3 ˙ C4 ˙ Z5 + C2 C3 ˙

˙ C3 ˙ C4 ˙ Z5 + C2 C3 ˙  ˙ Z5 + C2˙ Z6

˙ Z5 + C2˙ Z6

B3 = C3 Z5+

Z5+ C4·Z5+C3·Z6

C4·Z5+C3·Z6

B4 =  Z5+C4·Z6

Z5+C4·Z6

B5 = Z6

BO = 0, где Во - старший разряд, В6 - младший разряд величины сдвига Кj, а - значение вспомогательной величины, или условный переход четырехразрядного счетчика 123.

Величины Kj, Kj + 1, 2Kj+2 поступают в блок управления 13 с выхода шестиразрядного сумматора 130 последовательно во времени. На входы мультиплексора 128 поступают на третий ++ "0", второй - "1", первый - шестиразрядный выход сумматора 130. Соответственно на управляющие входы мультиплексора 128 сигналы из блока 13 управления К, К + 1, 2К +2. На входы мультиплексора 129 поступают Кj из узла определения длины сдвига 124 на второй вход, с выхода сумматора 130 на первый вход. Соответственно на управляющие входы сигналы К, 2К + 2. По совокупности сигналов из блока управления 13 К = 1(2К + 2 = 0, К + 1 = =0) на входы сумматора 130 поступают соответственно Кj, 0. С выхода сумматора 130 снимается значение Кj. По сигналам К = 1, К + 1 = 1, 2К + 2 = 0 на входы сумматора 130 поступают соответственно Кj, 1. С выхода сумматора 130 снимается значение (Kj + 1). По сигналам 2К + 2 = 1, К = 0, К + 1 = 0, на входы сумматора 130 поступают соответственно Кj + 1 и Kj + 1. С выхода сумматора 13 снимается значение (2Кj + 2).

Значения кода функции (4 разряда), знаковый разряд аргумента (1 разряд), Кj (5 разрядов) поступают на вход узла памяти весовых коэффициентов 125, где в соответствии с табл. 3 хранятся 36-разрядные весовые коэффициенты.

Тридцатишестиразрядный выход узла памяти весовых коэффициентов 125 поступает на первые информационные входы мультиплексоров 20, 22.

Четыре разряда счетчика 123 поступают на вход элемента И 127 выход которого обозначенный 49 поступает в блок 13 управления.

Обозначим сигналы с выходов триггеров 224-231 соответственно ХС1, ХС2, ИС1, ИС2, YC1, YC2, ZC1, ZC2.

Сигнал с выхода блока 12 управления соединен с соответствующими входами элементов И 184, 185, 190-190 и ИЛИ (180, 181). Сигнал с блока 13 управления XC1упр. (77), ХС2упр. (78), YC1упр. (79), YC2упр. (80), YC2упр (81) соединены с соотвествующими входами элементов ИЛИ (175-179), ZC1упр (82) - с S-входом триггера 230, ZC2упр. (83) - с R-входом триггера 231. Сигналы с выходов триггеров 224-231 совместно со знаковым разрядом (51) соединены со входами узлов формирования знака 232-235, работающих в соответствии с выражением

А = 3Н ˙ С1 + СН ˙ 2С, где А - выход узла формирования знака.

Сигналы С1, С2 являются соответственно выходами пар триггеров 224, 225, 226, 227, 228, 229, 230, 231.

При А = 0 передается прямой код числа, при А = 1 - дополнительный код числа мультиплексорами 19, 20, 21, 22.

С первого (52-67) по шестнадцатый выходные сигналы блока 12 анализа знака вырабатываются в соответствии с логическими выражениями

Вых 52 = вых232 MS2

MS2

Вых 53 = вых D1

D1

Вых 54 = вых233·D1

Вых 55 = вых D1

D1

Вых 56 = вых 233 ˙ D1

Вых 57 =  D1

D1

Вых 58 = вых 233

Вых 59 =  D1

D1

Вых 60 = вых 234·D2

Вых 61 =  D2

D2

Вых 62 = вых 235·D2

Вых 63 =  D2

D2

Вых 64 = вых 235 ˙ D2

Вых 65 = вых 235 ˙ D2

Вых 66 = вых 234

Вых 67=  где D1 - сигнал, включающий перекрестную связь между седьмым 24 и восьмым 25 регистрами, D2 - сигнал, включающий перекрестную связь между пятым 5 и шестым 23 регистрами, XMS2 - управляющий сигнал, включающий первый информационный вход восьмого 22 мультиплексора, YMS2 - управляющий сигнал, включающий первый информационный вход шестого 20 мультиплексора.

где D1 - сигнал, включающий перекрестную связь между седьмым 24 и восьмым 25 регистрами, D2 - сигнал, включающий перекрестную связь между пятым 5 и шестым 23 регистрами, XMS2 - управляющий сигнал, включающий первый информационный вход восьмого 22 мультиплексора, YMS2 - управляющий сигнал, включающий первый информационный вход шестого 20 мультиплексора.

Блоки сдвига 10, 11, 31, 32 функционируют в соответствии с логикой

X )0+Xn-1(Kj)o= X

)0+Xn-1(Kj)o= X

X )1+Xn-20·(Kj)1= X

)1+Xn-20·(Kj)1= X

X )2+Xn-41·(Kj)2= X

)2+Xn-41·(Kj)2= X

X )3+Xn-82·(Kj)3= X

)3+Xn-82·(Kj)3= X

X )4+Xn-163·(Kj)4= X

)4+Xn-163·(Kj)4= X

Xn )5+Xn-324·(Kj)5= X

)5+Xn-324·(Kj)5= X

(Kj)0,1,2,3,4,5 - первый-шестой управляющие входы блока сдвига, где (Kj)1 - младший разряд величины сдвига Кj; Xn0, Xn1, X02, Xn3, Xn4 - промежуточные значения n-х разрядов, Xn5 - выходное значение n-го разряда блоков сдвига 10, 11, 31, 32, причем при сдвиге старше разряды заполняются нулями.

Блок управления 13 работает следующим образом. По сигналу "Пуск" деблокируется генератор импульсов 137, выход которого поступает на вход блока 167 формирования синхросерий. На выходе блока 167 формируются три синхросерии Ф1, Ф2, Ф3. Код вычисляемой функции поступает на дешифратор 168, с выхода которого снимается сигнал, устанавливающий триггер 136 через элементы ИЛИ 131, И 142, 143, либо в "0", либо в "1".

Блок управления 13 работает следующим образом. По сигналу "Пуск" деблокируется генератор импульсов 137, выход которого поступает на вход блока 167 формирования синхросерий. На выходе блока 167 формируются три синхросерии Ф1, Ф2, Ф3. Код вычисляемой функции поступает на дешифратор 168, с выхода которого снимается сигнал, устанавливающий триггер 136 через элементы ИЛИ 131, И 142, 143, либо в "0", либо в "1".

При вычислении функций sin(X), cos(X), tg(X), ctg(X), sh(X), ch(X), th(X), ctg(X), триггер 136 устанавливается по сигналу 39 в "0", при вычислении остальных функций в "1".

Выход триггера 136 поступает на вход элемента И 145 совместно с седьмым 50 входом блока 13 управления, который является сигналом переноса Р15 счетчика 123. Выход элемента И 145 поступает на управляющий вход тринадцатого регистра 30, в который записывается результат вычисления и элемент 165 задержки на блокировку генератора 137 функции. Переключение триггера 136 из "0" в "1" осуществляется по сигналу с выхода элемента И 144, на вход которого поступает сигнал переноса счетчика 123 и выход элемента ИЛИ (131), таким образом для функций ln(X), exp(X),  , Y/X, arctg(X), artg(X) запись результата в выходной регистр происходит по первому переносу счетчика 123, для остальных функций - по второму переносу счетчика 123. Счетный вход счетчика микрокоманды 133 соединен с первой фазой Ф1 блока формирования синхросерий 167. Выход счетчика 133 совместно с кодом функции поступает на адресный вход блока памяти микрокоманд 134, содержимое которого записывается в регистр микрокоманд 135 третьей фазой ФЗ. На вход блока 138 формирования номера условного перехода поступает четырехразрядный код условного перехода с регистра микрокоманд 135 и выходной сигнал элемента И 139. Узел 138 формирования номера условного перехода работает в соответствии с логикой

, Y/X, arctg(X), artg(X) запись результата в выходной регистр происходит по первому переносу счетчика 123, для остальных функций - по второму переносу счетчика 123. Счетный вход счетчика микрокоманды 133 соединен с первой фазой Ф1 блока формирования синхросерий 167. Выход счетчика 133 совместно с кодом функции поступает на адресный вход блока памяти микрокоманд 134, содержимое которого записывается в регистр микрокоманд 135 третьей фазой ФЗ. На вход блока 138 формирования номера условного перехода поступает четырехразрядный код условного перехода с регистра микрокоманд 135 и выходной сигнал элемента И 139. Узел 138 формирования номера условного перехода работает в соответствии с логикой

I вых.138 = вых.139 + I вых.135

II вых.138 = вых.139 + II вых.135

III вых.138 = вых.139 + III вых.135

IV вых.138 = вых.139 + IV вых.135

Таким образом, если выход элемента 139 принимает значение "1", то на выходе узла формирования номера условного перехода 138 устанавливается значение 0111 (7 микрокоманда). На вход записи условного перехода счетчика 133 микрокоманд поступает сигнал с элемента ИЛИ 132, на вход которого поступают выходы элементов И 140, 141. На первый вход элементов И 140 и 141 соответственно поступают второй выход блока 33 анализа аргумента (а) и седьмой разряд регистра 135 микрокоманд (b), на второй вход элементов И 140 и 141 поступает вторая фаза Ф2. Таким образом, номер условного перехода записывается в счетчик микрокоманд 133 второй фазой Ф2 при условии, если а = 1, либо b = 1.

Содержимое регистра 135 микрокоманд напрямую, через элементы И 146-160, через элементы И 161-164 соединены соответствующими исполнительными устройствами. На вход группы элементов И поступает шестиразрядный выход 47 Кj, Kj+1, 2Kj+2 сумматора 130 блока анализа аргумента 33 и сигнал с регистра 135 микрокоманд.

Обозначим сигналы с регистра 135 микрокоманд на входах групп элементов И 161, 162, 163, 164 соответственно ХК, UK, YK, ZK.

Группы элементов И работают в соответствии с логикой

Вых. Хi = XK ˙ (Kj)i

Вых. Yi = YK ˙ (Kj)i

Вых. Zi = ZK ˙ (Kj)i

Вых. Ui = UK ˙ (Kj)i, где Вых. Xi, Вых. Yi, Вых. Zi, Вых. Ui - выходы i-х элементов И, формирующих значения Кj для блоков сдвига соответственно 32, 11, 10, 31 (Кj)i - i-й разряд величины сдвига Кj, поступающей из блока анализа аргумента 33.

i = 1, 2, 3, 4, 5, 6.

Блок 34 формирования начальных условий имеет четырехразрядный выход, первый разряд соединен со старшим разрядом первого информационного входа первого 15 мультиплексора.

Блок 34 работает в соответствии с табл. 4.

Остальные разряды соответствующих информационных входов мультиплексоров 15, 16, 17 подсоединены к "0".

Вычисление функции ехр(Х) выполняется в соответствии со структурной схемой микропрограммы, представленной на фиг. 5.

По входу кода функции устройства подается код 0001 в блок анализа аргумента 33, блок управления 13, блок анализа знака 12, блок формирования начальных условий 34. По сигналу "Исходное состояние" управляющие входы мультиплексора 20 устанавливаются в режим пропускания прямого кода регистра 23, если знаковый разряд аргумента 3Н = 0, и дополнительного кода, если 3Н = 1.

В первой микрокоманде по сигналам 88, 96 с выхода блока управления 13 мультиплексоры 18 и 16 соответственно переключаются на канал входного аргумента Х и начальных условий Y0 = 1. По сигналам 102, 103, 44 происходит соответственно запись информаций в регистры: в четвертый 4 - аргумент Х, во второй 2 - начальные условия Y0 = 1, в регистр 119 аргумента - аргумент Х.

Во второй микрокоманде по сигналу с выхода 45 в десятиразрядный регистр 120 адреса узла определения длины сдвига записываются в следующем формате значения номера типа функции (НТФ) - 2 разряда, содержимое счетчика 123 - 4 разряда, знак аргумента - 1 разряд, выход коммутатора анализируемых разрядов 122 - 3 разряда. По сигналу с выхода 46 дается разрешение на переключение счетчика 123 по а - величине, появляющейся на выходе блока 124 определения длины сдвига. Автоматически осуществляется условный переход. Если а = =1, то Cr 123 = Cr 123 + 1 и в счетчик 133 микрокоманд записывается номер условного перехода 0010 (2-я микрокоманда). Запись результата в выходной тридцатый 30 регистр и блокировка генератора 137 осуществляется по сигналу переноса Р15 счетчика 123.

Если а = 0, счетчик 123 не меняет своего состояния и счетчик 133 переходит к третьей микрокоманде.

В третьей микрокоманде по сигналу с выхода 41 блока управления 13 дается разрешение выход Кj из блока анализа аргумента 33, по сигналу с выхода 116 - (YK) величина сдвига Кj поступает на управляющий вход блока 11 сдвига по сигналу с выхода 108, в шестой 23 регистр записывается значение Yj ˙ 2-Kj по сигналам с выходов 84, 110, 112 соответственно восьмой 22 мультиплексор переключается на первый информационный вход, в двенадцатый 29 регистр записывается результат суммы Хj+1 = Xj - -ln(1 + εj 2-Kj), в десятый 27 регистр записывается результат суммы Yj+1 = Yj + εj 2-Kj Yj. В четвертой микрокоманде по сигналам 92, 102, 98, 104, 44, 76 выходов блока управления соответственно четвертый мультиплексор 18 переключается на пятый информационный вход, в четвертый регистр 4 записывается содержимое двенадцатого 29 регистра Хj+1, второй мультиплексор 16 переключается на четвертый информационный вход, во второй регистр 2 записывается содержимое десятого 27 регистра Yj+1. в регистр 119 записывается содержимое двенадцатого 29 регистра Хj+1, осуществляется условный переход по b = 1 ко 2-й микрокоманде. По сигналу Р 15 = 1 осуществляется запись в выходной регистр 30 значения функций и блокирование генератора 137.

Вычисление функций arctg(X), arth(X) выполняется в соответствии со структурной схемой микропрограммы, представленной на фиг. 8. По входу кода функции устройства в блок 33 анализа аргумента, блок 13 управления, блок 12 анализа знака, блок 34 формирования начальных условий подается код функций 0100 (для arth(X) либо 1000 (для arctg(X)). По сигналу "Исходное состояние" управляющие входы мультиплексоров устанавливаются в следующие режимы соответственно.

При вычислении arctg(X): для мультиплексора 21 - если "зн" = 0, то пропускается прямой код регистра 25, если "зн" = 1 - дополнительный код, для мультиплексора 22 - если "зн" = 0, то пропускается дополнительный код регистра 24, если "зн" = 1 - прямой код.

При вычислении arth(X): для мультиплексоров 21 и 22, если "зн" = 0, то пропускается дополнительный код соответственно регистров 25 и 24, если "зн" = 1 - прямой код регистров 25 и 24.

В первой микрокоманде по сигналам из блока управления 13 по 88 - мультиплексор 18 переключается на канал входного аргумента Х, по 102 - запись в регистр 4 значения аргумента Х, по 96 переключение мультиплексора 16, на канал начальных условий, по 104 запись начальных условий в регистр 2 Y0 = 0, по 94 - переключение мультиплексора 17 на канал начальных условий, по 103 - запись начальных условий в регистр 3 U0 = 1, по 44 запись аргумента Х в регистр 119.

Вторая микрокоманда общая для всех функций.

В третьей микрокоманде по сигналу 41 выходы - дается разрешение на выход Кj из блока анализа аргумента 33, по сигналам с 114, 115 выходов величина сдвига Кj поступает на управляющие выходы соответственно блоков сдвига 32 и 31, по 106, 107 сигналам-запись соответственно в регистр 25 величины Xj, 2-Kj , в регистр 24 Uj 2-Kj, по сигналу 85 - мультиплексор 20 переключается на первый информационный вход, по 86 включается перекрестная связь между мультиплексорами 21 и 22, по 110 - запись в регистр 29 значения соответственно для arctg(X): Xj+1 = Xj - εj 2-KjUj, для arth(X): Xj+1 = =Xj - εj 2-KjUj; по 111 запись в регистр 28 значения соответственно для arctg(X)Uj+1 = =Uj + εj 2-Kj для arth(X): Uj+1 = Uj - εj 2-KjXj; по 112 - запись в регистр 27 соответственно для arctg(X): Yj+1 = Yj + εj arctg 2-Kj для arth(X):

Yj+1= Yj+εjln ..

..

В четвертой микропрограмме по сигналам 92, 99, 98 мультиплексоры 18, 17, 16 соответственно переключаются на регистры 29, 28, 27, по сигналам 102, 103, 104 соответственно в регистры 4, 3, 2 записываются значения Xj+1, Uj+1 и Yj+1 по сигналу 44 в регистр 119 записываются значение Xj+1, по сигналу 76 осуществляется условный переход к b = 1 по второй микрокоманде.

Вычисление функции  выполняется в соответствии со структурной схемой микропрограммы, представленной на фиг. 15. По входу кода функции устройства подается код 1010. По сигналу "Исходное состояние" управляющие входы мультиплексоров 22 и 20 устанавливаются в режим пропускания прямого кода соответственно регистров 25 и 23, если "зн" = 0, дополнительного, если "зн" = 1.

выполняется в соответствии со структурной схемой микропрограммы, представленной на фиг. 15. По входу кода функции устройства подается код 1010. По сигналу "Исходное состояние" управляющие входы мультиплексоров 22 и 20 устанавливаются в режим пропускания прямого кода соответственно регистров 25 и 23, если "зн" = 0, дополнительного, если "зн" = 1.

В первой микрокоманде по сигналам 88 и 95 мультиплексоры 18 и 16 устанавливаются на канал входного аргумента Х, по сигналам 102, 104, 44 значение аргумента Х записывается в регистры 2, 4 и 119.

Вторая микрокоманда - общая для всех функций.

В третьей микрокоманде по сигналам с 41, 114 выходам соответственно дается разрешение на выход из блока анализа аргумента 33 величины Kj и значение Kj устанавливается на управляющие входы блока 32 сдвига, по сигналам 106 в регистр 25 записывается значение Хj 2-Kj по 110 сигналу в регистр 29 записывается значение суммы Хj + εj 2-Kj Xj.

В четвертой микрокоманде по сигналам с 41, 42 выходов дается разрешение на выход значения Kj+1 из блока анализа аргумента 33, по 116 - значение Кj+1 устанавливается на управляющих входах блока сдвига по 108 в регистр 23 записывается Yj2-(Kj+1) по 112 - в регистр 27 записывается значение Yj+1 = =Yj + εj 2-(Kj+1)Yj.

В пятой микрокоманде по сигналам с 43 выхода дается разрешение на выход значения 2Кj+2 из блока анализа аргумента 33 по 114 на управляющие входы блока сдвига 32 устанавливается (2Кj+2) по 106 - в регистр 25 записывается значение Хj2(-2Kj+2).

В шестой микрокоманде по сигналам с 77 выхода - управляющие входы мультиплексора 22 устанавливаются в режим пропускания прямого кода регистра 25, по 92 - мультиплексор 18 переключается на канал регистра 29, по 102 - в регистр 4 записывается значение Xj + εj 2-Kj Xj (первой фазой Ф1), по 110 в регистр 29 записывается Xj + 2-Kj Xj + 2-(Kj+2)Xj(третьей фазой ФЗ).

В седьмой микрокоманде по сигналам с 92, 98 мультиплексоры 18 и 16 соответственно переключаются на каналы регистра 29 и регистра 27 по сигналам 102, 104 и 44 в регистры 4, 2 и 119 соответственно записываются Xj+1, Yj+1, Xj+1 по 76 осуществляется условный переход ко второй микрокоманде.

Вычисление функции деления Y/Х выполняется в соответствии со структурной схемой микропрограммы, представленной на фиг. 16. По входу кода функции устройства подается код 1011. По сигналу "Исходное состояние" управляющие входы мультиплексоров 20 и 22 устанавливаются режим пропускания прямого кода соответственно регистров 23 и 25, если "зн" = 0 и дополнительного, если "зн" = 1.

В первой микрокоманде по сигналам с 88 выхода мультиплексор 18 переключается на канал Х, по 95 - мультиплексор 16 переключается на канал Y, по 102 в регистр 4 записывается значение Х, по 104 - в регистр 2 записывается значение Y, по 44 в регистр 119 записывается значение Х.

Вторая микрокоманда общая для всех функций.

В третьей микрокоманде по сигналу с 41 выхода дается разрешение на выход значения Кj из блока 33 анализа аргумента, по 114, 117 сигналам соответственно значения Кj поступают на управляющие входы соответственно 32 и 11 блоков сдвига, по 106 и 25, 108 соответственно в регистры 25 и 23 записываются значения Хj 2-Kj и Y 2-Kj ,по 110 и 112 в регистры 29 и 27 записываются соответственно Xj+1 = Xj + εj 2-Kj Xj и Yj+1 = Yj + + εj 2-Kj Yj.

В четвертой микрокоманде по сигналам с 92, 98 выходов мультиплексоры 18 и 16 переключаются соответственно на каналы регистров 29 и 27, по 102, 109, 44 в регистры 2, 2 и 119 соответственно записываются значения Xj+1, Yj+1 и Xj+1, по 76 - осуществляется условный переход ко второй микрокоманде.

Вычисление функций ln(X) выполняется в соответствии со структурной схемой микропрограммы, представленной на фиг. 17. По входу кода функции устройства подается код 1110. По сигналу "Исходное состояние" управляющие входы мультиплексора 22 устанавливаются в режим пропускания прямого кода регистра 25, если "зн" = 0 и дополнительного, если "зн" = 1.

В первой микрокоманде по сигналам с 88 выхода мультиплексор 18 переключается на канал Х, по 102 - в регистр 4 записывается Х, по 96 - мультиплексор 16 переключается на канал начальных условий Y0, 104 - в регистр 2 записывается Y0 = 0, по 44 - в регистр 119 записывается Х.

Вторая микрокоманда для всех функций общая.

В третьей микрокоманде по сигналу с 41 выхода дается разрешение на выход Кj из блока анализа аргумента 33, по 114 значение Kj поступает на управляющие входы блока 32 сдвига, по 106 в регистр записывается значение Xj2-Kj по 85 - мультиплексор 20 переключается на первый информационный вход, по 110 - в регистр 29 записывается Хj+1 = Xj + εj2-KjXj, по 112 - в регистр 27 записывается Yj+1 = Yj + ln(1 + εj2-Kj).

В четвертой микрокоманде по сигналу с 92 выхода - мультиплексор 18 переключается на канал регистра 29, по 102 в регистр 4 записывается Хj+1по 98 - мультиплексор 16 переключается на канал регистра 27, по 104 в регистр 2 записывается Yj+1, по 44 в регистр 119 записывается Xj+1, по 76 осуществляется условный переход ко второй микрокоманде.

Вычисление тригонометрических функций (sin(X), cos(X), tg(X), ctg(X)) и гиперболических функций (sh(X), ch(X), th(X), cth(X)) выполняются в соответствии со структурными схемами микропрограмм, представленных на фиг. 6, 7, 9-14. Микропрограммы вычисления тригонометрических функций отличаются от микропрограмм вычисления гиперболических функций сигналами YC2', ZC1 для тригонометрических функций и YC2' ZC2 для гиперболических функций в пятой микрокоманде. Микропрограммы вычисления тригонометрического и гиперболического синуса (sin(X), sh(X)), косинуса (cos(X), ch(X)), тангенса (tg(X), th(X)) и котангенса (ctg(X), cth(X)) отличаются содержанием седьмой микрокоманды.

По входу кода функции устройства устанавливается соответствующий код функции. По сигналу "Исходное состояние" управляющие входы мультиплексора 19 устанавливаются в режим пропускания прямого кода регистра 23, если "зн" = 1 и дополнительного, если "зн" = 0 для тригонометрических функций и в режим пропускания прямого кода, если "зн" = 0, и дополнительного, если "зн" = 1 для гиперболических функций, управляющие входы мультиплексора 20 устанавливаются в режим пропускания прямого кода регистра 5, если "зн" = 0, и дополнительного кода, если "зн" = 1 для тригонометрических и гиперболических функций, мультиплексор 21 устанавливается в режим пропускания прямого кода регистра 24 для тригонометрических функций и дополнительного кода гиперболических функций.

В первой микрокоманде по сигналу с 88 выхода мультиплексор 18 переключается на канал выходного аргумента Х, по 102 - в регистр 4 записывается Х, по 96 мультиплексор 16 переключается на канал начальных условий Y0, по 104 - в регистр 2 записывается Y0 = 0, по 100 - мультиплексор 15 переключается на канал начальных условий Z0, по 105 - в регистр 1 записывается Z0 = 1, по 93 - мультиплексор 17 переключается на канал начальных условий U0, по 103 - в регистр 3 записывается U0 = 1, по 44 - в регистр 119 записывается значение Х.

Вторая микрокоманда общая для всех функций.

В третьей микрокоманде по сигналу 41 выхода дается разрешение на выход Kj из блока анализа аргумента 33, по 116, 117 на управляющие входы блоков 10 и 11 сдвига поступает значение Kj по 108 - в регистр 23 записывается величина Yj 2-Kj, по 109 - в регистр 5 записывается величина Zj 2-Kj, по 87 включается перекрестная связь между мультиплексорами 19 и 20, по 112 - в регистр 27 записывается для тригонометрических и гиперболических функций величина Yj + εj 2-KjZj,по 113 в регистр 26 записывается величина для тригонометрических функций Zj - εj 2-KjYj; для гиперболических - Z1 + εj 2-KjYj.

В четвертой микрокоманде по сигналу с 43 выхода дается разрешение на выход величины 2Kj+2 из блока анализа аргумента 33, по 117, 116, 115 величина 2Kj+2 поступает на управляющие входы блоков 10, 11, 31 сдвига, по 108 в регистр 23 записывается Yj -(2Kj+2), по 109 в регистр 5 записывается Zj 2-(2Kj+2), по 107 в регистр 24 записывается Uj2-(2Kj+2), по 84 мультиплексор 22 переключается на первый канал, по 110 в регистр 29 записывается для тригонометрических функций Хj+1 = Xj - εj2 arctg 2-(Kj+1), для гиперболиче- ских функций Xj+1= Xj- εj ln  ..

..

В пятой микрокоманде по сигналу с 98 выхода мультиплексор 16 переключается на канал регистра 27, по 103 в регистр 2 записывается Yj + εj 2-Kj Zj, по 101 мультиплексор 15 переключается на канал регистра 26, по 105 в регистр 1 записывается для тригонометрических функций Zj - εj2-KjYj, для гиперболических функций Zj + εj 2-KjYj, по 81 (YC2') для тригонометрических функций управляющие входы мультиплексора 20 устанавливаются в режим пропускания дополнительного кода регистра 23, по 82 - управляющие входы мультиплексора 19 устанавливаются в режим пропускания дополнительного кода регистра 5, для гиперболических функций по 80 управляющие входы мультиплексора 20 устанавливаются в режим пропускания прямого кода регистра 23, по 83 - управляющие входы мультиплексора 19 устанавливаются в режим пропускания дополнительного кода регистра 5, по 112 в регистр 27 записывается для тригонометрических функций Yj+1 = Yj + +2-KjZj-2-(2Kj+2)Yj, для гиперболических функций Yj+1 = Yj + εj 2-KjZj+2-(2Kj+2)Yj, по 113 в регистр 26 записывается для тригонометрических функций Zj+1 = Zj - εj 2-Kj Yj - 2-(2Kj+2), для гиперболических функций Zj+1 = Zj + +2-KjYj+2-(2Kj+2)Zj, по 111 записывается в регистр 28 для тригонометрических функций Uj+1 = Uj + 2-(2Kj+1)Uj, для гиперболических функций Uj+1 = Uj - 2-(2Kj+2)Uj.

В шестой микрокоманде по сигналам с 92, 98, 101, 93 выходов мультиплексоры 18, 16, 15, 17 переключаются соответственно на канал регистров 29, 27, 26, 28, по 102, 104, 105, 103 в регистры 29, 27, 26, 28 и 119 соответственно записываются Хj+1, Yj+1, Zj+1, Uj+1, Zj+1 по сигналу с 76 осуществляется условный переход ко второй микрокоманде.

По сигналу Р15 первого переноса счетчика 123 в счетчик 133 микрокоманда записывается 0111 и осуществляется переход к седьмой микрокоманде, в блоке 121 преобразования кода функций номер типа функций 01 меняется на 10, соответствующий алгоритму анализа аргумента при делении (Y/X) см. табл. 1. По первому переносу счетчика 123 Р 15 триггер 136 переходит в "1" в блоке управления 13.

В седьмой микрокоманде для функций sin(X), sh(X) по сигналу 91 мультиплексор 18 переключается на канал регистра 28, по 102 в регистр 4 записывается Uj+1, по 44 в регистр 119 записывается Uj+1.

В седьмой микрокоманде для функций сosX, chX по сигналу 91 мультиплексор 18 переключается на канал регистра 28, по 102 в регистр 4 записывается Uj+1, по 99 мультиплексор 16 переключается на канал регистра 26, по 103 в регистр 2 записывается Zj+1, по 44 в регистр 119 записывается Uj+1.

В седьмой микрокоманде для функций tg(X), th(X) по сигналу 89 мультиплексор 18 переключается на канал регистра 26 по 102 и 44 в регистры 4 и 119 записывается Zj+1. В седьмой микрокоманде для функций ctg(X), cth(X) по сигналам 90, 99 мультиплексоры 18 и 16 переключаются соответственно на каналы регистров 27 и 26, по 102, 104, 44 в регистры 4, 2 и 119 записываются соответственно Yj+1, Zj+1, Yj+1.

Восьмая, девятая, десятая микрокоманды соответствуют второй, третьей, четвертой микрокомандам микропрограммы деления Х/Y фиг. 16.

Девятая микрокоманда дополнительно содержит для тригонометрических функций сигналы 79, 78 выходов, а для гиперболических функций сигналы 80 и 78 выходов, которые переводят управляющие входы мультиплексоров 20 и 22 в режим пропускания прямого кода соответственно регистров 23 и 25, если "зн" = 0 и дополнительного, если "зн" = 1.

По второму переносу счетчика 123 в регистр 30 записывается результат вычислений и через элемент 165 блокируется генератор 137 импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИВЕДЕНИЯ ФУНКЦИЙ К МУЛЬТИПЛИКАТИВНОМУ АЛГОРИТМУ ВЫЧИСЛЕНИЙ | 1990 |

|

RU2028659C1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| Устройство для деления | 1990 |

|

SU1742815A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для приведения аргумента | 1986 |

|

SU1357950A1 |

| Устройство для табличной реализации многоместных логических функций | 1982 |

|

SU1019455A1 |

| Устройство для вычисления функций синуса и косинуса | 1986 |

|

SU1478213A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах для вычисления трансцедентных функций в цифровых моделирующих, управляющих и вычислительных системах как общего, так и специального назначения. Цель изобретения - расширение класса решаемых задач за счет возможности вычисления тригонометрических, гиперболических, логарифмической, степенной, показательной и функции отношения. В устройстве применен алгоритм на основе мультипликативного подхода к представлению величин, позволяющего сократить число операций. Быстродействе устройства достигается за счет анализа двух разрядов операнда. 3 з.п. ф-лы, 26 ил.

двадцать восьмого элементов И, выход первого узла формирования знака подключен к третьему и второму входам соответственно тринадцатого и девятнадцатого элементов И и входу восьмого элемента НЕ, выход которого подключен к третьему и второму входам соответственно четырнадцатого и двадцатого элементов И, выход второго узла формирования знака соединен с третьим и вторым входами соответственно пятнадцатого и семнадцатого элементов И и входом девятого элемента НЕ, выход которого подключен к третьему и второму входам соответственно шестнадцатого и восемнадцатого элементов ИЛИ, выход четвертого узла формирования знака подключен к третьму и второму входам соответственно двадцать третьего и двадцать пятого элементов И и входу одиннадцатого элемента НЕ, выход которого соединен с третьим и вторым входами соответственно двадцать четвертого и двадцать шестого элементов И, выходы с тринадцатого и по двадцать восьмой элементов И соединены с выходами соответственно с первого по шестнадцатый

блока анализа знака.

G 11

(11) 1540558

0951

(13) C

(51)5 G 11 B 15 /02

(21) 4296335/10

(22) 17.08.87

(75) Богатин Л.Б., Зимарин С.А., Федоров Н.Н.

(73) Санкт-Петербургский опытный завод "Прибор"

(54) (57) 1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕВЕРСОМ МАГНИТНОЙ ЛЕНТЫ

, содержащее генератор опорной частоты, счетчик опорной частоты, счетный вход которого подключен к выходу генератора, формирователь импульсов, три дешифратора, выходы которых являются выходными шинами устройства, входную шину сигнала воспроизведения, соединенную с входом формирователя импульсов, и три входных шины управляющих сигналов, отличающееся тем, что, с целью повышения надежности управления реверсом магнитной ленты путем сокращения ложных срабатываний, в него введены два счетчика, триггер, четыре схемы совпадения и три инвертора, при этом первый вход первой схемы совпадения соединен с выходом генератора опорной частоты, а выход - со счетным входом первого счетчика, установочный вход которого соединен с выходом формирователя импульсов и с первым входом второй схемы совпадений, а выход первого счетчика - с вторым входом первой схемы совпадения и с установочным входом второго счетчика, выход которого подключен к входу первого инвертора и к счетному входу триггера, выход

первого инвертора подключен к второму входу третьей схемы совпадений и к второму входу втор выходом двенадцатого элемента НЕ, вход которого соединен с первыми входами семнадцатого и восемнадцатого элементов И, вторыми входами пятнадцатого и шестнадцатого элементов И и входом одиннадцатого разряда информационного входа блока анализа знака, вход двенадцатого разряда информационного входа которого соединен с первыми входами с двадцать третьего по двадцать шестой элементов И и входом тринадцатого элемента НЕ, выход которого соединен с первыми входами двадцать первого, двадцать второго, двадцать седьмого и двадцать восьмого элементов И, вход десятого разряда информационного входа блока анализа знака через четырнадцатый элемент НЕ подключен ко вторым входам с двадцать первого по двадцать четвертый элементов И, третий вход двадцать первого элемента И соединен со вторым входом двадцать восьмого элемента И, входом десятого элемента НЕ и выходом третьего узла формирования знака, выход десятого элемента НЕ подключен к третьему и второму входам соответственно двадцать второго и двадцать восьмого элементов И, выход первого узла формирования знака подключен к третьему и второму входам соответственно тринадцатого и девятнадцатого элементов И и входу восьмого элемента НЕ, выход которого подключен к третьему и второму входам соответственно четырнадцатого и двадцатого элементов И, выход второго узла формирования знака соединен с третьим и вторым входами соответственно пятнадцатого и семнадцатого элементов И и входом девятого элемента НЕ, выход которого подключен к третьему и второму входам соответственно шестнадцатого и восемнадцатого элементов ИЛИ, выход четвертого узла формирования знака подключен к третьму и второму входам соответственно двадцать третьего и двадцать пятого элементов И и входу одиннадцатого элемента НЕ, выход которого соединен с третьим и вторым входами соответственно двадцать четвертого и двадцать шестого элементов И, выходы с тринадцатого и по двадцать восьмой элементов И соединены с выходами соответственно с первого по шестнадцатый блока анализа знака.

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-08-30—Публикация

1988-11-21—Подача