ветственно с выходом блока памяти антилогарифмов и выходом целой части второго сумматора, третий и четвертый входы и выход дробной части которого соединены соответственно с выходами первого и третьего блоков памяти логарифмов и входом блока памяти антилогарифмов, вход третьего блока памяти логарифмов соединен с входом нор- Мирующего делителя преобразователя.

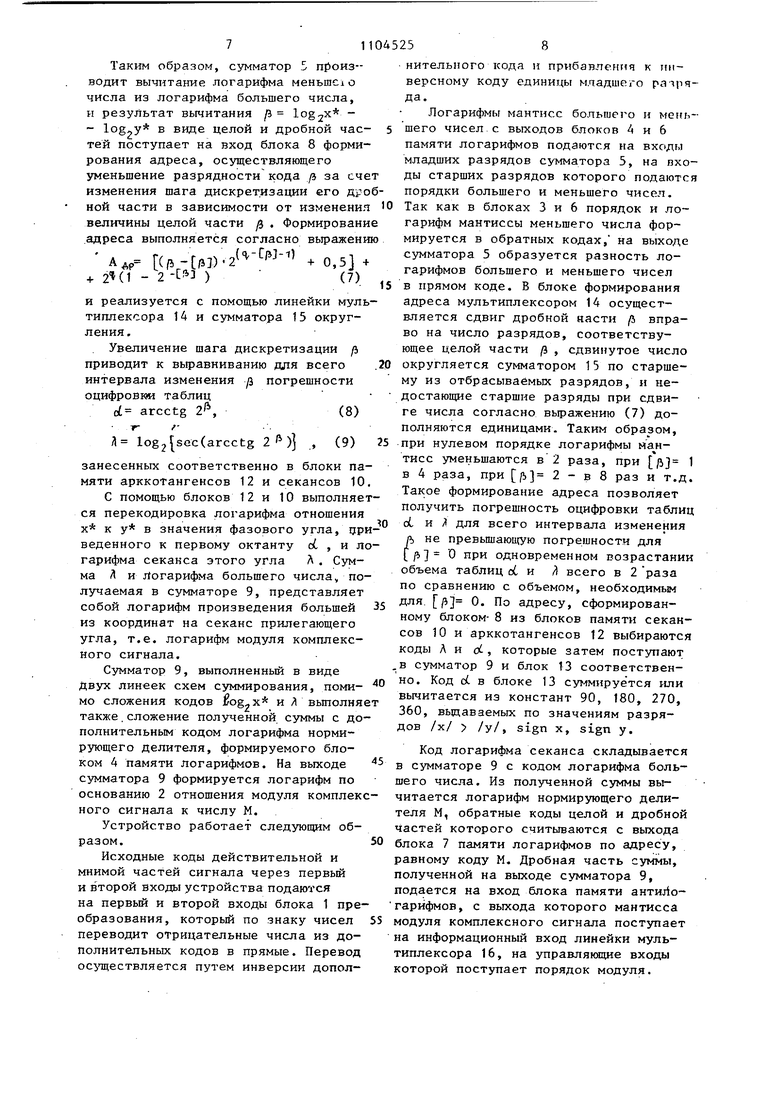

2. Преобразователь по п. 1, отличающийся тем, что блок преобразования чисел из формы с плавающей запятой в форму с фиксированной запятой содержит мультиплексор, блок памяти констант, преобразователь прямого .кода в дополнительный и два сумматора округления, причем первый

и второй информационные входы блока соединены соответственно с информационным входом преобразователя прямого кода в дополнительный и информацйонньгм- входом мультиплексора, управляющий вход и выход которого соединены соответственно с управляющим входом блока и входом первого сумматора округления, входы знаков аргументов и знака разности блока соединены через блок памяти констант с управляющим входом преобразователя прямого кода в дополнительный и первым входом второго сумматора округления, второй вход которого соединен с выходом преобразователя прямого кода в дополнительный, выходы сумматоров округления соединены с выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО для ПЕРЕРАБОТКИ ЧИСЛОВОЙ И БУКВЕННОЙ ИНФОРМАЦИИ | 1969 |

|

SU255656A1 |

| Устройство для вычисления функций синуса и косинуса | 1987 |

|

SU1494002A2 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1976 |

|

SU593212A1 |

| Устройство для вычисления эквивалентного уровня звуковой экспозиции | 1988 |

|

SU1640556A1 |

| Устройство для вычисления корня @ -степени | 1986 |

|

SU1381494A1 |

| Устройство для возведения в степень | 1984 |

|

SU1171788A1 |

| Устройство для умножения и деления | 1980 |

|

SU898424A1 |

| Устройство для вычисления функций | 1985 |

|

SU1297038A1 |

1. ПРЕОБРАЗОВАТЕЛЬ КОМПЛЕКСНЫХ СИГНАЛОВ, содержащий блок преобразования дополнительного кода в прямой, блок выделения наибольшего из чисел, блок преобразования чисел из формы с. фиксированной запятой в форму с плавающей запятой, блок памяти и блок преобразования чисел из формы с плавающей запятой в форму с фиксированной запятой, причем входы действительной и мнимой частей преобразователя соединены с соответствующими входами блока преобразования дополнительного кода в прямой, выходы первого и второго аргументов и знаков которого соединены соответственно с первым и вторым входами блока вьщеления наибольшего из числа и входом знаков аргументов блока преобразования чисел из формы с плавающей запятой в форму с фиксированной запятой, выход и вход знака разности аргументов которого соединены соответственно с выходом преобразователя и выходом знака разности блока вьщеления наибольшего из чисел, выходы большего и меньшего чисел которого соединены соответственно с входами большего и меньшего чисел блока преобразования чисел из формы с фиксированной запятой в форму с плавающей запятой, отличающийся тем, что, с целью расширения класса решаемых задач за счет дополнительной возможности вьшолнения операции нормирования модуля сигнала на весовой делитель я сокращения объема памяти, он содержит два сумматора, блок формирования адреса, а блок памяти выполнен в виде трех блоков памяти логарифмов чисел, блока памяти секансов, блока памяти антилогарифмов и блока памяти арккотангенсов, причем выходы мантиссы большего числа, мантиссы .меньшего числа и порядков этих чисел (Л блока преобразования чисел из формы с фиксированной запятой в форму с плавающей запятой соединены соответственно с входом первого блока памяти логарифмов, входом второго блока памяти логарифмов и первым и вторым входами старших разрядов первого сумматора, подключенного первым входом старших разрядов к первому входу вто4; ел рого сумматора, выходы первого и второго блоков памяти логарифмов соедиtsD СЛ нены соответственно с первым и вто-, рьм входами младших разрядов первого сумматора, выход первого сумматора подключен через блок формирования адреса к входам блоков памяти секансов и арккотангенсов, выходы которых соединены соответственно с вторым входом второго сумматора и первым информационным входом блока преобразования чисел из формы с плавающей запятой в форму с фиксированной запятой, второй информационный и управляющий входы которого соединены соот

Устройство относится к вычислитель ной технике и предназначено для преобразования комплексных сигналов из прямоугольных координат к полярным, а также нормирований модуля комплексного числа.

Известно арифметическое устройство, работающее по алгоритму Волдера и содержащее сдвигающие регистры, коммутаторы, -сумматоры-вычитатели 1 .

Недостаток арифметического устройства - невысокое быс.тродействие, являющееся следствием итерационного алгоритма вычислений.

Наиболее близким по технической сущности к изобретению является табличный преобразователь, содержащий преобразователь кодов сигналов, схему сравнения и коммутации, схему сдвига, таблицу преобразований, модификатор модуля и фазы, у которого первый и второй входы соединены с первым и вторым входами схемы преобразования кодов сигналов, вtopoй и третий выходы схемы преобразований соединены с первым и вторым входами схемы сравнения и коммутации, первый выход которой соединен с первым входом модификатора модуля и фазы. Первый вЬпсод схемы преобразования кодов сигналов соединен с вторым входом модификатора, первый и второй выходы которого

соединены соответственно с первым И вторым выходами устройства. Второй и третий выходы схемы сравнения и коммутации соединены с первым и вторым входами схемы сдвига, первый и второй выходы которой соединены с первым и вторым входом таблицы преобразований, а третий выход схемы сдвлга соединен с третьим входом модификатора, четвертьй и пятый входы которого соединены с первым и вторым выходами таблицы преобразований ,21. Недостатком известного устройства является большой объем таблицы преобразований, равный

Q. 4,-q«.i) (1)

где q - разрядность кода мантиссы модуля сигнала;

- разрядность кода фазы

Vi

сигнала (G d ; q , q-j - разрядность кодов мантисс входных переменных; Aq f, - разрядность кода разности порядков.

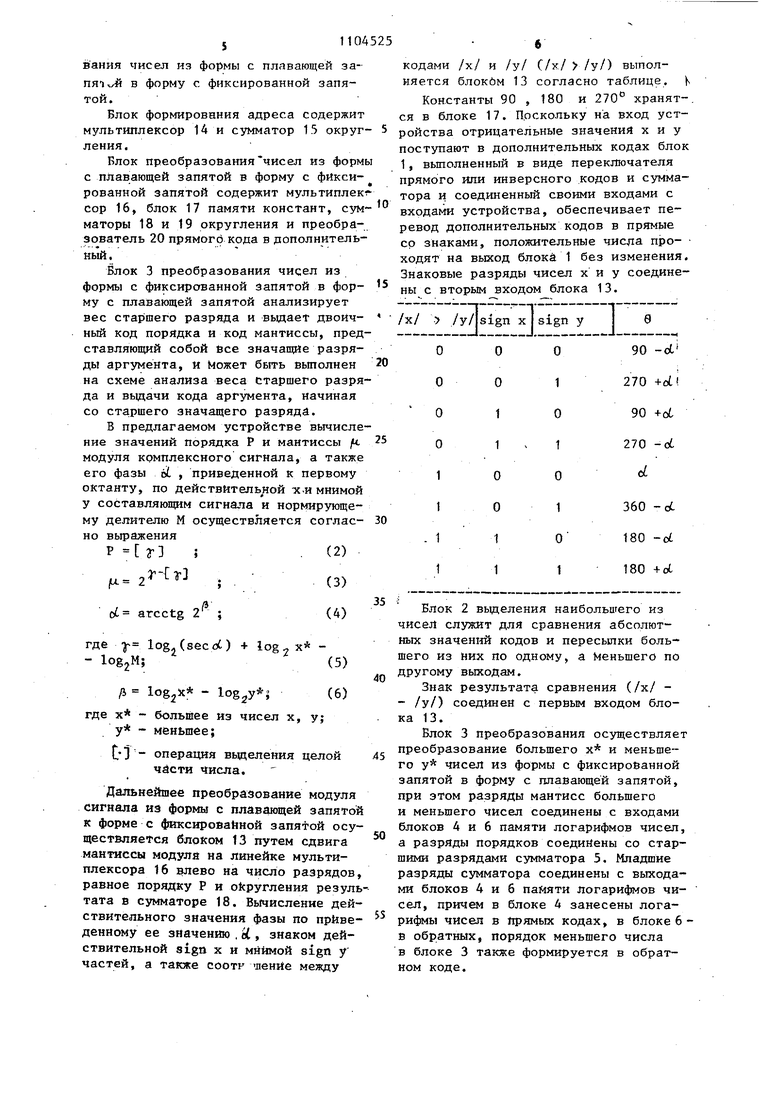

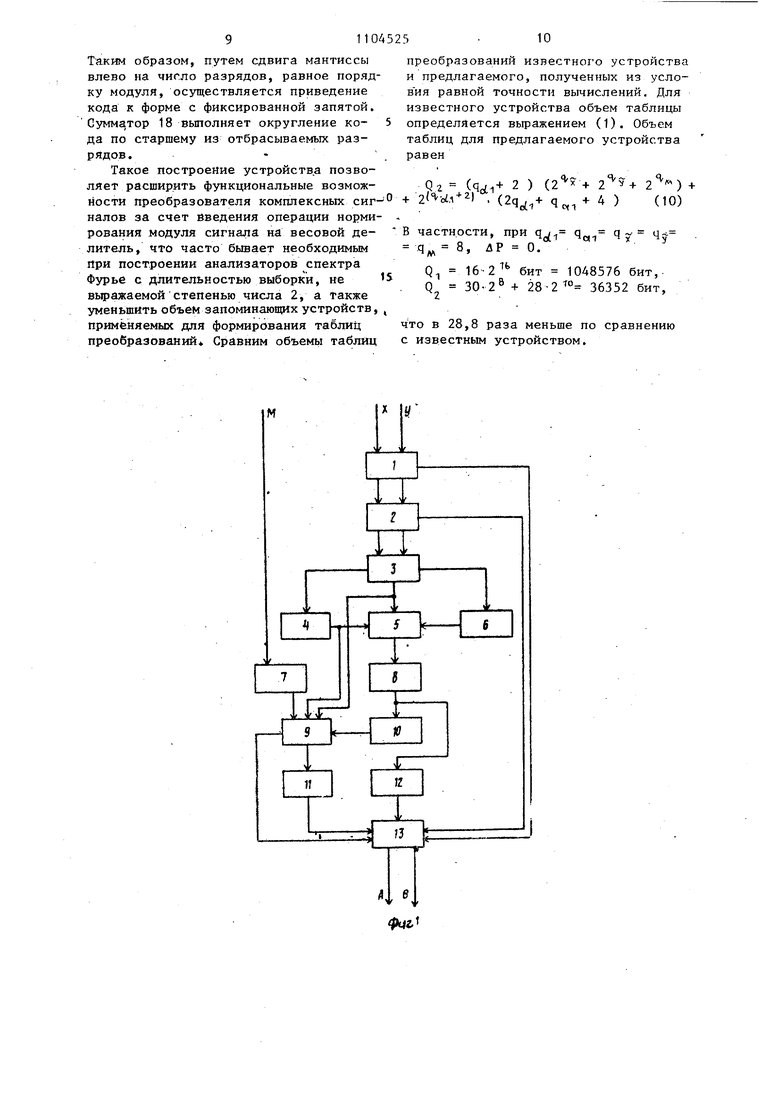

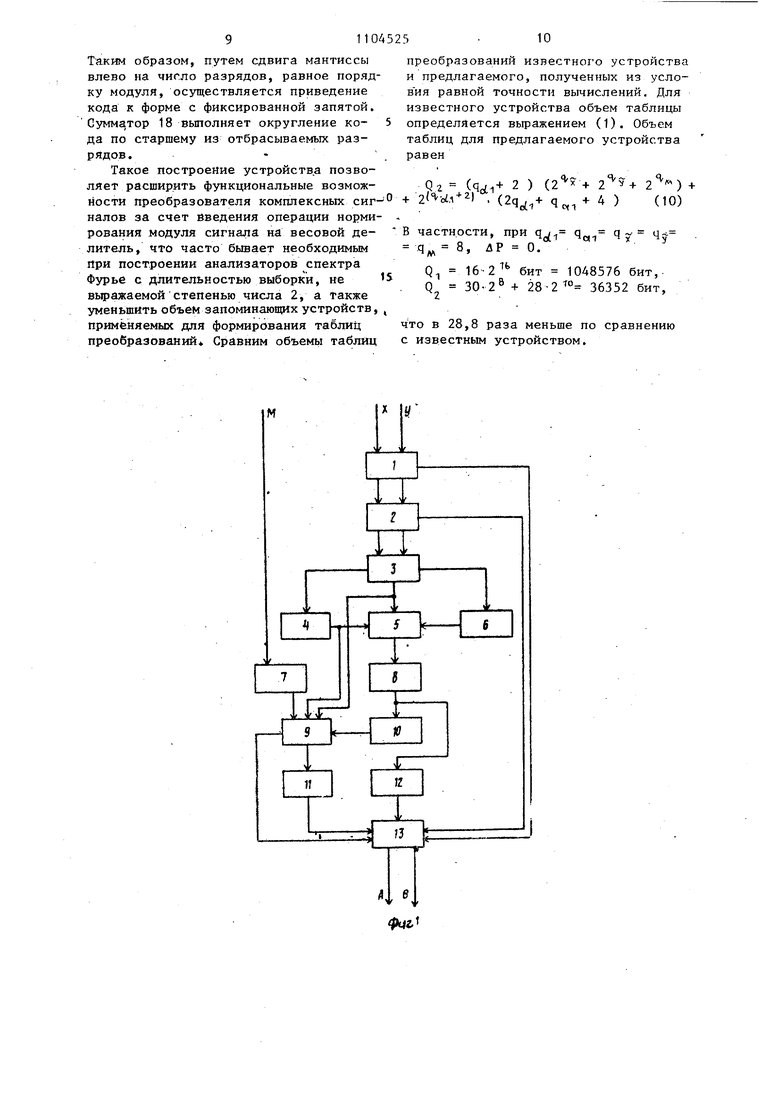

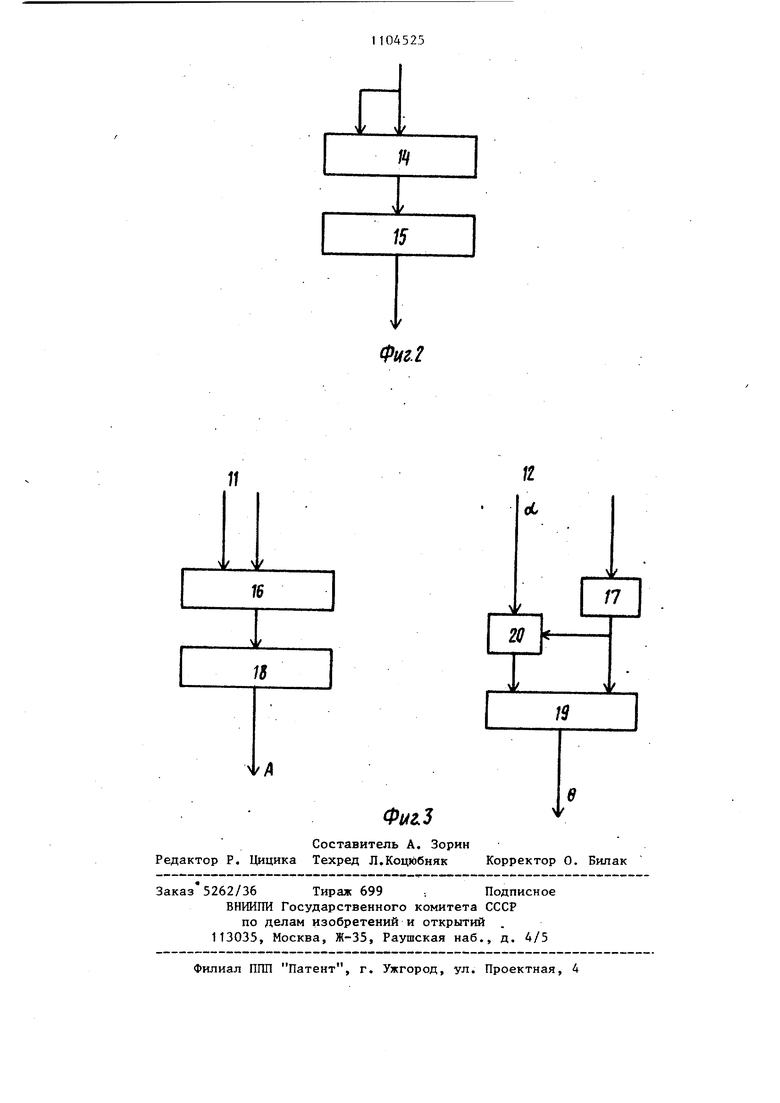

1 Целью изобретения является расщирение класса рещаемых задач за счет дополнительной возможности выполнения операции нормирования модуля сигнала на весовой делитель и сокращения объема памяти. 3 Поставленная цель достигается тем что преобразователь комплексных сигн лов, содержащий блок преобразования дополнительного кода в прямой, блок выделения наибольшего из чисел, блок преобразования исел из формы с фиксированной запятой в форму с плавающей запятой, блок памяти и блок преобразования чисел из формы с плавающей запятой в форму с фиксированной запятой, причем входы действительной .и мнимой частей преобразователя соединены с соответствующими входами блока преобразования дополнительного кода в прямой, выходы первого и второго аргументов и знаков, которого соединены соответственно с первым и вторым входами блока вьщеления намбольшего из числа и входом знаков аргументов блока преобразования чисел из формы с плавающей запятой в форму с фиксированной запятой, выход и вход знака разности аргументов которого- соединены соответственно с вьгходом преобразователя и выходом знака разности блока выделения наибольшего из чисел, выходы большего и меньшего чисел которого соединены соответственно с входами большего и меньшего чисел преобразования чисел из формы с фиксированной запятой в форму с плавающей запятой, содержи два сумматора, блок формирования -адреса, а блок памяти выполнен в виде трех блоков .памяти логарифмов чисел блока памяти секансов, блока памяти антилогарифмов и блока памяти арккотангенсов, причем выходы мантиссы большего числа, мантиссы меньшего числа и порядков этих чисел блока преобразования чисел из формы с фиксированной запятой в форму с плавающей запятой соединены соответственно с входом первого блока памяти логарифмов, входом второго блока памяти логарифмов и первым и вторым входами старших разрядов первого сумматора, подключенного первым входом старших разрядов к первому входу второго сумматора, выходы первого и второго блоков памяти логарифмов соединены с первым и вторым входами младших разрядов первого су 1матора, выход первого сумматора подключен через блок формирования адреса к входам блоков памяти секансов и арккотангенсов, выходы которых соединены соответственно с вторым входом второго сумматора и первым инфор 2 54 циоинып вхолом блока пpcoбpa: oп,-iиия 1исел из формы с плавающей запятой в форму с фиксированной запятой, второй информационный и управляющий входы которого соединены соответственно с выходом блока памяти антилогарифмов и вьгходом целой части второго сумматора, третий и четвертый входы и выход дробной части которого соединены с выходами первого и третьего блоков памяти логарифмов и входом блока памяти антилогарифмов, вход третьего блока памяти -логарифмов соединен с входом нормирующего делителя преобразователя. Блок преобразования чисел из формы с плавающей запятой в форму с фиксированной запятой содержит мультиплексор, блок памяти констант, преобразователь прямого кода в дополнительный и два сумматора округления, первый и второй информационные входы блока соединены соответственно с информационным входом преобразователя прямого кода в дополнительный и информационным входом мультиплексора, управляющий вход и выход которого соединены соответственно с управляющим входом блока и входом первого сумматора округления, входы знаков аргументов и знака разности блока соединены через блок памяти констант с управляющим входом преобразователя прямого кода в дополнительный и первым входом в.торого сумматора округления, второй вход которого соединен с выходом преобразователя прямого кода в дополнительный, выходы сумматоров округления соединены с выходом блока. I На фиг. 1 представлена блок-схема преобразователя; на фиг. 2 - блоксхема блока формирования адреса; на фиг. 3 - схема блока преобразования чисел из формы с плавающей запятой в форму с фиксированной запятой. Преобразователь комплексных сигналов содержит преобразователь 1 дополнительного кода в прямой, блок 2 выделения наибольшего из чисел, блок 3 преобразования чисел из формы с фиксированной запятой в форму с плавающей запятой, блок 4 памяти логарифмов, сумматор 5, блоки 6 и 7 памяти логарифмов, блок 8 формирования адреса , сумматор 9, блоки памяти секансов 10, антилогарифмов 11 и арккотангенсов 12 и блок 13 преобразо51104вания чисел из формы с плавающей запя1 хй в форму с фиксированной запятой. Блок формирования адреса содержит мультиплексор 14 и сумматор 15 округ ления. Блок преобразованиячисел из форм с плавающей запятой в форму с фиксированной запятой содержит мультиплек сор 16, блок 17 памяти констант, сум маторы 18 и 19 округления и преобразователь 20 прямого кода в дополнительный. Блок 3 преобразования чисел из формы с фиксированной запятой в форму с плавающей запятой анализирует вес старшего разряда и выдает двоИчный код порядка и код мантиссы, пред ставляющий собой бее значащие разряды аргумента, и Может быть вьшолнен на схеме анализа веса старшего разря да и выдачи кода аргумента, начиная со старшего значащего разряда. В предлагаемом устройстве вычисле ние значений порядка Р и мантиссы |k. модуля комплексного сигнала, а также его фазы ci , приведенной к первому октанту, по действительной х.и мнимой у составляющим сигнала и нормирующему делителю М осуществляется согласно вьфажения Р y ; ; . (2) х arcctg 2 где f logj(secot) + log,, х - log2M;(5) /i logjX - (6) где X - большее из чисел х, у; у меньшее; to операция вьщеления целой чести числа. Дальнейшее преобразование модуля сигнала из формы с плавающей запятой к форме с фиксировайной запятой осуществляется блоком 13 путем сдвига мантиссы модула на линейке мультиплексора 16 влево на число разрядов, равное порядку Р и округления резуль тата в сумматоре 18. Вьмисление действительного значения фазы по приведенному ее значению . Ц , знаком действительной sign X и мнимой sign у частей, а также COOTF шенйе между кодами /X/ и /у/ С/х/ /у/) выполняется блокбм 13 согласно таблице. Ь Константы 90 , 180 и 270 хранят-, ся в блоке 17. Поскольку на вход устройства отрицательные значения х и у поступают в дополнительных кодах блок 1, вьшолненный в виде переключателя прямого или инверсного кодов и сумматора и соединенный своими входами с входами устройства, обеспечивает перевод дополнительных кодов в прямые со знаками, положительные числа про- ходят на выход блока 1 без изменения. Знаковые разряды чисел х и у соединены с вторым входом блока 13. Блок 2 вьщеления наибольшего из чисел служит для сравнения абсолютных значений кодов и пересьшки большего из них по одному, а Меньшего по другому выходам. Знак результата сравнения (/х/ - /У/) соединен с первым входом блока 13. Блок 3 преобразования осуществляет преобразование большего х и меньшего у чисел из формы с фиксированной запятой в форму с плавающей запятой, при этом разряды мантисс большего и меньшего чисел соединены с входами блоков А и 6 памяти логарифмов чисел, а разряды порядков соединены со старшими разрядами сумматора 5. Младшие разряды сумматора соединены с выходами блоков 4 и 6 памяти логарифмов чисел, причем в блоке 4 занесены логарифмы чисел в лрямых кодах, в блоке 6в обратных, порядок меньшего числа в блоке 3 также формируется в обратном коде. Таким образом, сумматор 5 nf)OH3-водит вычитание логарифма меньше о числа из логарифма большего числа, и результат вычитания logjX - log,,y в виде целой и дробной час тей поступает на вход блока 8 формирования адреса, осуществляющего уменьшение разрядности кода /з за сче изменения шага дискретизации его дро ной части в зависимости от изменения величины целой части /3 Формировани адреса выполняется согласно выражени 2 V-CpM) 0,5. ААР + 241 - ) (7) и реализуется с помощью линейки муль типлексора 14 и сумматора 15 округления. Увеличение шага дискретизации /5 приводит к вьфавниванию для всего интервала изменения р погрешности оцифровки таблиц d arcctg 2,(8) г г Д log2J sec(arcctg 2) , (9) занесенных соответственно в блоки памяти арккотангенсов 12 и секансов 10 С помощью блоков 12 и 10 выполняет ся перекодировка логарифма отношения X к у в значения фазового угла, дри веденного к первому октанту ot , и ло гарифма секанса этого угла Т . Сумма Д и Логарифма большего числа, получаемая в сумматоре 9, представляет собой логарифм произведения большей из координат на секанс прилегающего угла, т.е. логарифм модуля комплексного сигнала. Сумматор 9, выполненный в виде Двух линеек схем суммирования, помимо сложения кодов и Л вьшолняе также.сложение полученной суммы с дополнительным кодом логарифма нормирующего делителя, формируемого блоком 4 памяти Логарифмов. На выходе сумматора 9 формируется логарифм по основанию 2 отношения модуля комплекс ного сигнала к числу М. Устройство работает следующим образом. Исходные коды действительной и мнимой частей сигнала через первый и второй входы устройства подаются на первый и второй входы блока 1 преобразования, который по знаку чисел переводит отрицательные числа из дополнительных кодов в прямые. Перевод ос тцествляется путем инверсии допел- 11 58 нительного кода и прибавления к инверсному коду единицы младшего ратряда. Логарифмы мантисс большего и ме {ьшего чисел с выходов блоков 4 и 6 памяти логарифмов подаются на входы младших разрядов сумматора 5, на входы старших разрядов которого подаются порядки большего и меньшего чисел. Так как в блоках 3 и 6 порядок и логарифм мантиссы меньшего числа формируется в обратных кодах, на выходе сумматора 5 образуется разность логарифмов большего и меньшего чисел в прямом коде. В блоке формирования адреса мультиплексором 14 осуществляется сдвиг дробной насти /i вправо на число разрядов, соответствующее целой части , сдвинутое число округляется сумматором 15 по старшему из отбрасываемых разрядов, и недостающие старшие разряды при сдвиге числа согласно выражению (7) дополняются единицами. Таким образом, при нулевом порядке логарифмы мантисс уменьшаются в 2 раза, при /ij 1 в 4 раза, при /Ь 2 - в 8 раз и т.д. Так:ое формирование адреса позволяет получить погрешность оцифровки таблиц оС и для всего интервала изменения А не превьщгающую погрешности для /i D при одновременном возрастании объема таблиц ot и f всего в 2 раза по сравнению с объемом, необходимым для. /i 0. По адресу, сформированному блоком- 8 из блоков памяти секансов 10 и арккотангенсов 12 выбираются коды Л и od, которые затем поступают в сумматор 9 и блок 13 соответственно. Код о(. в блоке 13 суммируется или вычитается из констант 90, 180, 270, 360, вьщаваемых по значениям разрядов /X/ /у/, sign X, sign у. Код логарифма секанса складывается в сумматоре 9 с кодом логарифма больего числа. Из полученной суммы вычитается логарифм нормирующего делителя М, обратные коды целой и дробной астей которого считываются с выхода блока 7 памяти логарифмов по адресу, авному коду М. Дробная часть суммы, олученной на выходе сумматора 9, одается на вход блока памяти антиЛо- гарйфмов, с выхода которого мантисса одуля комплексного сигнала поступает на информационный вход линейки мульиплексора 16, на управлякндие входы которой поступает порядок модуля.

Таким образом, путем сдвига мантиссы влево на число разрядов, равное порядку модуля, осуществляется приведение кода к форме с фиксированной запятой. Сумматор 18 выполняет округление кода по старшему из отбрасываемых разрядов.Такое построение устройства позволяет расширить функциональные возможности преобразователя комплексных сигналов за счет введения операции нормирования модуля сигнала на весовой делитель, что часто бывает необходимым при построении анализаторов спектра Фурье с длительностью выборки, не выражаемой степенью числа 2, а также уменьшить объем запоминающих устройств, применяемых для формирования таблиц преобразований Сравним объемы таблиц

преобразований известного устройства и предлагаемого, полученных из условия равной точности вычислений. Для известного устройства объем таблицы определяется выражением (1). Объем таблиц для предлагаемого устройства равен

Ог (q,+ 2 ) ( 2) + + . (2а,.+ q

+ 4 )

(10)

0(1

41

В частности, при q, q q-. q .q 8, ЛР 0.

Q бит 1048576 бит, . Q 30-2 + 36352 бит,

что в 28,8 раза меньше по сравнению с известным устройством.

f

Фиг.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карбонизационная колонна | 1972 |

|

SU560634A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Силовая установка | 1985 |

|

SU1328567A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1984-07-23—Публикация

1983-03-10—Подача