Изобретение относится к вычислительной технике, в частности к системам ввода-вывода информации в ЭВМ, и может быть использовано в системах для передачи информации от источника к приемнику.

Известно устройство для ввода-вывода информации, содержащее фиксатор-накопитель данных, шестиразрядный вход которого является входом ключа для подключения к группе информационных выходов ЭВМ, три шестиразрядных счетчика, три задатчика начальных установок счетчиков, четыре селектора, четыре задатчика начального состояния селекторов, элемент И-ИЛИ, выход которого является выходом сигнала подтверждения ключа для подключения к информационному входу ЭВМ [1] .

Недостатком этого устройства является низкая надежность защиты информации от несанкционированного доступа, что обусловлено, во-первых, высокой вероятностью раскрытия начальных установок счетчиков (общее количество возможных комбинаций значений установок равно 25147); во-вторых, отсутствием дополнительной энергонезависимой памяти, в которой могут размещаться различные пароли и шифровальные ключи, доступные для прикладных программ ЭВМ по чтению.

Наиболее близким по технической сущности и достигаемому эффекту к предлагаемому устройству является устройство для сопряжения источника и приемника информации, содержащее блок памяти, информационный вход и выход которого являются соответствующими входом и выходом устройства для подключения к информационному выходу источника информации и информационному входу приемника информации, триггер, инверсный и прямой выходы которого являются соответствующими выходами устройства для подключения к входу разрешения записи источника информации и входу разрешения чтения приемника информации, счетчик, выход обнуления и информационный выход которого соединены соответственно с входом сброса триггера и адресным входом блока памяти, вход синхронизации которого подключен через элемент задержки к выходу элемента ИЛИ, вход режима работы блока памяти подключен к инверсному выходу триггера, первый и второй входы элемента ИЛИ являются соответственно входами устройства для подключения к выходу синхроимпульсов записи источника и выходу синхроимпульсов чтения приемника информации, дешифратор кода конца сообщения, информационный вход которого соединен с входом устройства для подключения информационного выхода источника информации, а выход - с установочным входом триггера, вход синхронизации дешифратора кода конца сообщения соединен с входом для подключения выхода синхроимпульсов записи источника информации и счетным входом счетчика, вычитающий вход которого соединен с входом устройства для подключения выхода синхроимпульсов чтения приемника информации, информационный выход счетчика соединен с выходом устройства для подключения к индикаторному входу приемника информации [2] .

Недостатком этого устройства является низкая надежность защиты информации от несанкционированного доступа, что обусловлено, во-первых, высокой вероятностью раскрытия кода сообщения, передаваемого от источника информации (ЭВМ) на информационный вход дешифратора кода сообщения, так как общее количество возможных комбинаций кодов сообщений для получения доступа к блоку памяти прототипа ограничено разрядностью информационного входа прототипа и не превышает значения 2n, где n - разрядность информационной шины источника информации, во-вторых, вероятность раскрытия начальной установки счетчика адреса близка к единице, что облегчает процедуру несанкционированного доступа к содержимому (к паролям) блока памяти в режиме чтения (в исходном состоянии на информационных выходах счетчика адреса могут быть либо все логические "0", либо все логические "1").

Целью изобретения является повышение надежности защиты информации от несанкционированного доступа.

Поставленная цель достигается тем, что в устройство для ввода-вывода информации, содержащее дешифратор кода данных, группа информационных входов которого является входом данных устройства для подключения к шине данных микроЭВМ, блок формирования адреса, блок постоянной памяти, группа адресных входов которого соединена с группой информационных выходов блока формирования адреса, а группа информационных выходов является выходом данных устройства для подключения к шине данных абонента, триггер готовности, выход которого соединен с входом режима блока формирования адреса и является выходом разрешения чтения устройства, введены первый и второй триггеры разрешения, элемент И, первый вход которого соединен с входом разрешения чтения блока постоянной памяти и является входом чтения устройства для подключения к выходу чтения микроЭВМ, входы сброса первого и второго триггеров разрешения и триггера готовности соединены и являются входом сброса устройства для подключения к выходу сброса микроЭВМ, входы сброса данных первого и второго триггеров разрешения и триггера готовности соединены и являются входом записи устройства для подключения к выходу записи микроЭВМ, выход первого триггера разрешения соединен с первым информационным входом дешифратора кода данных и с вторым входом элемента И, выход которого подключен к входу строба данных блока формирования адреса, группа параллельных входов данных которого соединена с группой информационных входов дешифратора кода данных и с группой информационных выходов блока постоянной памяти, выход второго триггера разрешения подключен к второму информационному входу дешифратора кода данных, первый, второй и третий выходы которого соединены с входами данных первого и второго триггеров разрешения и триггера готовности соответственно, при этом блок формирования адреса содержит два счетчика, группа параллельных входов данных которых являются группой параллельных входов данных блока формирования адреса, группа информационных выходов первого и второго счетчика являются группой информационных выходов блока формирования адреса, входы строба данных первого и второго счетчиков соединены и являются входом строба данных блока формирования адреса, вход разрешения счета и вход режима первого счетчика соединены с входом режима второго счетчика и являются входом режима блока формирования адреса, информационный выход первого счетчика подключен к входу разрешения счета второго счетчика.

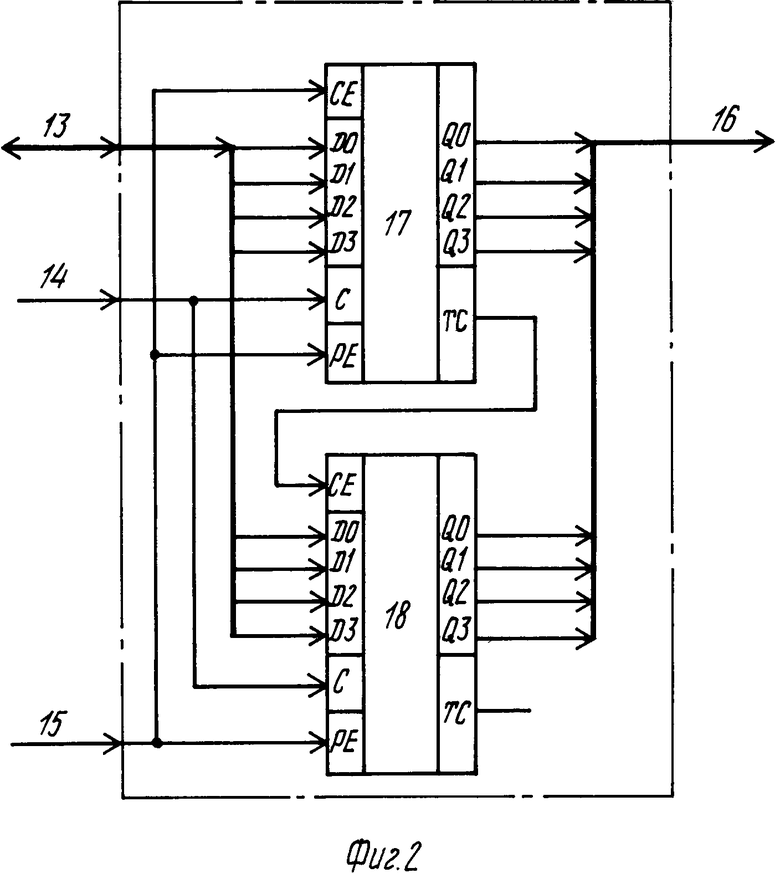

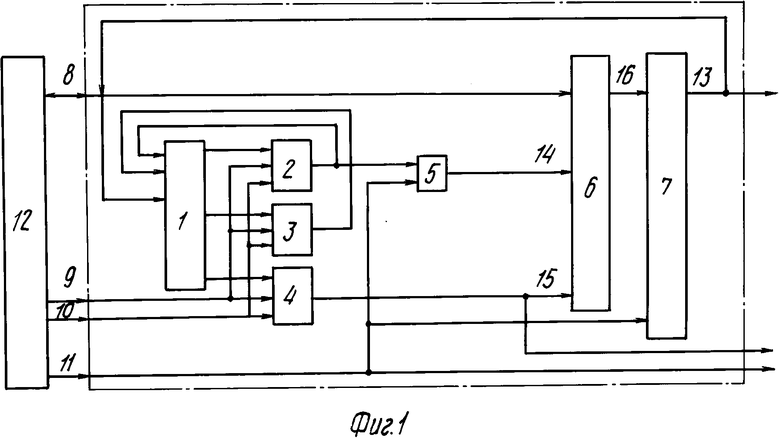

На фиг. 1 представлена структурная схема устройства для ввода-вывода информации; на фиг. 2 - схема блока формирования адреса.

Устройство содержит дешифратор 1 кода данных, первый и второй триггеры 2, 3 разрешения, триггер 4 готовности, элемент И 5, блок 6 формирования адреса, блок 7 постоянной памяти, вход 8 данных, вход 9 записи, вход 10 сброса и вход 11 чтения устройства для подключения соответственно к шине данных, выходам записи, сброса и чтения микроЭВМ 12, группу информационных выходов 13 блока 7, являющуюся выходом данных устройства для подключения к шине данных абонента, вход 14 строба данных, вход 15 режима блока 6, являющийся выходом разрешения чтения устройства, группу информационных выходов 16 блока 6.

Блок 6 формирования адреса (см. фиг. 2) содержит первый и второй счетчики 17, 18.

Дешифратор 1 кода данных предназначен для формирования сигнала логического "0" на одном из его информационных выходах при поступлении на информационные входы 8 дешифратора 1 соответствующего кодового набора логических нулей и единиц с шины данных микроЭВМ 12.

Триггеры 2, 3, 4 предназначены для записи информации с выходов дешифратора 1 при поступлении на вход 9 записи устройства строба данных с выхода записи микроЭВМ 12, элемент И 5 - для формирования строба данных при поступлении на вход 11 чтения устройства сигнала чтения с выхода чтения микроЭВМ 12, блок 6 - для формирования адреса ячейки постоянной памяти блока 7, блок 7 постоянной памяти - для хранения и вывода служебной информации длительного пользования (пароли, шифровальные ключи).

Устройство работает следующим образом.

В исходном состоянии триггеры 2, 3, 4 сброшены, на выходах дешифратора 1 и триггеров 2, 3, 4 присутствуют сигналы логических "1", блок 6 формирования адреса переведен в режим параллельной загрузки данных.

В произвольный момент времени микроЭВМ 12 выставляет на шине данных 8 первое слово данных и сопровождает его стробом записи по входу 9, в результате чего на первом информационном выходе дешифратора 1 вырабатывается логический "0", который стробом данных записывается в первый триггер 2 разрешения. На выходе триггера 2 вырабатывается логический "0", который поступает на первый информационный вход дешифратора 1, подготавливая его к распознаванию следующего слова данных от микроЭВМ 12.

Одновременно сигнал логического "0" с выхода триггера 2 поступает через элемент И 5 на вход 14 строба данных блока 6 формирования данных и подготавливает его к приему слова данных с шины данных 8. Затем микроЭВМ 12 выставляет на шине данных 8 второе слово данных и сопровождает его стробом записи по входу 9. При этом на первом и третьем информационных выходах дешифратора 1 присутствуют логические 1, на втором информационном выходе дешифратора 1 вырабатывается логический "0", которые стробом данных на входе 9 записываются в триггеры 2, 3, 4. На выходе триггера 2 вырабатывается сигнал логической "1" (положительный фронт, который через элемент И 5 поступает на вход 14 строба данных блока 6, в результате чего слово данных с шины данных 8 через группу параллельных входов 13 блока 6 записывается в его память (счетчики 16, 17, фиг. 2). Одновременно логическая "1" с выхода триггера 2 и логический "0" с выхода триггера 3 поступают на первый и второй информационные входы дешифратора 1, подготавливая его к распознаванию следующего слова данных микроЭВМ 12. После того, как микроЭВМ 12 выставит на шине данных и сформирует строб записи на входе 9, на выходе дешифратора 1 вырабатывается сигнал логического "0", который по стробу данных запишется в триггер 4 готовности. В результате этого на входе 15 режима блока 6 установится сигнал логического "0", который переведет блок 6 формирования адреса из режима параллельной загрузки в режим работы (режим разрешения счета и запрета загрузки параллельных данных счетчиков 16, 17, фиг. 2).

В режиме ввода-вывода информации микроЭВМ 12 выполняет операцию чтения данных из блока 6 путем подачи сигналов чтения на вход 11 чтения, при этом одновременно выполняется вывод информации абоненту. В качестве строба сопровождения данных абоненту может использоваться сигнал чтения на входе 11 блока 7. Достоверность передаваемых данных абоненту определяется сигналом разрешения чтения на выходе 15 устройства.

В процессе считывания информации из блока 7 микроЭВМ выставляет на входе 11 устройства сигналы чтения (логические "0"), которые поступают на вход разрешения чтения блока 7. При этом данные с группы информационных выходов 13 блока 7 могут считывать микроЭВМ 12 и абонент. При снятии сигнала чтения с входа 11 на первом входе элемента И 5 вырабатывается сигнал логической "1", в результате чего на входе 14 строба данных блока 6 формируется строб данных (положительный фронт перепада напряжения), который изменяет содержимое блока 6 (т. е. изменяется содержимое счетчиков 16, 17, фиг. 2). На выходе 16 блока 6 формируется адрес очередной ячейки памяти для следующего цикла обращения к блоку 7.

Таким образом устройство осуществляет ввод информации в микроЭВМ и вывод информации абоненту.

Дешифратор 1 может быть выполнен на базе микросхем К555 ИД7. К573 РФ2, триггеры 2, 3, 4 - на базе микросхем К555 ТМ2, К555 ТМ8, блок формирования адреса - на базе микросхемы К555 ИЕ17, К555 ИЕ16, блок 7 постоянной памяти - на микросхеме К573 РФ2, которая предварительно программируется под конкретную прикладную программу пользователя.

Указанные операции записи и считывания данных по шине данных 8 микроЭВМ 12 осуществляются в течение одного машинного цикла микроЭВМ, выполненной на базе микропроцессора КМ 1810 ВМ86. Машинный цикл записи (чтения) данных в блок 6 (из блока 7) устройства составляет четыре тактовых импульса, частота следования которых 5 МГц, причем запись информации в блок 6 может осуществляться по положительному перепаду сигнала записи, а чтение информации из блока 7 происходит в третьем такте машинного цикла. Активизация сигналов записи (вход 9) и чтения (вход 11) осуществляется во втором такте машинного цикла. (56) Гриншпан Л. А. и Левин Е. М. Электронные ключи для защиты информации. - Мир ПК, 1991, N 4, с. 69-73, рис. 1.

Авторское свидетельство СССР N 1661777, кл. G 06 F 13/00, 1990.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Устройство для объема информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1679497A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| УСТРОЙСТВО ДЛЯ ОТЛАДКИ МИКРОЭВМ | 1990 |

|

RU2015540C1 |

| Устройство для сопряжения двух ЭВМ с абонентами | 1988 |

|

SU1529237A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1566359A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

Изобретение относится к вычислительной технике, в частности к системам ввода-вывода информации в ЭВМ, и может быть использовано для защиты информации от несанкционированного доступа. Цель изобретения - повышение надежности защиты информации от несанкционированного доступа. Для этого устройство содержит дешифратор кода данных, два триггера разрешения и триггер готовности, элемент И, блок формирования адреса и блок постоянной памяти, группа информационных выходов которого соединена с группой информационных выходов дешифратора кода данных и с группой параллельных входов данных блока формирования адреса. 2 ил.

Авторы

Даты

1994-01-30—Публикация

1991-12-26—Подача