вого элемента И соединен с синхронизирующим входом регистра числа коэффициентов и со счетным входом первого счетчика, выходы которого соединены с входами первого дешифратора, первый, второй и третий выходы которого соединены с входом разрешения записи регистра числа коэффициентов первого и второго регистров значений коэффициентов соответственно, прямой выход первого триггера соединен с входами разрешения сдвига первого и второго регистров значений коэффициентов , выход В -го разряда (б ° 1 2, ...,п -1) первого регистра знагчений коэффициентов соединен с первым входом В -го блока умножения, выходы которого соединены с первой группой входов м -го комбинационного сумматора ( м 2 -П), выходы которого соединены с информационными входами t-го регистра результата, выходы которого соединены со второй группой входов М -го комбинационного сумматора, выход k-ro разряда (к 1, 2, ...,П ) втрого регистра значений коэффициенртон соединен с вторым входом с -го

блока умножения и с входом переноса младшего разряда М -го комбинационного сумматора, выходы которого соединены с -и группой информационных входов мультиплексора, выходы которого соединены с первым входами элементов И первой группы, а группа управляющих входов муЛьтиплексора соединена с выходами второго дешифратора, входы которого соединены с выходами второго счетчика, счетный вход которого соединен с выходом второго элемента И, первьй вход которого подклю чей к входу синхронизации устройства, второй вход второго элемента И соединен с прямым выходом первог триггера и с первыми входами элеметов И второй группы, вторые входы которых соединены с информационными входами регистра чисда коэффициентов, первого и второго регистров

80833

значений коэффициентов и подключены к группе информационных входов устройства, выходы элементов И второй группы соединены с входами множимого блоков умножения, выход второго элемента И через элемент НЕ соединён с первыми входами элементов И третьей группы, а второй вход k-го элемента И третьей группы соединен с к-м выходом второго дешифратора, вь1ходы элементов И третьей группы соединены с первыми входами элементов ИЛИ группы, выходы которых соединены с входами сброса регистров результатов, синхронизирующие входы которых соединены с выходом второго элемента И и с первым входом третьего элемента И, второй вход которого соединен с инверсным выходом второго триггера, а выход третьего элемента И соединен с синхронизирующим входом третьего счетчика, выходы которого соединены с первой группой входов блока сравнения, вторая группа входов которого соединена с выходами регистра числа коэффициентов, а выход соединен с входом установки второго триггера и с входом элемента задержки, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с входом признака сброса устройства в исходное положение, выход второго элемента ИЛИ соединен с входом установки в Q третьего счетчика, прямой выход второго триггера соединен с вторыми входами элементов И первой группы и с первым входом четвертого элемента И, второй вход которого соединен с выходом второго элемента И, выход четвертого элемента И подключен к выходу выдачи импульсов сопровождения устройства, а выходы элементов И первой группы соединены с информационными выходами устройства, выход признака сбоя устройства подключен к четвертому выходу первого дешифратора, вторые входы элементов ИЛИ группы соединены с выходом первого элемента ИЛИ.

1

Изобретение относится к вычислительной технике и предназначено для использования в слстемах цифровой обработки информации.

Целью изобретения является расширение функциональных возможносте путем обеспечения вычисления выражения вида

i+ktt

Н )

где 1 .а 1, 2, .,., К- числа кэффициентов .

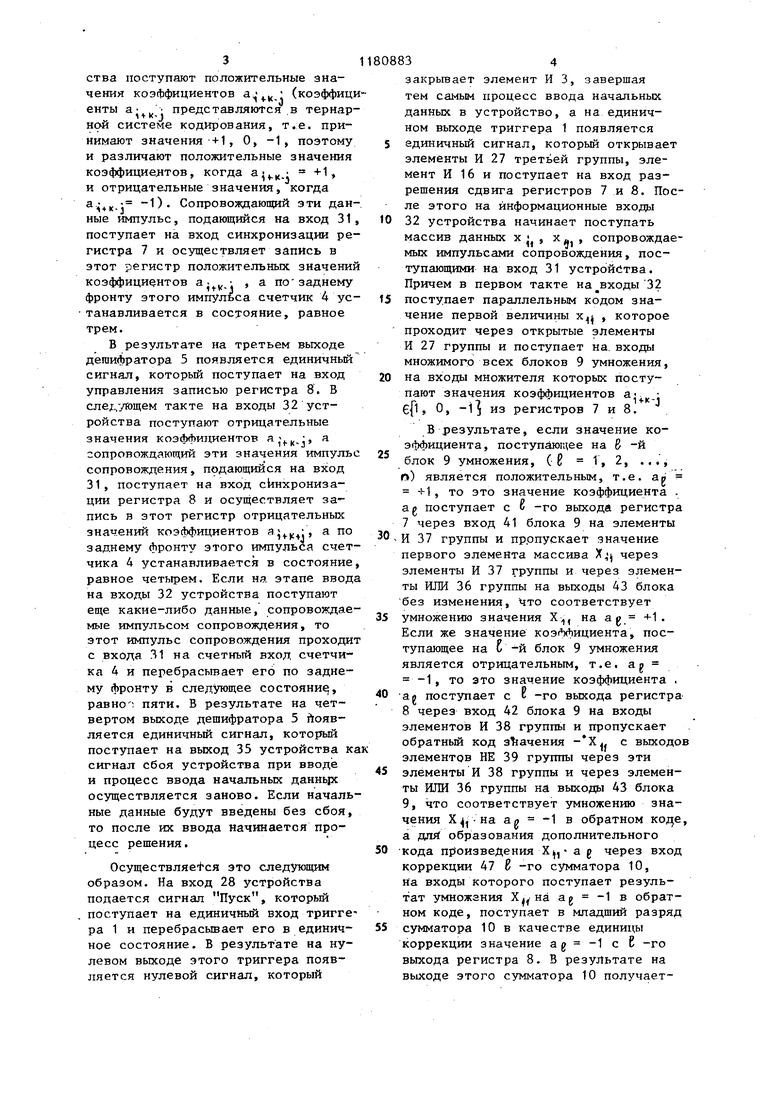

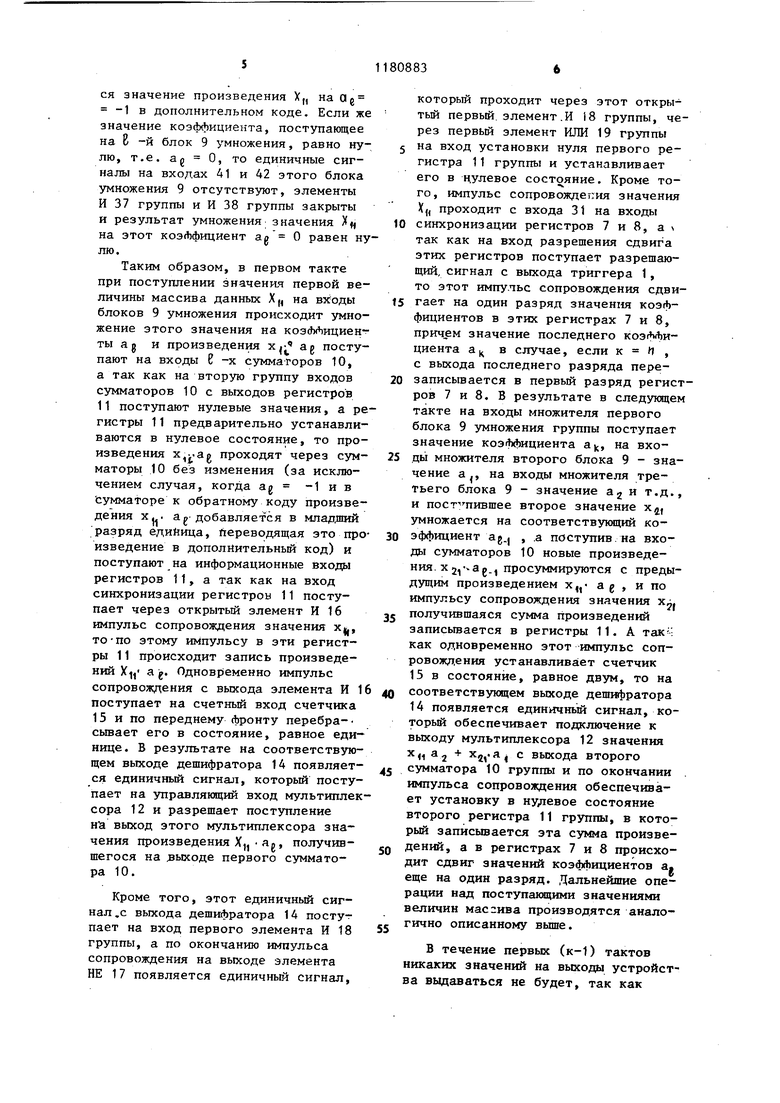

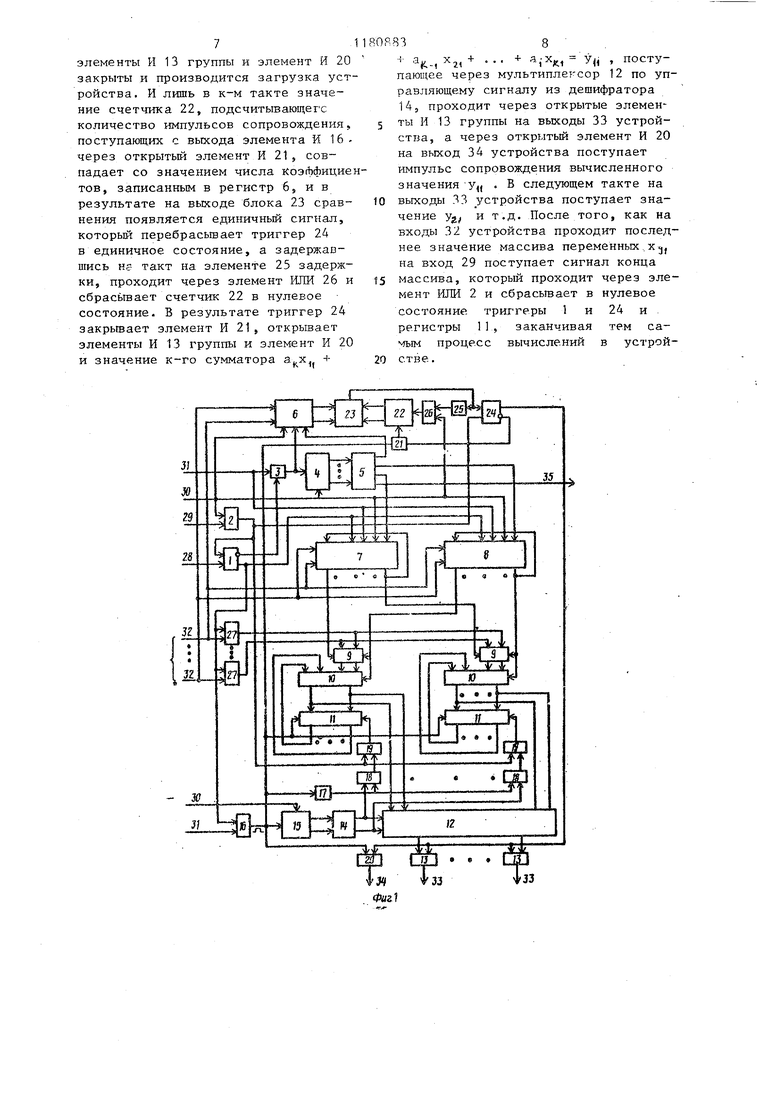

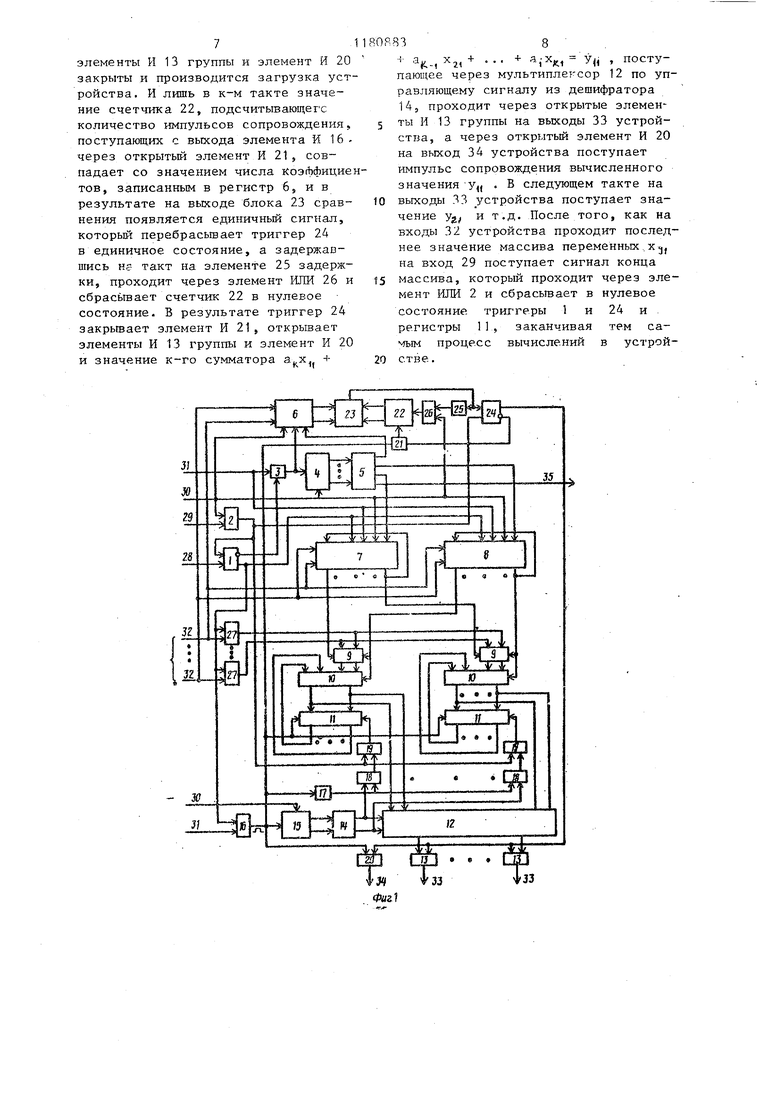

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - пример реализации блока умножения , на фиг. 3 - пример реализации комбинационного сумматора.

Устройство (фиг. 1) содержит первый триггер 1, первьй элемент ИЛИ 2, первьй элемент И 3, первый суммирующий счетчик 4, первьй дешифратор 5, регистр 6 числа коэффициентов, первьй регистр 7 значений коэффициентов, второй регистр

8значений коэффициентов, ц блоков

9умножения, h комбинационных сумматоров 10, п регистров 11 результатов, мультиплексор 12, первая группа элементов И 13, второй дешифратор 14, второй суммирующий счетчик 15, второй элемент И 16, элемент НЕ 17, вторая группа элементов И 18, группа элементов

ИЛИ 19, третий элемент И 20, четветьй элемент И 21, третий суммирующий счетчик 22, блок 23 сравнения, второй триггер 24, элемент 25 задержки, второй элемент ИЛИ 26, третья группа элементов .И 27.

Кроме того, устройство содержит вход 28 пуска устройства, вход 29 сигнала конца массива, вход 30 признака сброса, вход 31 импульсов сопровождения данных, информационные входы 32, информационные выходы 33, выход 34 импульсов сопровождения данных и выход 35 сбоя устройства . г

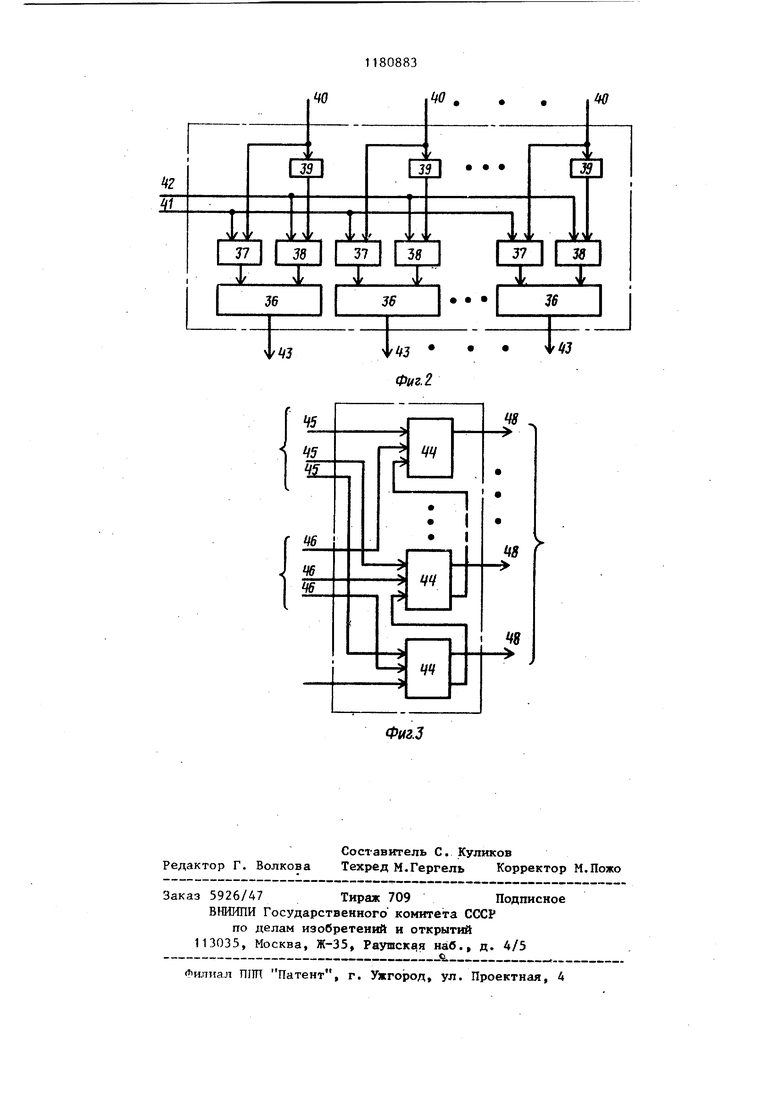

Блок 9 умножения (фиг. 2) содержит группу элементов ШЮ 36, первую группу элементов. И 37, вторую группу элементов И 38, группу элементов НЕ 39, группу входов 40 шожимого, первьй вход 41 значения множителя, второй вход 42 значения множителя и группу информационных выходов 43.

808832

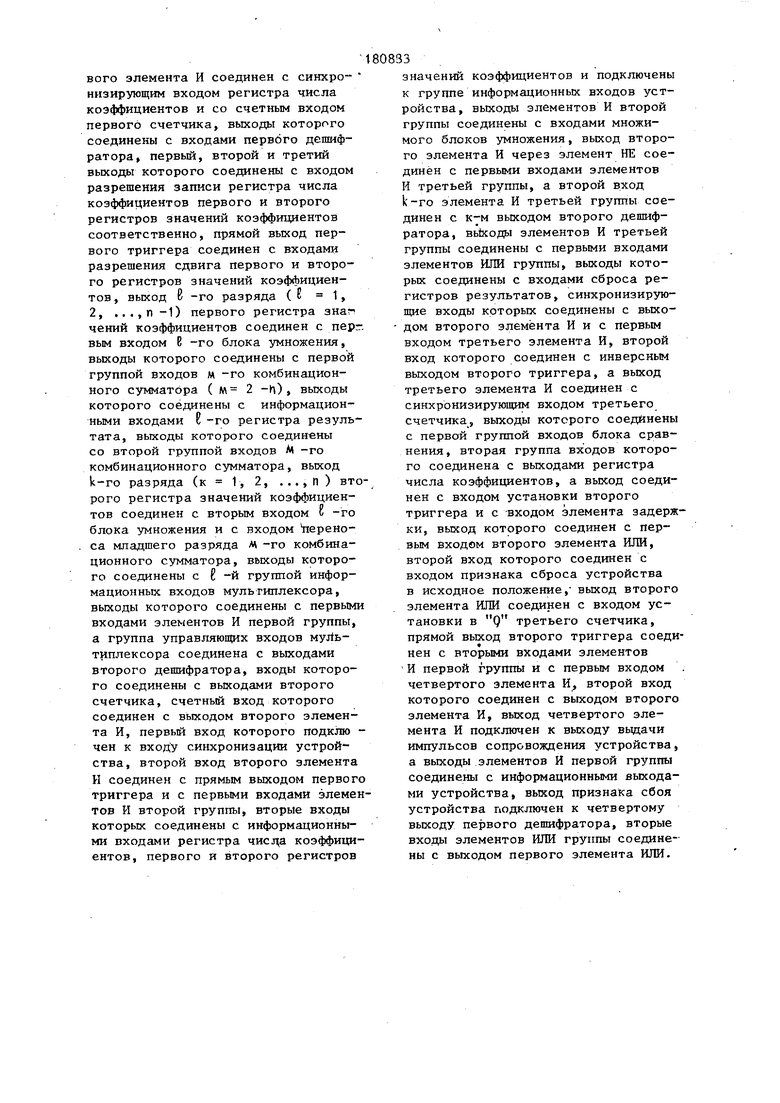

Комбинационньй сумматор (фиг. 3) содержит М одноразрядных .т.рехвходовых сумматоров 44, первую группу входов 45, вторую группу входов 5 46, вход 47 коррекщш и группу выходов 48.

Устройство работает следующим образом.

Перед началом работы подачей

10 сигнала на вход 30 сброса производится установка устройства в исходное состояние. При этом сигнал с входа 30 устанавливает в нулевое состояние регистры 6-8. счетчиts ки 4 и 15, а пройдя через элемент ИЛИ 26, устанавливает в нулевое состояние счетчик 22. Кроме того, пройдя через элемент ИЛИ 2, сигнал сброса с входа 30 устанавливает

20 в нулевое состояние триггеры 1 и 24j а пройдя с выхода элемента ИЛИ 2 через элементы ИЛИ 19 группы, этот сигнал устанавл1шает в нулевое состояние регистры 11.

Затем производится ввод начальных данных. При этом на вход 31 устройства поступает импульс, которьй проходит через открытьй элемент И 3 (так как триггер 1 установлен в нулевое состояние) на счетньй вход суммирующего счетчика 4 и по заднему фронту устанавливает этот счетчик в состояние, равное единице. В результате на первом

5 выходе дешифратора 5 появляетсяединичньй сигнал, который поступает на вход управления записью регистра 6. В следующем такте на информационные входы 32 устройства подается

параллельным кодом значение числа коэффициентов а, , равное k(,,i -l-i), и одновременно на вход 31 подается импульс, который проходит через открытьй элемент И 3

на вход синхронизации регистра 6 и осуществляет запись в этот регистр) значения числа крэф4)ициентов (К) , поступающего с входов 32 устройства на информационные входы этого ре гистра, а по заднему фронту этого импульса счетчик 4 устанавливается в состояние, равное двум.

В результате на втором входе дешифратора 5 появляется единичный сигнал, который поступает на вход упрабления записью,регистра 7. В следующем тактов на входы 32 устрой- ства поступают положительные значения коэффициентов (коэффиц енты представляются ,в тернар но-й системе кодирования, т.е. принимают значения +1, О, -1, поэтому и различают положительные значения коэффициентов, когда а. +1, и отрицательные значения, когда а. -1). Сопровождающий эти дан ные импульс, подающийся на вход 31 поступает на вход синхронизации ре гистра 7 и осуществляет запись в этот регистр положительных значени коэффициентов а., , а позаднему фронту этого импульса счетчик 4 ус танавливается в состояние, равное трем. В результате на третьем выходе дешифратора 5 появляется единичный сигнал, который поступает на вход управления записью регистра 8. В cлe yйщeм такте на входы 32 устройства поступают отрицательные значения коэффициентов а- , а сопровождающий эти значения импуль сопровождения, подающийся на вход 31, поступает на вход синхронизации регистра 8 и осуществляет запись в этот регистр отрицательных значений коэффициентов . по заднему фронту этого импульса счет чика 4 устанавливается в состояние равное четырем. Если на этапе ввод на входы 32 устройства поступают еще какие-либо данные, сопровождае мые импульсом сопровождения, то этот импульс сопровождения проходи с входа 31 на счетный вход счетчика 4 и перебрасьгоает его по заднему фронту в следующее состояни, равно пяти. В результате на четвертом выходе дешифратора 5 йоявляется единичный сигнал, который поступает на выход 35 устройства к сигнал сбоя устройства при вводе и процесс ввода начальных данньрс осуществляется заново. Если началь ные данные будут введены без сбоя, то после их ввода начинается процесс решения. Осуществляется это следующим образом. На вход 28 устройства подается сигнал Пуск, который поступает на единичный вход тригге ра 1 и перебрасывает его в единичное состояние. В результате на нулевом выходе этого триггера появляется нулевой сигнал, который закрьгеает элемент И 3, завершая тем самым процесс ввода начальных данных в устройство, а на единичном выходе триггера 1 появляется единичный сигнал, который открывает элементы И 27 третьей группы, элемент И 16 и поступает на вход разрешения сдвига регистров 7 и 8. После этого на информационные входы 32 устройства начинает поступать массив данных х . х , сопровождаемых импульсами сопровождения, поступающими на вход 31 устройства. Причем в первом такте на входы 32 поступает параллельным кодом значение первой величины х , которое проходит через открытые элементы И 27 группы и поступает на. входы множимого всех блоков 9 умножения, на входы множителя которых поступают значения коэффициентов а; „ ; 6fl О i из регистров 7 и 8. В результате, если значение коэффициента, поступающее на 6 -и блок 9 умножения, (6 1, 2, ..., г) является положительным, т.е. аи +1, то это значение коэффициента . ag поступает с S -го выхода регистра 7 через вход 41 блока 9 на элементы И 37 группы и пропускает значение первого элемента массива Х, через элементы И 37 группы и через элементы ИЛИ 36 группы на выходы 43 блока без изменения, то соответствует умножению значения Х,, на ао +1. Если же значение коэгЬфициента, поступающее на С -и блок 9 умножения является отрицательным, т.е. ag -1, то это значение коэффициента . ал поступает с К -го выхода регистра 8 через вход 42 блока 9 на входы элементов И 38 группь и пропускает обратный код значения Х. с выходов элементов НЕ 39 группы через эти элементы И 38 группы и через элементы ИЛИ 36 группы на выходы 43 блока 9, что соответствует умножению значения ag -1 в обратном коце, а дни образования дополнительного кода П15оизведения Х, а g через вход коррекции 47 6 -го сумматора 10, на входы которого поступает результат умножения ag -1 в обратном коде, поступает в младший разряд сумматора 10 в качестве единицы коррекции значение ag -1 с 6 -го выхода регистра 8. В результате на выходе этого сумматора 10 получается значение произведения Х„ на 0 -1 в дополнительном коде. Если же значение коэффициента, поступающее на 6 -и блок 9 умножения, равно нулю, т.е. ag О, то единичные сигналы на входах 41 и 42 этого блока умножения 9 отсутствуют, элементы И 37 группы и И 38 группы закрыты и результат умножения значения Х, на этот коэЛфициент ag О равен нулю.

Таким образом, в первом такте при поступлении значения первой величины массива данных Х„ на входы блоков 9 умножения происходит умножение этого значения на коэЛЛициенты а g и произведения ag поступают на входы 6 -X сумматоров 10, а так как на вторую группу входов сз мматоров 10 с выходов регистров 11 поступают нулевые значения, а регистры 11 предварительно устанавливаются в нулевое состояние, то произведения проходят через сумматоры 10 без изменения (за исключением случая, когда ag -1 и в Сумматоре к обратному коду произведения X,. а g-добавляется в младший разряд едийица, переводящая это произведение в дополНительньй код) и поступают на информационные входы регистров 11, а так как на вход синхронизации регистром 11 поступает через открытый элемент И 16 импульс сопровождения значения х,, тоПО этому импульсу в эти регистры 11 происходит запись произведений а g. Одновременно импульс сопровождения с выхода элемента И 1 поступает на счетный вход счетчика 15 и по переднему фронту перебра- сывает его в состояние, равное единице. В результате на соответствующем выходе дешифратора 14 появляется единичный сигнал, который поступает на управляклций вход мультиплексора 12 и разрешает поступление на выход этого мультиплексора значения произведения Х„ а, получившегося на выходе первого сумматора 10.

Кроме того, этот единичный сигнал,с выхода дешифратора 14 постут пает на вход первого элемента И 18 группы, а по окончанию импульса сопровождения на выходе элемента НЕ 17 появляется единичный сигнал.

который проходит через этот открытьй первьй. элемент.И 18 группы, через первьй элемент ИЛИ 19 группы 5 на вход установки нуля первого регистра 11 группы и устанавливает его в нулевое состояние. Кроме того, импульс сопровождения значения проходит с входа 31 на входы 10 синхронизации регистров 7 и 8, а так как на вход разрешения сдвига этих регистров поступает разрешающий, сигнал с выхода триггера 1, то этот импульс сопровождения сдвиts гает на один разряд значения коэффициентов в этих регистрах 7 и 8, причем значение последнего коэгЬФициента а в случае, если к Я , с выхода последнего разряда перезаписывается в первьй разряд регистров 7 и 8. В результате в следукяцем такте на входы множителя первого блока 9 умножения группы поступает значение коэффициента а, на вхо5 цы множителя второго блока 9 - значение а., на входы множителя третьего блока 9 - значение а и т.д., и пост пившее второе значение Xj, умножается на соответствующий коэффициент ag., , .а поступив на входы сумматоров 10 новые произведения, х j,-- а g., просуммируются с предыдущим произведением х,,- а g , и по импульсу сопровождения значения Xjj

r получившаяся сумма произведений записьтается в регистры 11. А такч как одновременно этот импульс сопровождения устанавливает счетчик 15 в состояние, равное двум, то на

0 соответствующем выходе дешифратора 14 появляется единичньй сигнал, которьй обеспечивает подключение к выходу мультиплексора 12 значения X,, а2 + с выхода второго

5 сумматора 10 группы и по окончании . импульса сопровождения обеспечивает установку в нулевое состояние второго регистра 11 группы, в который записывается эта сумма произвеQ дений, а в регистрах 7 и 8 происходит сдвиг значений коэффициентов а. еще на один разряд. Дальнейшие операции над поступакидими значениями величин массива производятся аналогично описанному выше.

В течение первых (к-1) тактов никаких значений на выходы устройства выдаваться не будет, так как 7 элементы И 13 группы и элемент И 20 закрыты и производится загрузка уст ройства. И лишь в к-м такте значение счетчика 22, подсчитывающегс количество импульсов сопровождения, поступающих с выхода элемента И 16через открытый элемент И 21, совпадает со значением числа коэффицие тов, записанным в регистр 6, и в результате на выходе блока 23 сравнения появляется единичный сигнал, который перебрасьшает триггер 2А в единичное состояние, а задержавшись на такт на элементе 25 задержки, проходит через элемент ИЛИ 26 и сбрасьгаает счетчик 22 в нулевое состояние. В результате триггер 24 закрьгоает элемент И 21, открывает элементы И 13 группы и элемент И 20 и значение к-го сумматора а,,,х,, + 3 К-, 2( поступающее через мультиплетсор 12 по управляющему сигналу из дешифратора 14, проходит через открытые элементы И 13 группы на выходы 33 устройства, а через открытый элемент И 20 на выход 34 устройства поступает импульс сопровождения вычисленного значения -у,, . В следующем такте на выходы 33 устройства поступает значение УЗ и т.д. После того, как на входы 32 устройства проходит последнее значение массива переменных , на вход 29 поступает сигнал конца массива, который проходит через элемент ИЛИ 2 и сбрасьтает в нулевое состояние триггеры 1 и 24 и регистры 11, заканчивая тем самым процесс вычислений в устройстве.

ЦЗ

ИЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления выражения вида @ | 1989 |

|

SU1644135A1 |

| Вычислительное устройство | 1987 |

|

SU1444759A1 |

| Вычислительное устройство | 1985 |

|

SU1272329A1 |

| Вычислительное устройство | 1985 |

|

SU1320804A1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Устройство для вычисления выражения @ | 1985 |

|

SU1357949A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее первый п -разрядный регистр значений коэффициентов, блок умножения, комбинационный сумматор и регистр результата, причем выходы комбинационного сумматора соединены с информационными входами регистра результата, выходы которого соединены с первой группой входов к;омбинационного сумматора, вторая группа входов которого соединена с выходами блока умножения, первый вход которого соединен с выходом п -го разряда регистра значений коэффициентов, о т л и -ч а ющ е е с я тем, что, с целью расширения его функциональных возможностей путем обеспечения вычисления выражения , , 4|l- -3H у ц - значения элементов преобразованного массива; Х- - значения элементов исход ного массиваj а- - значения коэффициентов, k - число коэффициентов, 1|

| Устройство для вычисления выражений вида | 1973 |

|

SU444193A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Шилейко А.В | |||

| Цифровые модели | |||

| М.: Энергия, 1964, с | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

| Рабинер Гоулд | |||

| Теория и применение цифровой обработки сигналов, М.: Мир, 1978 | |||

| / . | |||

Авторы

Даты

1985-09-23—Публикация

1984-03-11—Подача