S

Изобретение относится к системам управления и измерительной технике, предназначено для идентификации производ- ных сигнала полиномиальной формы и может быть использовано, например, в системах навигации и управления летательными аппаратами.

Известны устройства для многократного дифференцирования сигналов с помощью последовательно соединенных однотипных аналоговых или дискретных дифференциаторов.

Недостатком таких устройств является малая точность дифференцирования.

Известно устройство для распознавания формы сигнала, содержащее дискретизатор, вход которого является входом устройства, группу из n логических блоков, содержащих каждый элемент задержки, сумматор, пороговый элемент и коммутирующий элемент, причем вход элемента задержки является входом логического блока и соединен с первым входом сумматора, второй вход которого соединен с выходом элемента задержки, а выход, являющийся информационным выходом логического блока, соединен через пороговый элемент с входом коммутирующего элемента, выход которого является управляющим выходом логического блока, выход дискретизатора соединен с входом первого логического блока группы, вход каждого последующего логического блока группы соединен с информационным выходом предыдущего, матрицу коммутации, содержащую nхn ключей, причем ключи каждой строки матрицы соединены последовательно, управляющие входы ключей i-го столюца соединены с управляющим выходом i-го логического блока группы, i=  , в каждом i-м столбце первые i ключей являются размыкающими, а ключи с i+1 по n-замыкающими, генератор тактовых импульсов, выход которого соединен с управляющим входом дискретизатора, а входы строк матрицы соединены с шинной питания.

, в каждом i-м столбце первые i ключей являются размыкающими, а ключи с i+1 по n-замыкающими, генератор тактовых импульсов, выход которого соединен с управляющим входом дискретизатора, а входы строк матрицы соединены с шинной питания.

Это устройство не позволяет идентифицировать старшие производные от сигналов распознанной формы.

Цель изобретения - расширение функциональных возможностей за счет получения значений старших производных до n-го порядка.

Цель достигается тем, что в устройство введены делитель частоты, группы из n ключей и n масштабирующих элементов, выходы которых являются выходами устройства, при этом информационный выход i-го логического блока группы соединен с входом ключа i-й cтроки первого столбца матрицы, выходы ключей n-го столбца матрицы соединены через соответствующий ключ группы с входом соответствующего масштабирующего элемента.

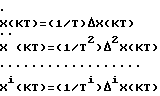

Устройство в зависимости от порядка n (формы) входного сигнала определяет значения старших производных по соотношениям при

; где Тi- период дискретности;

; где Тi- период дискретности;

Δi X(K T)- значение i-й разности сигналов, i = 1,2, . . . . n.

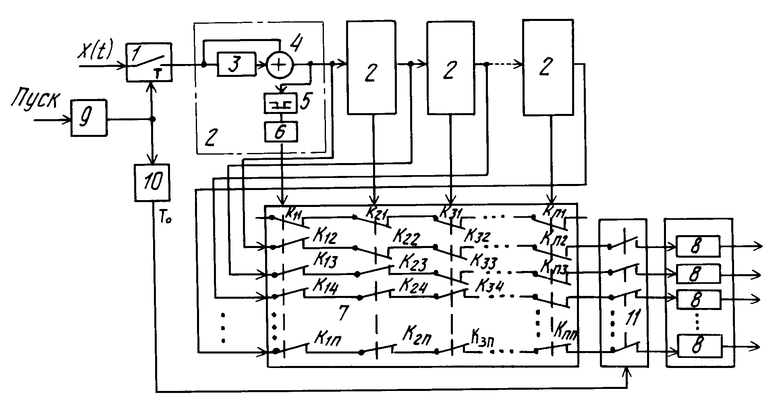

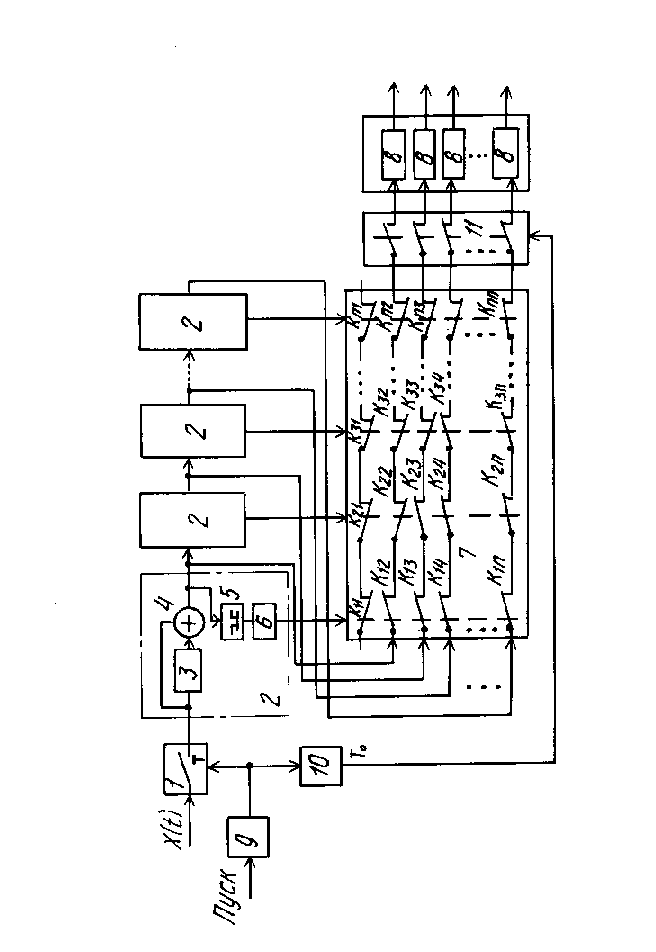

На чертеже изображена схема устройства.

Устройство содержит дискретизатор 1, логические блоки 2, каждый из которых состоит из элемента 3 задержки на Тс, cумматора 4, порогового элемента 5 и коммутирующего элемента 6, матрицу 7 коммутации, масштабирующие элементы 8, генератор 9 тактовых импульсов, делитель 10 частоты, группу 11 ключей.

Информационный выход i-го логического блока 2 в виде разности Δi X(K T) соединен с входом ключа i-й cтроки первого столбца матрицы 7 коммутации, выходы ключей n-го cтолбца матрицы соединены через соответствующий ключ группы 11 с выходом соответствующего масштабиру- ющего элемента 8, коэффициенты которых равны 1/Т, 1/Т2, 1/Т3, . . . , 1/Тn.

Входной аналоговый сигнал Х(t) дискретизатором 1 разбивается на дискретные по времени отсчеты, амплитудные значения которых поступают на вход последовательно соединенных логических блоков 2, на выходах которых формируются разности сигналов в виде ΔXi(K T). С помощью пороговых элементов 5 формируются условия прохождения разностей сигналов через соответствующую строку матрицы 7 коммутации, содержащей замыкающие и размыкающие ключи. Через интервал времени Тo = nТс cрабатывает группа 11 ключей от сигнала с делителя 10 частоты и своими замыкающими контактами подключает выходы строк матрицы 7 коммутации к входам масштабирующих элементов 8, в результате чего на одном из выходов устройства появляется импульсный сигнал, амплитуда которого равна старшей производной от полиномиального сигнала порядка n. Появление сигнала на первом, втором, третьем и так далее выходах n = 1,2,3, . . . ) свидетельствует и о том, что в конце интервала времени Тo имеет линейную, квадратическую, кубическую и т. д. форму изменения и этим обеспечивается сохранение функции основного устройства. В результате расширяются функциональные возможности за счет получения значений старших производных от сигналов известной формы.

Применение в технике устройства для идентификации производных полиномиального сигнала позволяет получить точные значения старших производных, пропорциональных внешнему воздействию, которые могут быть использованы в измерительной технике, автоматических системах для расчета, например, управления. (56) Авторское свидетельство СССР N 1330643, кл. G 06 K 9/00, 1985.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРОИЗВОДНЫХ ОТ КУСОЧНО-ПОЛИНОМИАЛЬНЫХ ФУНКЦИЙ | 1991 |

|

RU2047903C1 |

| АССОЦИАТИВНЫЙ КОММУТАТОР | 1991 |

|

RU2101760C1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

| Устройство для распознавания формы сигнала | 1985 |

|

SU1330643A1 |

| АССОЦИАТИВНЫЙ ВЫЧИСЛИТЕЛЬ СМЕЩЕНИЯ ЦЕНТРА ТЕКУЩЕГО ИЗОБРАЖЕНИЯ ОТ ЦЕНТРА ЭТАЛОННОГО | 1991 |

|

RU2029358C1 |

| Устройство для выполнения операций обращения матриц | 1985 |

|

SU1265796A1 |

| Устройство для диагностики технических систем | 1987 |

|

SU1444828A2 |

| Трехфазный стабилизатор переменного синусоидального напряжения дискретного действия | 1988 |

|

SU1576884A2 |

| Устройство коммутации для систем многоканального контроля и управления | 1985 |

|

SU1264206A1 |

| Устройство для усреднения дискретных сигналов | 1986 |

|

SU1474688A1 |

Использование: дискретные системы управления. Сущность изобретения: устройство содержит дискретизатор 1, логические блоки 2, содержащие каждый элемент 3 задержки, сумматор 4, пороговый элемент 5 и коммутирующий элемент 6, а также матрицу 7 коммутации, масштабирующие элементы 8, генератор 9, делитель 10 частоты, группу 11 ключей. 1 ил.

УСТРОЙСТВО ДЛЯ ИДЕНТИФИКАЦИИ ПРОИЗВОДНЫХ ПОЛИНОМИАЛЬНОГО СИГНАЛА, содержащее дискретизатор, вход которого является входом устройства, группу из n логических блоков, содержащих каждый элемент задержки, сумматор, пороговый элемент и коммутирующий элемент, причем вход элемента задержки является входом логического блока и соединен с первым входом сумматора, второй вход которого соединен с выходом элемента задержки, а выход, являющийся информационным выходом логического блока, соединен через пороговый элемент с входом коммутирующего блока, выход которого является управляющим выходом логического блока, выход дискретизатора соединен с входом первого логического блока группы, вход каждого последующего логического блока группы соединен с информационным выходом предыдущего, матрицу коммутации, содержащую n · n ключей, причем ключи каждой строки матрицы соединены последовательно, управляющие входы ключей i-го столбца соединены с управляющим выходом i-го логического блока групы i=  в каждом i-м столбце первые i ключей являются размыкающими, а ключи с (i + 1)-го по n-й замыкающими, генератор тактовых импульсов, выход которого соединен с управляющим входом дискретизатора, отличающееся тем, что, с целью расширения функциональных возможностей за счет получения значений старших производных до n-го порядка, в него введены делитель частоты, группа из n ключей и n масштабирующих элементов, выходы которых являются выходами устройства, при этом информационный выход i-го логического блока группы соединен с входом ключа i-й строки первого столбца матрицы, выходы ключей n-го столбца матрицы соединены через соответствующий ключ группы с входом соответствующего масштабирующего элемента.

в каждом i-м столбце первые i ключей являются размыкающими, а ключи с (i + 1)-го по n-й замыкающими, генератор тактовых импульсов, выход которого соединен с управляющим входом дискретизатора, отличающееся тем, что, с целью расширения функциональных возможностей за счет получения значений старших производных до n-го порядка, в него введены делитель частоты, группа из n ключей и n масштабирующих элементов, выходы которых являются выходами устройства, при этом информационный выход i-го логического блока группы соединен с входом ключа i-й строки первого столбца матрицы, выходы ключей n-го столбца матрицы соединены через соответствующий ключ группы с входом соответствующего масштабирующего элемента.

Авторы

Даты

1994-01-30—Публикация

1990-06-05—Подача