Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для связи процессоров с внешними устройствами, между процессорами, а также между процессорами и запоминающими устройствами.

Известно устройство для загрузки данных, содержащее группу входных регистров, регистр сдвига, группу регистров номера операнда, группу схем сравнения, две группы блоков элементов И, группу выходных регистров [1]

Недостатками данного устройства является низкое быстродействие и большой объем оборудования.

Известно устройство для распределения заданий процессорам, содержащее регистр готовности процессоров, регистр сдвига, две группы из n блоков элементов И (где n-число процессоров) и две группы из элементов ИЛИ, кодовый селектор и элемент И [2]

Недостатками устройства являются сравнительно низкая производительность и существенная сложность.

Наиболее близким по технической сущности к предлагаемому является устройство для сопряжения, содержащее N блоков согласования интерфейса, M регистров адреса и матрицу блоков коммутации размерностью N x M, причем первые информационные вход и выход i-го (i=1, N) блока согласования интерфейса являются соответственно i-м информационным входом м выходом устройства, информационный выход K-го (K=1,M) регистра адреса соединен с первыми информационными входами-выходами блоков коммутации K-го столбца матрицы, информационные входы и выходы блоков коммутации i-й строки матрицы соединена с вторыми информационными выходами и входом i-го блока согласования интерфейса соответственно, входы настройки синхронизации и начальной установки всех блоков коммутации матрицы соединены с входами настройки, синхронизации и начальной установки устройства соответственно, входы выборки регистров адреса с первого по М-й соединены с входом настройки устройства. Кроме того, вторые информационные входы-выходы блоков коммутации k-го столбца матрицы соединены между собой, управляющие входы блоков коммутации i-й строки соединены с управляющим выходом i-го блока согласования интерфейса. При этом блок коммутации содержит схему сравнения, триггер, элемент И, элемент ИЛИ-НЕ, элемент НЕ, два шинных формирователя, информационные входы и выходы которых являются соответственно информационным входом и выходом блока соответственно, информационные входы-выходы первого и второго шинных формирователей являются соответственно первым и вторым информационными входами-выходами блока, первый и второй входы схемы сравнения подключены соответственно к информационному входу и к первому информационному входу-выходу блока, выход схемы сравнения соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с входом установки триггера, выход которого соединен с первым входом элемента И, второй вход которого соединен с вторым входом элемента ИЛИ-НЕ и с входом настройки блока, входы сброса и синхронизации триггера являются входами начальной установки и синхронизации блока, выход элемента И соединен с входами выборки первого и второго шинных формирователей, вход направления передачи данных первого шинного формирователя соединен с управляющим входом блока и с входом элемента НЕ, выход которого соединен с входом направления передачи данных второго шинного формирователя [3]

Недостатком данного устройства является отсутствие возможности осуществлять двусторонний обмен информацией.

Целью изобретения является расширение функциональных возможностей за счет реализации возможности осуществления двустороннего обмена информацией.

Поставленная цель достигается тем, что в ассоциативный коммутатор, содержащий матрицу из M x N блоков коммутации (где M+N количество подключенных внешних устройств), i-й вход первой группы информационных входов устройства (i-1,M) соединен с первыми информационными входами блоков коммутации i-го столбца, i-й вход первой группы признаковых входов устройства соединен с первыми управляющими входами блоков коммутации i-го столбца, j-й (j=1,N)вход второй группы информационных входов устройства соединен с вторыми информационными входами блоков коммутации j-й строки, j-й вход второй группы признаковых входов устройства соединен с вторыми управляющими входами блоков коммутации j-й строки, первые входы блоков коммутации i-го столбца соединены с i-м выходом первой группы выходов устройства, вторые выходы блоков коммутации j-й строки соединены с j-м выходом второй группы выходов устройства. Причем каждый блок коммутации содержит компаратор и первый элемент И, первый и второй входы компаратора соединены соответственно с первым и вторым управляющими входами блока коммутации. Кроме того, каждый блок коммутации содержит второй элемент И и два элемента задержки, причем первый и второй информационные входы блока коммутации соединены соответственно с входами первого и второго элемента задержки, выходы которых соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены с выходом компаратора, выходы первого и второго элементов И соединены соответственно с первым и вторым выходами блока коммутации.

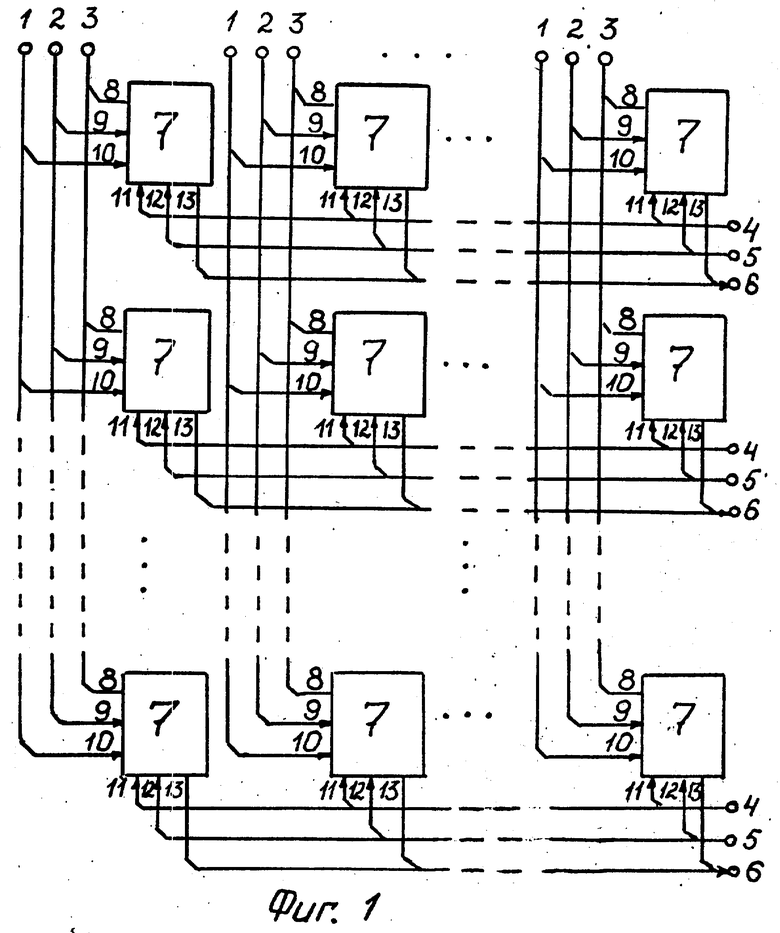

На фиг. 1 представлена структурная схема ассоциативного коммутатора; на фиг.2 структурная схема коммутационного элемента.

Ассоциативный коммутатор содержит группу признаковых входов 1, группу информационных входов 2, группу информационных выходов 3, группу информационных входов 4, группу признаковых входов 5, группу информационных выходов 6, матрицу M x N коммутационных элементов 7, где M+N количество подключенных внешних устройств, причем каждый коммутационный элемент 7 содержит группу информационных выходов 8, группу информационных входов 9, группы признаковых входов 10, 11, группу информационных входов 12, группу информационных выходов 13, группы элементов задержки 14, 15 с временами задержки, равными t14= t15=t16, логический компаратор 16, две группы ключей 17, 18.

Все элементы устройства известны и могут быть реализованы на основе серийной элементной базы по существующим методам инженерного проектирования, описанным, например, в [4]

Существенность отличительных признаков в формуле изобретения подтверждается тем фактом, что ни в патентной, ни в технической литературе не обнаружены указанные в отличительной части совокупности признаков изобретения. Сопоставительный анализ заявляемого устройства с прототипом показывает, что выявленные функции одно- и двунаправленного обмена информацией обеспечивается за счет выбора нужной информации по ассоциативному признаку. Поэтому можно сделать вывод, что заявляемое техническое решение соответствует критерию "новизна". Кроме того, следует отметить, что положительный эффект, полученный в результате использования совокупности признаков, значительно превышает эффект, который мог бы быть получен от использования каждого признака в отдельности.

Принцип действия устройства основан на сравнении ассоциативных признаков, поступающих на признаковые входы от подключенных внешних устройств. При их совпадении устройство обеспечивает прохождение информации, поступающей на информационные входы. Причем обеспечена возможность двустороннего обмена информацией между внешними устройствами и передачи информации от одного внешнего устройства к нескольким.

Устройство работает следующим образом.

Информационная посылка от i-го (i=1,M) внешнего устройства поступает через информационные входы 2 на информационные входы 9 i-го j-го (j=1,N) коммутационного элемента 7. Информационная посылка от j-го внешнего устройства поступает через информационные входы 5 на информационные входы 12 i-го j-го коммутационного элемента 7. С информационных входов 9 информационная посылка поступает на входы группы элементов задержки 15, а с информационных входов 12 на входы группы элементов задержки 14. Одновременно с информационными посылками поступающие ассоциативные признаки через входы 1, 4 поступают соответственно на признаковые входы 10, 11 i-го j-го коммутационного элемента 7, а через них соответственно на первую и вторую группу входов логического компаратора 16. В случае совпадения ассоциативных признаков с выхода логического компаратора 16 поступает сигнал на вторые входы групп ключей 17, 18, открывающий прохождение информационных посылок, поступающих с выходов групп элементов задержки 14, 15 на первые входы групп ключей 17, 18 соответственно. С выходов группы ключей 17 информационная посылка через информационные выходы 8 коммутационного элемента 7 поступает на информационные выходы 3 устройства. С выходом группы ключей 18 информационная посылка через информационные выходы 13 поступает на информационные выходы 6 устройства.

Промышленная реализуемость устройства обусловлена тем, что его схема может быть выполнена на существующей элементной базе. Область применения устройства может быть расширена за счет использования в аппаратуре связи и информационно-измерительной техники.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИДЕНТИФИКАЦИИ ПРОИЗВОДНЫХ ПОЛИНОМИАЛЬНОГО СИГНАЛА | 1990 |

|

RU2006944C1 |

| АССОЦИАТИВНЫЙ ВЫЧИСЛИТЕЛЬ СМЕЩЕНИЯ ЦЕНТРА ТЕКУЩЕГО ИЗОБРАЖЕНИЯ ОТ ЦЕНТРА ЭТАЛОННОГО | 1991 |

|

RU2029358C1 |

| Устройство для выполнения операций обращения матриц | 1985 |

|

SU1265796A1 |

| Устройство для диагностики технических систем | 1987 |

|

SU1444828A2 |

| УСТРОЙСТВО ЗАЩИТЫ ПАМЯТИ | 1990 |

|

RU2022343C1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

| УСТРОЙСТВО ТЕРМОКОМПЕНСАЦИИ КВАРЦЕВОГО ГЕНЕРАТОРА | 1990 |

|

RU2007839C1 |

| УСТРОЙСТВО ДЛЯ РЕКОНФИГУРАЦИИ МНОГОМАШИННОГО ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА | 1991 |

|

RU2022342C1 |

| УНИВЕРСАЛЬНЫЙ ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК ПО МОДУЛЮ M - ДЕШИФРАТОР КОЛИЧЕСТВА ЕДИНИЦ В N-РАЗРЯДНОМ ДВОИЧНОМ КОДЕ | 1991 |

|

RU2020744C1 |

| УСТРОЙСТВО СВЕРТКИ ПО ПЕРЕМЕННОМУ МОДУЛЮ | 1991 |

|

RU2051408C1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для связи процессоров с внешними устройствами, между процессорами, а также между процессорами и запоминающими устройствами. Целью изобретения является расширение функциональных возможностей за счет реализации возможности осуществления двустороннего обмена информацией. Поставленная цель достигается тем, что ассоциативный коммутатор содержит группу прзнаковых входов 1, группу информационных входов 2, группу информационных выходов 3, группу информационных входов 4, группу признаковых входов 5, группу информационных выходов 6, матрицу из M x N коммутационных элементов 7, где M+N - количество подключенных внешних устройств, причем каждый коммутационный элемент 7 содержит группу информационных выходов 8, группу информационных входов 9, группы признаковых входов 10, 11, группу информационных входов 12, группу информационных выходов 13, группы элементов задержки 14, 15, логический компаратор 16, две группы ключей 17, 18. Принцип действия устройства основан на сравнении ассоциативных признаков, поступающих на признаковые входы от подключенных внешних устройств. При их совпадении устройство обеспечивает прохождение информации, поступающей на информационные входы. Причем обеспечена возможность двустороннего обмена информацией между внешними устройствами и передачи информации от одного внешнего устройства к нескольким. 2 ил.

Ассоциативный коммутатор, содержащий матрицу из М х П блоков коммутации (где М + П количество подключенных внешних устройств), i-й вход первой группы информационных входов устройства (i 1, М) соединен с первыми информационными входами блоков коммутации i-го столбца, i-й вход первой группы признаковых входов устройства соединен с первыми управляющими входами блоков коммутации i-го столбца, j-й (j 1, П) вход второй группы информационных входов устройства соединен с вторыми информационными входами блоков коммутации j-й строки, j-й вход второй группы признаковых входов устройства соединен с вторыми управляющими входами блоков коммутации j-й строки, первые выходы блоков коммутации i-го столбца соединен с i-м выходом первой группы выходов устройства, вторые выходы блоков коммутации j-й строки соединены с j-м выходом второй группы выходов устройства, причем каждый блок коммутации содержит компаратор и первый элемент И, первый и второй входы компаратора соединены соответственно с первым и вторым управляющими входами блока коммутации, отличающийся тем, что каждый блок коммутации содержит второй элемент И и два элемента задержки, причем первый и второй информационные входы блока коммутации соединены соответственно с входами первого и второго элементов задержки, выходы которых соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены с выходом компаратора, выходы первого и второго элементов И соединены соответственно с первым и вторым выходами блока коммутации.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для загрузки данных | 1983 |

|

SU1103236A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР N 9764342, G 06 F 9/00, 1982 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для сортировки данных | 1982 |

|

SU1277088A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Потемкин И.С | |||

| Функциональные узлы цифровой автоматики | |||

| - М.: Энергоатомиздат, 1988. | |||

Авторы

Даты

1998-01-10—Публикация

1991-12-10—Подача