Изобретение относится к распознающим и измерительным устройствам, дискретным системам управления и предназначено для формирования производных от кусочно-полиномиальных сигналов порядка n≅ 3.

Известны устройства для многократного дифференцирования дискретных сигналов, содержащие последовательно соединенные однотипные дискретные дифференциаторы, например, по правилу прямоугольника.

Недостатком таких устройств является малая точность, зависящая, в основном, от формы входного сигнала, способа дифференцирования, периода дискретности.

Известно устройство для распознавания формы сигнала, содержащее квантователь, блоки формирования приращений и сигналов управления, матрицу ключей, каждая строка которой образована последовательно соединенными ключами, информационные входы ключей первого столбца матрицы ключей соединены с шиной положительного потенциала, информационным входом устройства является вход квантователя, выход которого подключен к выходу первого блока формирования приращений (логический блок), первый выход каждого блока формирования приращений, кроме последнего блока, подключен ко входу последующего блока формирования приращений, второй выход каждого блока формирования приращений соединен с управляющими входами ключей одноименного столбца матрицы.

Это устройство не позволяет формировать производные от сигналов распознанной формы в дискретные моменты времени t=кТ.

Цель изобретения состоит в расширении функциональных возможностей базового устройства путем формирования всех производных от сигналов кусочно-полиномиальной формы порядка n≅3.

Цель достигается тем, что в базовое устройство введены блок коммутации, включающий три канала, и три блока вычисления производных, причем первый канал блока коммутации содержит ключевой элемент, второй канал блока коммутации содержит два ключевых элемента, третий канал блока коммутации содержит три ключевых элемента, первый блок вычисления производных содержит умножитель, второй блок вычисления производных содержит сумматор и три умножителя, третий блок вычисления производных содержит пять умножителей и два сумматора, первый выход первого блока формирования приращений подключен к информационному входу ключевого элемента первого канала блока коммутации и к информационным выходам первых ключевых элементов второго и третьего каналов блока коммутации, первый выход второго блока формирования приращений соединен с информационными входами вторых ключевых элементов второго и третьего каналов блока коммутации, первый выход третьего блока формирования приращений подключен к информационному входу третьего ключевого элемента третьего канала блока коммутации, управляющие входы ключевых элементов первого, второго и третьего каналов блока коммутации подключены к выходам ключей соответственно первой, второй и третьей строк матрицы ключей, выход ключевого элемента первого канала блока коммутации соединен с входом умножителя первого блока вычисления производных, выход которого является первым выходом устройства, выход первого ключевого элемента второго канала блока коммутации подключен к первому входу сумматора второго блока вычисления производных, второй вход которого соединен с входом первого умножителя, а выход подключен к входу второго умножителя своего блока, выход которого является вторым выходом устройства, выход второго ключевого элемента второго канала блока коммутации соединен с входами первого и третьего умножителей второго блока вычисления производных, выход которого является третьим выходом устройства, выход первого ключевого элемента третьего канала блока коммутации подключен к первому входу сумматора третьего блока вычисления производных, второй и третий входы которого соединены с выходами соответственно первого и второго умножителей третьего блока вычисления производных, выход второго ключевого элемента третьего канала блока коммутации подключен к входу первого умножителя и первому входу второго сумматора третьего блока вычисления производных, второй вход второго сумматора, входы второго и третьего умножителей третьего блока вычисления производных объединены и подключены к выходу третьего ключевого элемента третьего канала блока коммутации, выходы второго и третьего сумматоров третьего блока вычисления производных соединены с входами четвертого и пятого умножителей этого блока, выходы которых являются соответственно четвертым и пятым выходами устройства, шестым выходом которого является выход третьего умножителя третьего блока вычисления производных.

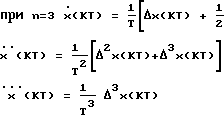

Устройство в зависимости от формы (порядка n) сигнала формирует производные в блоках поканально по зависимостям:

при n=1  (кт)

(кт)  Δx(кт)

Δx(кт) 2

2 т

т x(кт) +

x(кт) +  Δ2x(кт)

Δ2x(кт)

Δ2x(кт) +

Δ2x(кт) +  Δ3(кт)

Δ3(кт)

(1) где Δх(кт)=х(кт)-х[(к-1)т]

Δ2х(кт)= Δ х(кт)-Δ х[(к-1)n]

Δ3х(кт)= Δ2х(кт)- Δ2х[(к-1)т]

Т период дискретности.

Сопоставительный анализ с известным устройствам показывает, что заявляемое устройство отличается тем, что оно дополнительно содержит блок коммутации, включающий три канала соответственно имеющих один, два и три ключевые элемента, и три блока вычисления производных, содержащие сумматоры и умножители, с определенными весовыми коэффициентами, причем управляющие входы первого, второго и третьего каналов блока коммутации подключены к выходам ключей соответственно первой, второй и третьей строк матрицы ключей, а информационные входы каналов блока коммутации к выходам блоков формирования приращений, выходы каналов блока коммутации соединены с соответствующими входами трех блоков вычисления производных.

Таким образом, заявляемое устройство соответствует критерию изобретения "НОВИЗНА".

Сравнение заявляемого решения с прототипом и другими решениями в данной области техники не позволило выявить в них признаки, отличающие заявляемое решение от прототипа, что позволяет сделать вывод о соответствии критерию "Существенные отличия".

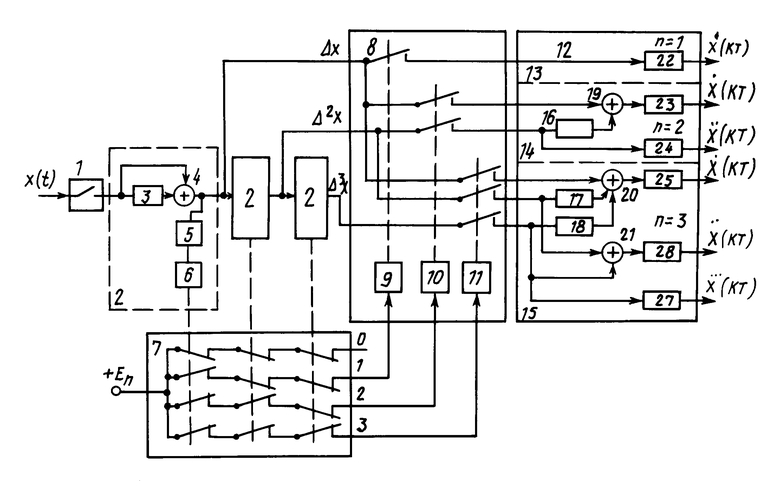

На чертеже представлена схема предлагаемого устройства. Она содержит квантователь 1, три блока формирования приращений 2, каждый из которых содержит элемент задержки 3, сумматор 4, пороговый элемент 5, матрицу ключей 7, блок коммутации 8, ключевые элементы 9, 10, 11 первого, второго, и третьего каналов блока коммутации, общий блок вычисления производных 12, содержащий первый, второй и третий блоки 13, 14, 15 вычисления производных от сигналов соответственно порядка n=1, 2, 3, содержащие умножители 16, 17, 18 с коэффициентами соответственно равными 1/2, 1/2, 1/3, сумматоры 19, 20, 21 на два и три входа, умножители 22-27 с коэффициентами соответственно равными 1/T, 1/T, 1/T2, 1/T, 1/T, 1/T2, 1/T3, где Т период дискретности квантователя 1 по времени.

Информационные выходы с первого третьего блоков формирования приращений 2, в виде разностей Δх(кт), Δ2х(к), Δ3х(кт) от входного сигнала х(t), соединены с входами блоков 13, 14, 15 вычисления производных через ключевые элементы блока коммутации 8, управляющие входы которых подключены к выходам строк матрицы 7 ключей.

Устройство работает следующим образом. Входной сигнал х(t) подается на квантователь 1, с выхода которого амплитудные значения в виде х(кт), к=1, 2, 3. подаются на вход последовательно соединенных блоков приращения 2, где формируются разности Δx,Δ2x,Δ3x.

С помощью пороговых элементов 5, коммутирующих элементов 6 и ключевых элементов матрицы 7 определяется форма х(t) в виде сигнала на одном из выходов 1, 2, 3 матрицы ключей 7, от которых срабатывают ключевые элементы 9, 10, 11 каналов блока коммутации 8 и разности сигналов подаются на входы одного из блоков 13, 14, 15 вычисления производных. В этих блоках, в зависимости от значения n=1, 2, 3, реализуются соотношения (1);

В зависимости от порядка полинома n=1, 2, 3 входного сигнала на интервале времени То= 3Т с выходов блоков вычисления производных следуют импульсные сигналы, амплитудные значения которых равны производным от х(t) в дискретные моменты времени t=кт.

Вначале работы, когда еще не накоплена прошлая информация в виде х(к-1), х(к-2), х(к-3), устройство не может формировать точные значения производных и только через первый интервал времени То=3Тс можно получать производные через каждые Тс. Этот недостаток характерен для всех дискретных систем и устройств, в которых используется не только текущая, но и прошлая информация, которая накапливается, циркулируется и теряется.

Применение в технике предлагаемого устройства для формирования производных от кусочно-полиноминальных функций, порядок которых (форма) n≅3, позволит получить точные значения всех производных, которые могут быть использованы в различных областях техники, в том числе и в системах управления для расчета оптимального управления объектами при минимальном числе датчиков состояния. Особенно полезно применять устройство в адаптивных системах автоматического управления объектами с заранее неопределенной структурой.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНАЯ СИСТЕМА УПРАВЛЕНИЯ | 1992 |

|

RU2066874C1 |

| Адаптивная система интегрирования дискретных сигналов | 1986 |

|

SU1439630A1 |

| УСТРОЙСТВО ДЛЯ ИДЕНТИФИКАЦИИ ПРОИЗВОДНЫХ ПОЛИНОМИАЛЬНОГО СИГНАЛА | 1990 |

|

RU2006944C1 |

| Адаптивная система управления | 1987 |

|

SU1495744A1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ С ПОВЫШЕННОЙ СЛОЖНОСТЬЮ | 1999 |

|

RU2153230C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2004 |

|

RU2287909C2 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПРОВЕРКИ ЗАВЕРЕННОГО ЦИФРОВЫМ ВОДЯНЫМ ЗНАКОМ ЭЛЕКТРОННОГО ИЗОБРАЖЕНИЯ | 2009 |

|

RU2411579C1 |

| Кодер сигнала изображения | 1990 |

|

SU1730724A1 |

| Детерминированно-вероятностный интегратор | 1979 |

|

SU857990A1 |

| Устройство для управления технологическим процессом | 1988 |

|

SU1522238A1 |

Изобретение относится к распознающим устройствам, измерительной технике и дискретным системам управления, в частности к адаптивным. Цель изобретения расширение функциональных возможностей устройства для определения формы сигнала путем получения всех производных от полиномиальных сигналов порядка n≅3. Это достигается тем, что в базовое устройство дополнительно введены: трехканальный блок коммутации и три блока вычисления производных, содержащие девять умножителей с определенными коэффициентами и три сумматора на два и три входа. 1 ил.

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРОИЗВОДНЫХ ОТ КУСОЧНО-ПОЛИНОМИАЛЬНЫХ ФУНКЦИЙ, содержащее квантователь, три блока формирования приращений и матрицу ключей, каждая строка которой образована последовательно соединенными ключами, информационные входы ключей первого столбца матрицы ключей соединены с шиной положительного потенциала, информационным входом устройства является вход квантователя, выход которого подключен к входу первого блока формирования приращений, первый выход каждого блока формирования приращений, кроме последнего, подключен к входу последующего блока формирования приращений, второй выход каждого блока формирования приращений соединен с управляющими входами ключей одноименного столбца матрицы, отличающееся тем, что в него введены блок коммутации, включающий три канала, и три блока вычисления производных, причем первый канал блока коммутации содержит ключевой элемент, второй канал два ключевых элемента, третий канал три ключевых элемента, первый блок вычисления производных содержит умножитель, второй блок сумматор и три умножителя, третий блок пять умножителей и два сумматора, первый вход первого блока формирования приращений подключен к информационному входу ключевого элемента первого канала блока коммутации и к информационным входам первых ключевых элементов второго и третьего каналов блока коммутации, первый выход второго блока формирования приращений с информационными входами вторых ключевых элементов и третьего каналов блока коммутации, первый выход третьего блока формирования приращений подключен к информационному входу третьего ключевого элемента третьего канала блока коммутации, управляющие входы ключевых элементов первого, второго и третьего каналов блока коммутации подключены к выходам ключей соответственно первой, второй и третьей строк матрицы ключей, выход ключевого элемента первого канала блока коммутации соединен с входом умножителя первого блока вычисления производных, выход которого является первым выходом устройства, выход первого ключевого элемента второго канала блока коммутации подключен к первому входу сумматора второго блока вычисления производных, второй вход которого соединен с выходом первого умножителя, а выход подключен к входу второго умножителя своего блока, выход которого является вторым выходом устройства, выход второго ключевого элемента второго канала блока коммутации соединен с входом первого и третьего умножителей второго блока вычисления производных, выход которого является третьим выходом устройства, выход первого ключевого элемента третьего канала блока коммутации подключен к первому входу сумматора третьего блока вычисления производных, второй и третий входы которого соединены с выходами соответственно первого и второго умножителей третьего блока вычисления производных, выход второго ключевого элемента третьего канала блока коммутации подключен к входу первого умножителя и первому входу второго сумматора третьего блока вычисления производных, второй вход второго сумматора, входы второго и третьего умножителей третьего блока вычисления производных объединены и подключены к выходу третьего ключевого элемента третьего канала блока коммутации, выходы второго и третьего сумматоров третьего блока вычисления производных соединены с входами четвертого и пятого умножителей этого блока, выходы которых являются соответственно четвертым и пятым выходами устройства, шестым выходом которого является выход третьего умножителя третьего блока вычисления производных.

| Устройство для распознавания формы сигнала | 1985 |

|

SU1330643A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-11-10—Публикация

1991-11-04—Подача