Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти на базе БИС запоминающих устройств со словарной организацией обращения.

Известно запоминающее устройство с самоконтролем [1] , содержащее адресный блок, накопитель, шифратор, две группы элементов И, блок контроля, сумматоры по модулю два, элемент ИЛИ. Шифратор и блок контроля состоят из сумматоров по модулю два. Устройство позволяет исправить одиночные и кратные отказы в каждом слове накопителя из-за отказа интегральной микросхемы памяти (ИМП) с единичными сигналами на выходах при наличии b + l дополнительных разрядов, где l =  , К - число информационных разрядов; b - разрядность интегральной схемы памяти.

, К - число информационных разрядов; b - разрядность интегральной схемы памяти.

Это устройство корректирует только такие отказы, которые приводят к появлению единичных сигналов на группе выходов, принадлежащих одной ИМП.

Наиболее близким к изобретению является запоминающее устройство с исправлением ошибок [2] , которое содержит основной и дополнительный накопители, блок выборки адресов, дешифратор, блок контроля, регистр числа и элементы И по числу разрядов основного накопителя.

Недостатками этого устройства являются исправление только одиночной ошибки в слове, необходимость большого объема дополнительной памяти для запоминания информации об искажении большой области памяти, что возможно при отказе большой интегральной схемы памяти и увеличение времени обращения при наличии ошибки за счет задержки информации на регистре числа для коррекции.

Целью изобретения является повышение надежности, быстродействия и упрощение устройства.

Цель достигается тем, что в устройство, содержащее информационные блоки памяти основного накопителя, блока памяти контрольных разрядов, дополнительный накопитель, блоки контроля, элементы И, введены элементы ИСКЛЮЧАЮЩЕЕ ИЛИ по числу разрядов основного накопителя, вторые входы которых соединены с выходами элементов И, формирующих признак коррекции разряда по совпадению единичного значения сигнала с выхода контрольного блока, означающего наличие ошибки в группе разрядов информации с выходов основного носителя, принадлежащих разным блокам, и единичного значения сигнала с выхода дополнительного накопителя, соответствующего наличию дефекта в определенном блоке основного накопителя.

Эффективность применения предлагаемого устройства наиболее высока при использовании для построения накопителя БИС памяти большой информационной емкости. При неисправности БИС устройство корректирует ошибки во всей информации неисправной БИС в каждом ряду.

Анализ известных решений исследуемой отрасли показал, что известно запоминающее устройство с самоконтролем [1] , содержащее аналогичные элементам ИСКЛЮЧАЮЩЕЕ ИЛИ предлагаемого устройства сумматоры по модулю два, одни входы которых подключены к выходам накопителя, другие - к выходам группы элементов И, формирующих признаки коррекции информации соответствующего разряда. Но в этом устройстве один вход каждого элемента группы элементов И связан с выходом элемента ИЛИ, входы которого связаны с выходами блока контроля, а второй вход - с выходом элемента И другой группы элементов И, входы которых связаны с выходами группы разрядов накопителя. Признак коррекции разряда выходной информации формируется этой схемой по совпадению условия наличия ошибки в считываемой информации с условием наличия ошибочных единичных выходов группы разрядов накопителя, соответствующих одной интегральной схеме памяти.

Таким образом, признаков, отличающих предложенное техническое решение от прототипа, в известных технических решениях не имеется, т. е. заявленное техническое решение соответствует критерию "существенные отличия".

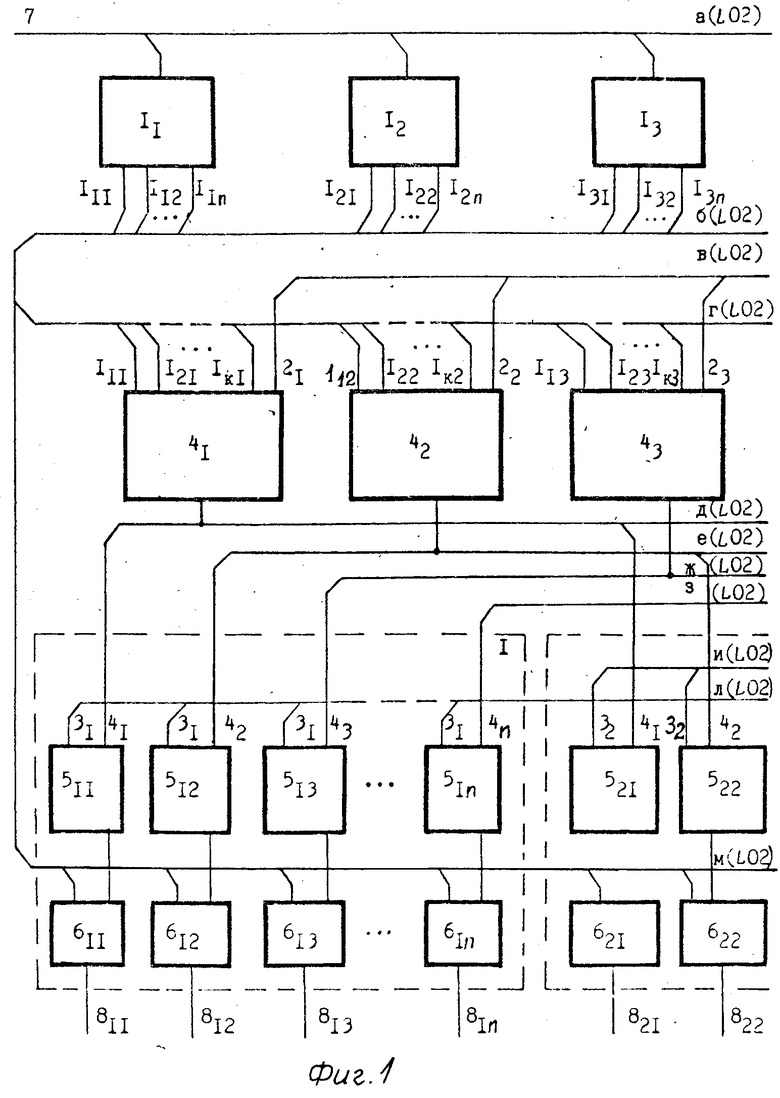

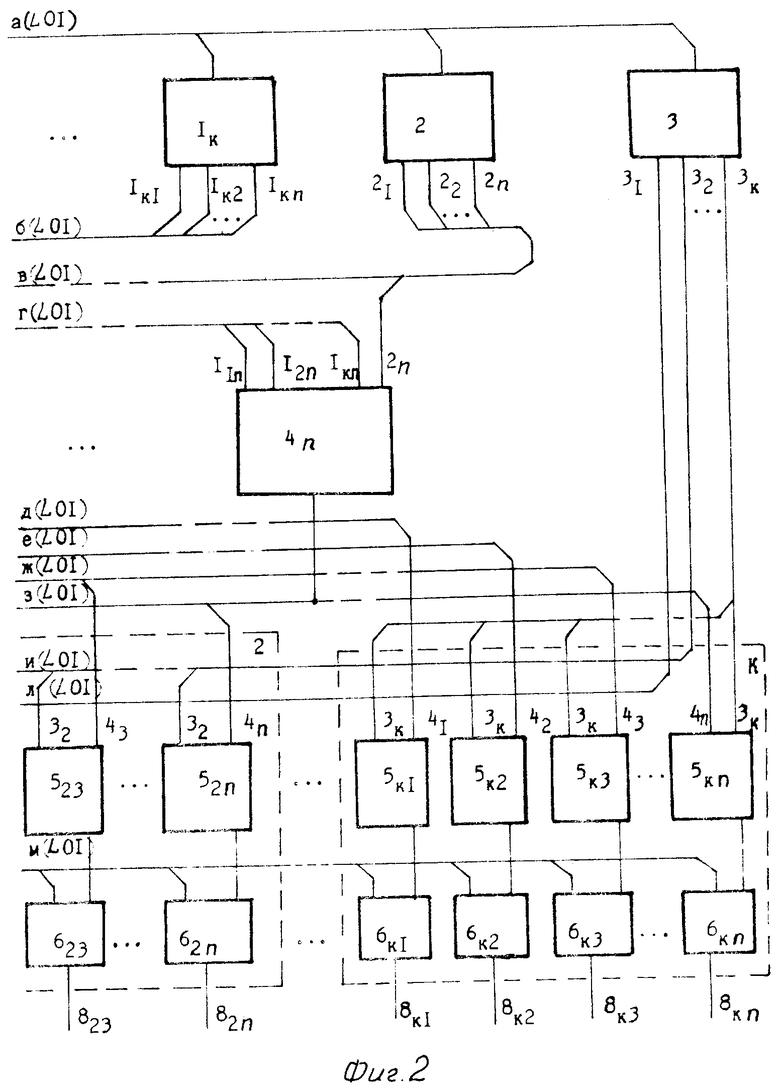

На фиг. 1 и 2 представлена блок-схема предложенного запоминающего устройства.

Запоминающее устройство содержит основной накопитель, состоящий из К n-разрядных информационных блоков 1 памяти, одного n-разрядного блока 2 памяти контрольных разрядов, К-разрядного дополнительного накопителя 3, n блоков 4 контроля, К групп элементов И 5 по n элементов в каждой группе, К групп элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6 по n элементов в каждой группе, причем адресные входы основного и дополнительного накопителей соединены с адресной шиной 7. Выходы 8 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 6 являются выходами устройства, первый вход i-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 (i = 1, . . . , n) k-й группы (k = 1, . . . , K) соединен с i-м выходом блока 2 основного накопителя, второй вход i-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 k-й группы соединен с выходом i-го элемента И 5 k-й группы, первый вход всех элементов И 5 k-й группы соединен с k-м выходом дополнительного накопителя 3, второй вход i-го элемента И 5 каждой группы соединен с выходом i-го блока 4 контроля, k-й вход i-го блока 4 контроля соединен с i-м выходом k-го блока 1 памяти основного накопителя, (К+1)-й выход i-го блока 4 контроля соединен с i-м выходом блока 2 памяти контрольных разрядов основного накопителя. При этом основной накопитель построен из m рядов n-разрядных интегральных схем памяти емкостью n˙ R бит по К+1 схем в каждом ряду для хранения [(K+1) ˙n] -разрядных слов с учетом контрольных разрядов. Каждый блок 1 основного накопителя содержит m интегральных схем памяти и имеет емкость (m ˙n ˙R) бит. Блок 2 контрольных разрядов содержит n-разрядную информацию, i-й разряд которой является контрольным для кода соответственно из i-х разрядов информации блоков 1 основного накопителя и сформирован каким-либо известным способом, например является суммой по модулю два одноименных разрядов информации блоков 1.

Каждому блоку 1 основного накопителя в дополнительном накопителе соответствует m бит информации, т. е. каждой интегральной схеме памяти блоков 1 основного накопителя соответствует один бит информации, единицей кодируется неисправность схемы, нулем - исправность. Неисправность может приводить к искажению части или всей информации, хранящейся в интегральной схеме памяти, ошибки корректируются при наличии ошибочной информации на выходах одного блока основного накопителя, т. е. при наличии в каждом ряду не более одной неисправной интегральной схемы памяти.

Запоминающее устройство работает следующим образом.

По шине 7 адреса из процессора (не показан) на адресные входы накопителей поступает адрес считываемого слова. Считанное слово с контрольными разрядами поступает в блок 4 контроля, в котором получается контрольная информация, она сравнивается с информацией с блока 2 контрольных разрядов. Если в считанной информации нет искажений, то выходы блоков 4 контроля нулевые. В случае искажения информации выходы соответствующих искаженным разрядам блоков 4 контроля будут единичными.

Количество элементов И 5 и ИСКЛЮЧАЮЩЕЕ ИЛИ 6 равно количеству разрядов считываемой информации без учета контрольных разрядов. Каждому разряду выходной информации соответствуют один элемент И 5 и один элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 6. Сигналы с выходов блоков 4 контроля поступают на элементы И 5, соответствующие разрядам информации, по которым получен сигнал. На вторые входы k-й группы элементов И 5 поступает информация k-го разряда дополнительного накопителя 3 о состоянии исправности единичного сигнала с блока 4 контроля и единичного сигнала с выхода дополнительного накопителя 3. На выходе элемента И появляется единичный сигнал, при наличии которого происходит инвертирование элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 6 соответствующего разряда считанной информации.

Использование предлагаемого устройства более эффективно, чем известного устройства для коррекции ошибок считанной информации. В нем может быть скорректировано от одного до n разрядов считанного слова, если искаженные разряды считаны с одного блока основной памяти. Для коррекции ошибок требуется меньший объем дополнительной памяти, чем в известном устройстве. В предлагаемом устройстве в отличие от известного не происходит существенного увеличения времени обращения. (56) Авторское свидетельство СССР N 1005193, кл. G 11 C 29/00, 1981.

Авторское свидетельство СССР N 686085, кл. G 11 C 29/00, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ МАГИСТРАЛЕЙ | 1990 |

|

RU2017210C1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| СИСТЕМА КОММУТАЦИИ ВЫЧИСЛИТЕЛЬНЫХ УСТРОЙСТВ | 1991 |

|

RU2006928C1 |

| ПРЕОБРАЗОВАТЕЛЬ КОД-НАПРЯЖЕНИЕ | 1991 |

|

RU2013001C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1991 |

|

RU2025772C1 |

| Устройство для записи и воспроизведения цифровой информации | 1990 |

|

SU1742856A1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 1990 |

|

RU2040040C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения надежных запоминающих устройств, оперативной или постоянной памяти произвольного доступа, работающих в реальном масштабе времени. Целью изобретения является повышение надежности, быстродействия и упрощение устройства. Цель достигается тем, что в устройство, содержащее основной накопитель, состоящий из информационных блоков памяти и блока памяти контрольных разрядов, дополнительный накопитель, блоки контроля, элементы И, введены элементы ИСКЛЮЧАЮЩЕЕ ИЛИ по числу разрядов основного накопителя. 2 ил.

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК В ВЫХОДНОЙ ИНФОРМАЦИИ, содержащее основной накопитель, дополнительный накопитель, n (где n - разрядность блоков памяти основного накопителя) блоков контроля, K групп по n элементов И в каждой группе, причем адресные входы основного и дополнительного накопителей являются адресными входами устройства, отличающееся тем, что, с целью повышения надежности, быстродействия и упрощения устройства, в него введены K групп по n элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а основной накопитель состоит из K информационных блоков памяти и блока памяти контрольных разрядов, причем первый вход i-го (i= 1, . . . , n) элемента ИСКЛЮЧАЮЩЕЕ ИЛИ k-й (k = 1, . . . , K) группы соединен с i-м выходом k-го информационного блока памяти, второй вход i-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ k-й группы соединен с выходом i-го элемента И k-й группы, k-й выход дополнительного накопителя соединен с первыми входами элементов И k-й группы, второй вход i-го элемента И каждой группы соединен с выходом i-го блока контроля, k-й вход которого соединен с i-м выходом k-го информационного блока памяти, (K + 1)-й вход i-го блока контроля соединен с i-м выходом блока памяти контрольных разрядов, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходами устройства.

Авторы

Даты

1994-01-30—Публикация

1991-01-11—Подача