Изобретение относится к технике электрической связи, в частности к устройствам для фазирования синхронных цифровых потоков, и может найти применение, например, при разработке цифровых систем передачи с синхронным уплотнением цифровых потоков.

Цель изобретения - повышение точности фазирования синхронных цифровых потоков путем исключения совпадения фронтов информационных и тактовых импульсов.

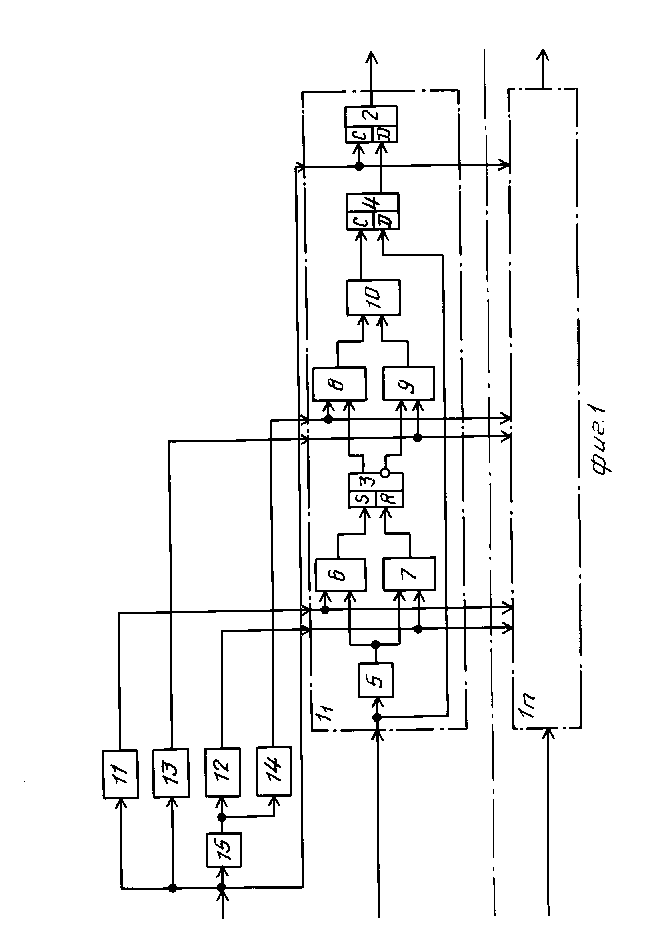

На фиг. 1 представлена структурная электрическая схема устройства для фазирования синхронных цифровых потоков; на фиг. 2 - временные диаграммы, поясняющие его работу; на фиг. 3 - вариант выполнения первого и второго формирователей зоны неопределенности стробирования (ЗНС) и первого и второго формирователей стробирующих импульсов (СИ).

Устройство для фазирования синхронных цифровых потоков содержит N цифровых каналов 11-1N, каждый из которых состоит из триггеров 2, 3, 4, формирователя импульсов 5, элементы И 6-10, а также формирователи ЗНС 11, 12, формирователи СИ 13 и 14 и элемент НЕ 15, причем формирователи ЗНС 11 и 12 и формирователи СИ 13 и 14 выполнены идентично и содержат два элемента И-НЕ 16 и 19, конденсатор 17 и диод 18.

Устройство для фазирования синхронных цифровых потоков работает следующим образом.

Последовательность тактовых импульсов (см. фиг. 2, а), синхронная с цифровыми потоками (см. фиг. 2, ж), поступающими на входы формирователей импульсов 51-5 цифровых каналов 11-1N поступает на входы формирователя ЗНС 11, формирователя СИ 13 и элемента НЕ 15. Инверсная последовательность тактовых импульсов с выхода элемента НЕ 15 (см. фиг. 2, б) подается на входы формирователя ЗНС 12 и формирователя СИ 14. На выходах формирователей ЗНС 11 и 12 формируются отрицательные импульсы (см. фиг. 2 в, г) определяющие зону неопределенности стробирования, а именно при попадании переднего фронта импульса цифрового потока (см. фиг. 2, ж) в зону неопределенности (см. фиг. 2, в, г) происходит переключение стробирующей последовательности (см. фиг. 2, д, е) на входе триггера 4, за счет этого исключается совпадение фронтов цифрового потока и последовательности тактовых импульсов.

Цифровой поток (см. фиг. 2, ж) поступает на вход формирователя импульсов 5, на выходе которого формируются узкие импульсы (см. фиг. 2, з), совпадающие с передними фронтами импульсов цифрового потока. В случае совпадения этого импульса (см. фиг. 2, з) с импульсом с выхода формирователя ЗНС 11 или 12 на выходе соответствующего элемента совпадения 6 или 7 формируется узкий импульс, устанавливающий триггер 3 в единичное состояние (см. фиг. 2, и) 1 или в нулевое состояние.

Прямой и инверсный выходы триггера 3 подключены к первым входам элементов совпадения 8 и 9 и сигналы на выходах триггера 3 являются разрешающими (запрещающими) прохождение соответствующей стробирующей последовательности через элемент совпадения 10 на тактовый вход триггера 4 (см. фиг. 2, к). С выхода триггера 4 сигнал (см. фиг. 2, л) подается на информационный вход триггера 2 и стробируется последовательностью тактовых импульсов, поступающей на вход устройства (см. фиг. 2, а).

Таким образом сигналы на выходах цифровых каналов 11-1N (см. фиг. 2, м) привязаны к последовательности тактовых импульсов (см. фиг. 2, а) и являются не только синхронными, но и синфазными, что облегчает их дальнейшую обработку (например, при синхронном объединении) и исключает потерю информационных и тактовых импульсов. (56) Авторское свидетельство СССР N 1608811, кл. H 04 J 3/06, 1987.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок по элементам двоичного сигнала | 1984 |

|

SU1256228A1 |

| УСТРОЙСТВО для КОНТРОЛЯ АППАРАТУРЫ ПЕРЕДАЧИДАННЫХ | 1972 |

|

SU356806A1 |

| Устройство асинхронного сопряжения дискретного сигнала с синхронным цифровым трактом | 1987 |

|

SU1610600A1 |

| Устройство для приема относительного биимпульсного сигнала | 1988 |

|

SU1614117A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ЦИФРОВЫХ ПОТОКОВ | 1992 |

|

RU2054809C1 |

| Двухканальный приемник дискретной информации | 1975 |

|

SU585615A1 |

| Многоканальный интерфейс | 1990 |

|

SU1751774A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Устройство для определения достоверности цифровой информации | 1989 |

|

SU1674211A2 |

| Устройство определения перерывов цифрового сигнала в радиоканале | 1988 |

|

SU1538262A1 |

Использование: в технике электрической связи при фазировании синхронных цифровых потоков. Сущность изобретения: устройство для фазирования синхронных цифровых потоков содержит N цифровых каналов 11-1N, каждый из которых состоит из триггеров 2, 3, 4, формирователь импульсов 5 и элементов совпадения 6 - 10, а также формирователь зоны неопределенности стробирования 11, 12 и формирователей стробирующих импульсов 13, 14, и элемент НЕ 15. Цель изобретения - повышение точности фазирования синхронных цифровых потоков путем исключения совпадения фронтов информационных и тактовых импульсов. 3 ил.

УСТРОЙСТВО ДЛЯ ФАЗИРОВАНИЯ СИНХРОННЫХ ЦИФРОВЫХ ПОТОКОВ, содержащее N цифровых каналов, каждый из которых содержит первый триггер, тактовый вход и выход которого являются соответственно тактовым входом и выходом цифрового канала, отличающееся тем, что, с целью повышения точности фазирования синхронных цифровых потоков путем исключения совпадения фронтов информационных и тактовых импульсов, в него введены первый и второй формирователи стробирующих импульсов, первый и второй формирователи зоны неопределенности стробирования и элемент НЕ, а в каждый из N цифровых каналов введены формирователь импульсов, элементы совпадения и второй и третий триггеры, причем выход формирователя импульсов через первый и второй элементы совпадения соединены соответственно с первым и вторым входами второго триггера, прямой и инверсный выходы которого соединены соответственно через третий и четвертый элементы совпадения с входами пятого элемента совпадения, выход которого соединен с тактовым входом третьего триггера, прямой выход которого соединен с информационным входом первого триггера, причем информационный вход третьего триггера соединен с входом формирователя импульсов и является входной шиной цифрового потока, вторые входы первого - четвертого элементов совпадения являются первым - четвертым входами каждого цифрового канала, при этом выходы первого и второго формирователей зоны неопределенности стробирования соединены соответственно с первым и вторым входами N цифровых каналов, а выходы первого и второго формирователей стробирующих импульсов соединены соответственно с третьим и четвертым входами N цифровых каналов, причем тактовый вход первого триггера N цифровых каналов соединен с тактовыми входами первого формирователя зоны неопределенности стробирования, первого формирователя стробирующих импульсов и с входом элемента НЕ, выход которого соединен с тактовыми входами второго формирователя зоны неопределенности стробирования и второго формирователя стробирующих импульсов.

Авторы

Даты

1994-01-30—Публикация

1990-05-24—Подача