. 1

Изобретение относится к электросвязи и может быть использовано в многоканальных системах передачи для асинхронного сопряжения дискретного сигнала с синхронным цифровым трактом, а также в системах асинхронной передач дискретной информации.

Целью изобретения является, повышение помехоустойчивости асинхронного д сопряжения.

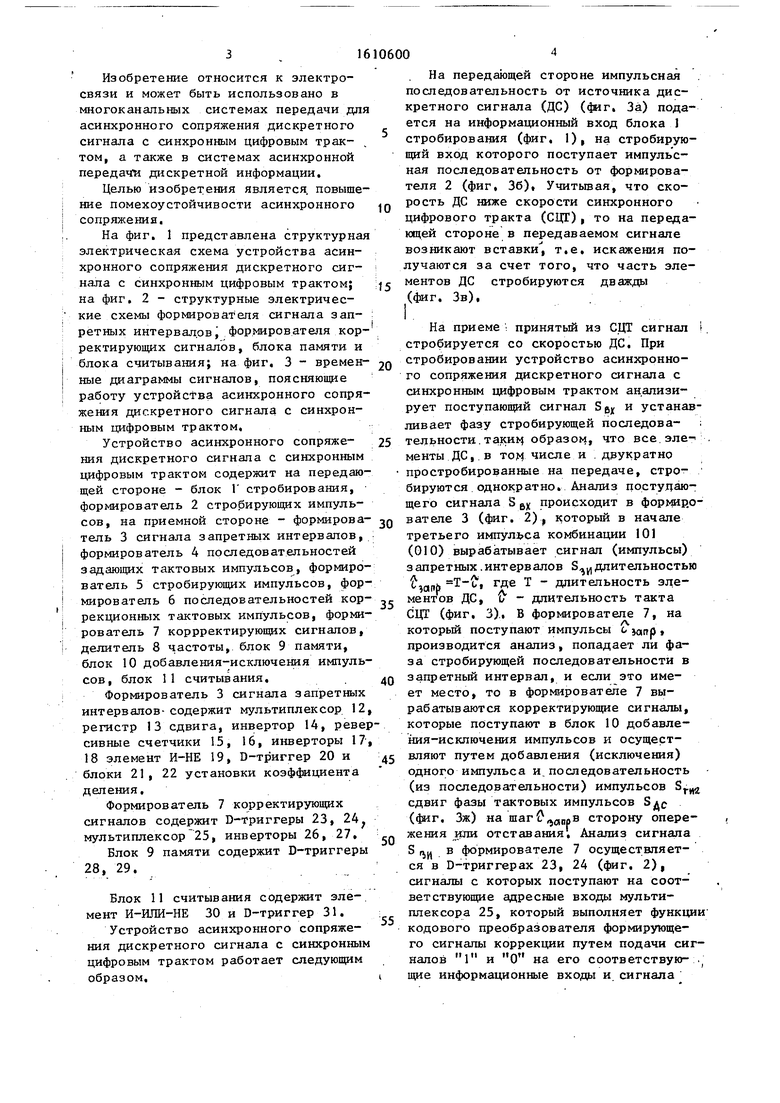

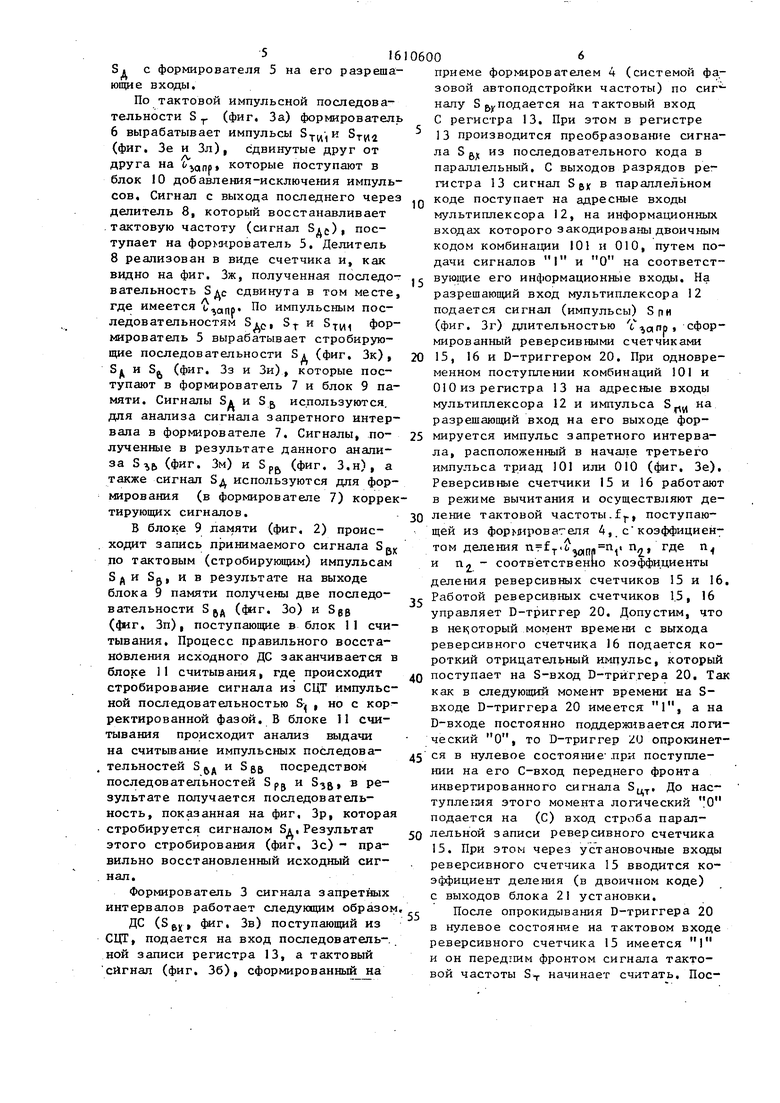

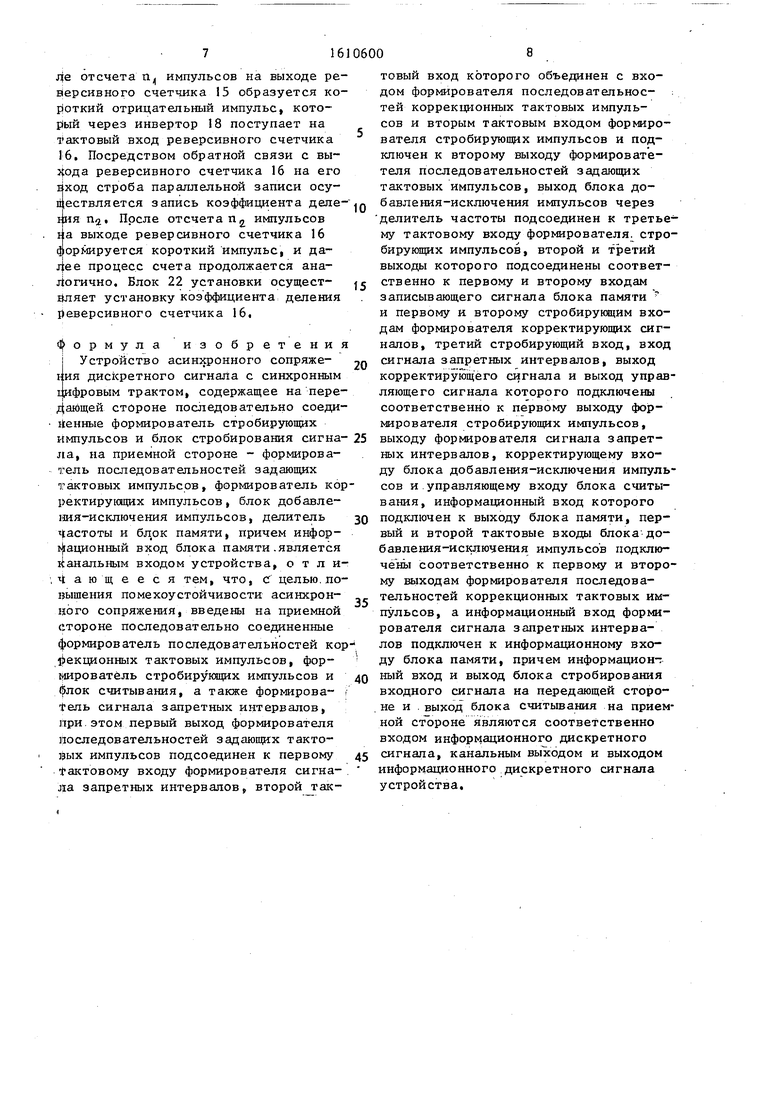

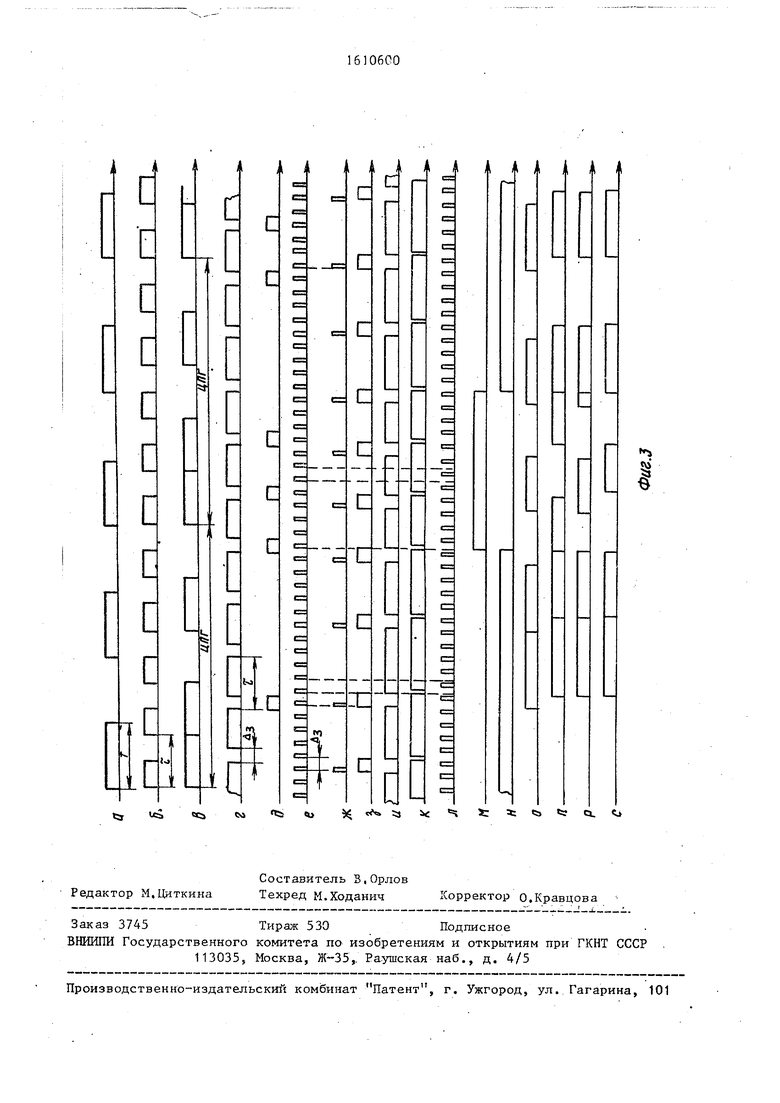

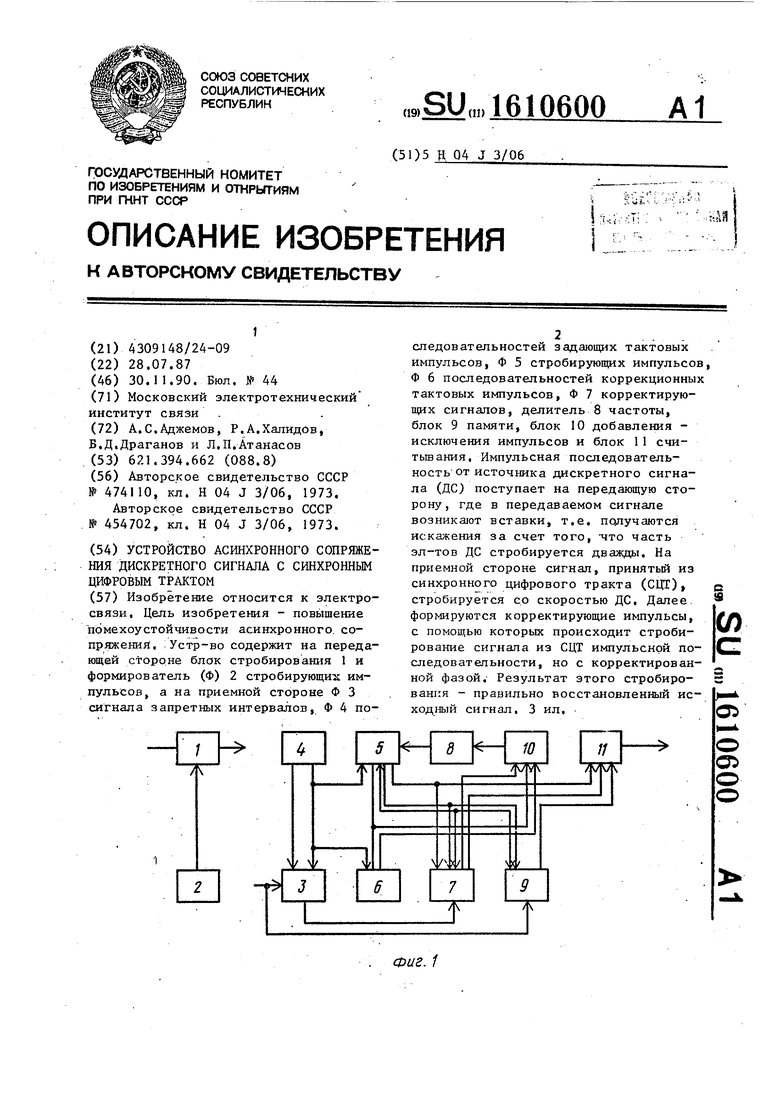

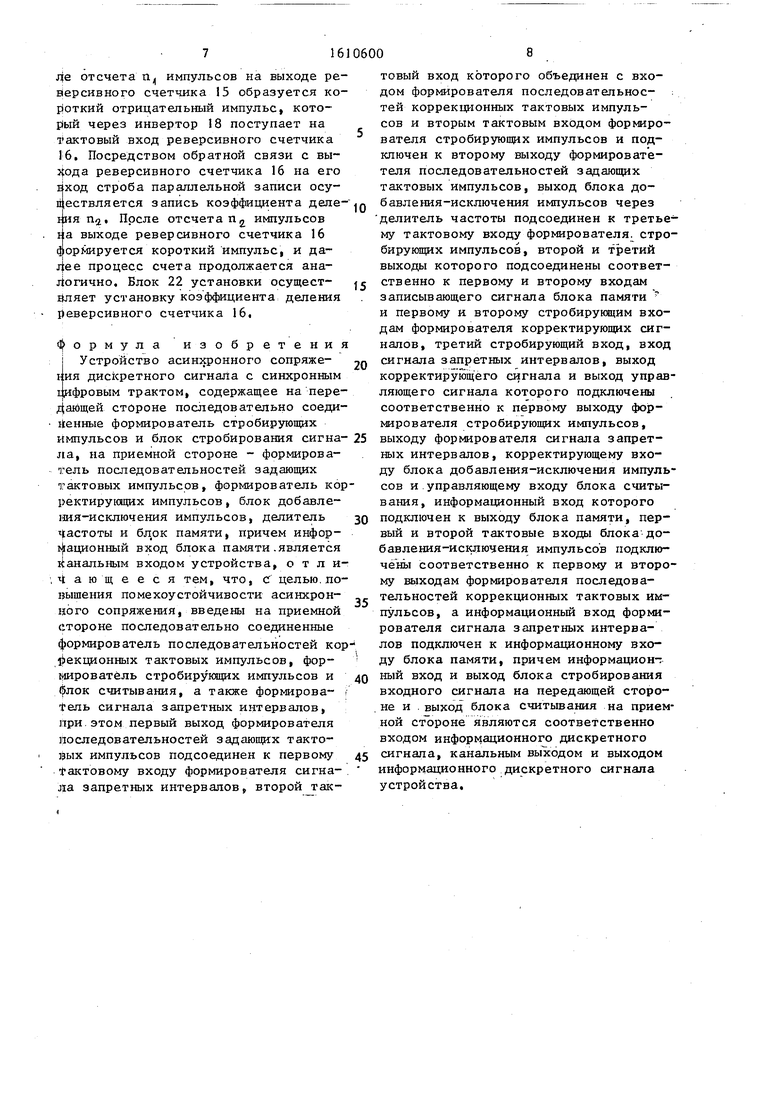

На фиг, 1 представлена структурная электрическая схема устройства асинхронного сопряжения дискретного сиг- нала с синхронным цифровым трактом; ;j5 на фиг, 2 - структурные электрические схемы формирователя сигнала зап- : ретных HHTepBanoBJ формирователя корректирующих сигналов, блока памяти и блока считывания; на фиг. 3 - времен- 2Q ные диаграммы сигналов, поясняюид е работу устройства асинхронного сопряжения дискретного сигнала с синхронным цифровым трактом.:

Устройство асинхронного сопряже- 25 кия дискретного сигнала с синхронным цифровым трактом содержит на передающей стороне - блок Г стробирования, формирователь 2 стробирующих импульсов, на приемной стороне - формирова- д тель 3 сигнала запретных интервалов, формирователь 4 последовательностей задающих тактовых импульсов, формирователь 5 стробирующих импульсов, формирователь 6 последовательностей кор- эс рекционных тактовых импульсов, формирователь 7 коррректирующих сигналов, делитель 8 частоты, блок 9 памяти, блок 10 добавления-исключения импульсов , блок 11 считыв ания..40

Формирователь 3 сигнала запретных интервалов-содержит мультиплексор 12, регистр 13 сдвига, инвертор 14, реверсивные счетчики 15, 16, инверторы 17, 18 элемент И-НЕ 19, D-триггер 20 и 45 блоки 21, 22 установки коэффициента деления.

Формирователь 7 корректирующих сигналов содержит D-триггеры 23, 24 мультиплексор 25, инверторы 26, 27, Q

Блок 9 памяти содержит D-триггеры 28, 29.

,-

Блок 11 считывания содержит элемент И-ИЛИ-НЕ 30 и D-триггер 31.

Устройство асинхронного сопряже ния дискретного сигнала с синхронным цифровым трактом работает следующим образом.

д

;j5 : 2Q :

25 дэс40

45

Q

55

На передающей стороне импульсная . последовательность от источника дискретного сигнала (ДС) (фиг. За) подается на информационный вход блока I стробирования (фиг. 1), на стробирую- щий вход которого поступает импульсная последовательность от формирователя 2 (фиг. 36)t Учитьгоая, что скорость ДС ниже скорости синхронного цифрового тракта (СЦГ) , то на передающей стороне в передаваемом сигнале возникают вставки, т.е. искажения получаются за счет того, что часть элементов ДС стробируются дважды (фиг. Зв),

На приеме принятый из СЦТ сигнал i стробируется со скоростью ДС. При стробировании устройство асинхронного сопряжения дискретного сигнала с синхронным цифровым трактом ан.апизи- рует поступающий сигнал Sgjf и устанавливает фазу стробирующей последова- ; тельности. та.ки1 образом, что все. эле- . менты ДС,.в том числе и двукратно простробированные на передаче, стробируются однократно. Анализ постудаю- щего сигнала S вц происходит в фориир.о- вателе 3 (фиг, 2), который в начале третьего импульса комбинации 101 (010) вырабатывает сигнал (импульсы) запретных .интервалов , длительностью , Т- о, где Т - длительность эде- ментов ДС, С - длительность такта СЦГ (фиг. 3). В формирователе 7, на который поступают импульсы о jano, производится анализ, попадает ли фаза стробирующей последовательности в запретный интервал, и если это имеет место, то в формирователе 7 вырабатываются корректирующие сигналы, которые поступают в блок 10 добавления-исключения импульсов и осуществляют путем добавления (исключения) одного импульса и,последовательность (из последовательности) импульсов S сдвиг фазы тактовых импульсов Зд (г. Зж) на сторону опережения или отставания. Анализ сигнала S п,и в формирователе 7 осуществляется в D-триггерах 23, 24 (фиг. 2), сигналы с которых поступают на соответствующие адресные входы мультиплексора 25, который выполняет функции кодового преобразователя формирующего сигналы коррекции путем подачи сигналов 1 и О на его соответствую- . щие информационные входы и сигнала

S. с формирователя 5 на его разрешающие входы.

По тактовой импульсной последовательности S (фиг. За) формирователь 6 вырабатывает импульсы STU . и S

ТИ1

ТИ2

(фиг, Зе и 3л), сдвинутые друг от друга на которые поступают в блок 10 добавления-исключения импульсов. Сигнал с выхода последнего через делитель 8, который восстанавливает .тактовую частоту (сигнал S.c), поступает на фор а-1рователь 5, Делитель 8 реализован в виде счетчика и, как видно на фиг. Зж, полученная последовательность Здс сдвинута в том месте, где имеется i/,anp« По импульсным последовательностям SACI S-r и 8ти5 формирователь 5 вырабатывает стробирую- щие последовательности 5д (фиг, Зк), БД и Sj (фиг. За и Зи), которые поступают в формирователь 7 и блок 9 памяти. Сигналы Зд и S используются.

10

приеме формирователем 4 (системой фа зовой автоподстройки частоты) по сиг налу 8,подается на тактовый вход С регистра 13, При этом в регистре 13 производится преобразование сигна ла S gj, из последовательного кода в параллельный, С выходов разрядов регистра 13 сигнал S B)f в параллельном коде поступает на адресные входы мультиплексора 12, на информационных входах которого закодированы двоичным кодом комбинации 101 и 010, путем по дачи сигналов I и О на соответст jr вующие его информационные входы. На разрешающий вход мультиплексора 12 подается сигнал (импульсы) Зпи (фиг, Зг) длительностью V-joinp , сфор мированный реверсивными счетчиками 15, 16 и D-триггером 20, При одновре менном поступлении комбинаций 101 и 010 из регистра 13 на адресные входы мультиплексора 12 и импульса S, на

20

для анализа сигнала запретного интер- разрешающий вход на его выходе форвала в формирователе 7, Сигналы, полученные в результате данного анализа , (фиг, 3м) и Spg, (фиг, 3,н), а также сигнал Зд используются для формирования (в формирователе 7) корректирующих сигналов,

В блоке 9 ламяти (фиг, 2) происходит запись принимаемого сигнала Sov

|Эл

25 мируется импульс запретного интервала, расположенный в началте третьего импульса триад 101 или 010 (фиг, Зе) Реверсивные счетчики 15 и 16 работаю в режиме вычитания и осуществляют де

30 ление тактовой частоты.f, поступающей из формирователя 4, c кoзффициeн A

том деления ..б,.п,1 п,

где п

по тактовым (стробирующим) импульсам

Зди Sg, и в результате на выходе

блока 9 памяти получены две последо-Работой реверсивных счетчиков 15, 16

и соответственно коэффициенты деления реверсивных счетчиков 15 и 1

вательности (фиг, Зо) и Spg (фиг, Зп), поступающие в блок 11 считывания. Процесс правильного восстановления исходного ДС заканчивается в блоке 11 считывания, где происходит стробирование сигнала из СЦТ импульсной последовательностью & , но с корректированной фазой, В блоке 11 считывания происходит анализ выдачи на считывание импульсных последовапосредством

S-JB в результате получается последовательность, показанная на фиг, Зр, которая стробируется сигналом Зд, Результат этого стробирования (фиг, 3с) - правильно восстановленный исходный сигнал.

Формирователь 3 сигнала запретных интервалов работает следующим образом,

ДС (3(, фиг, Зв) поступающий из СЦТ, подается на вход последовательной записи регистра 13, а тактовый сигнал (фиг, Зб), сформированный на

тельностей и Звц последовательностей Зр и

управляет D-триггер 20, Допустим, чт в нек;оторый момент времени с выхода реверсивного счетчика 16 подается ко роткий отрицательный импульс, который

ДО поступает на 3-вход D-трйггера 20, Т как в следующий момент времени на 3- входе D-триггера 20 имеется 1, а н D-входе постоянно поддерживается логи ческий О, то D-триггер 2U опрокинет

45 ся в нулевое состояние .при поступлении на его С-вход переднего фронта инвертированного сигнала 5ц-, До наступления этого момента логический О подается на (С) вход строба парал50 лельной записи реверсивного счетчика 15, При этом через установочные входы реверсивного счетчика 15 вводится коэффициент деления (в двоичном коде) с выходов блока 21 установки,

55После опрокидывания D-триггера 20

в нулевое состояние на тактовом входе реверсивного счетчика 15 имеется I и он передгшм фронтом сигнала тактовой частоты 3т начинает считать, Пос1610600

10

приеме формирователем 4 (системой фазовой автоподстройки частоты) по налу 8,подается на тактовый вход С регистра 13, При этом в регистре 13 производится преобразование сигнала S gj, из последовательного кода в параллельный, С выходов разрядов регистра 13 сигнал S B)f в параллельном коде поступает на адресные входы мультиплексора 12, на информационных входах которого закодированы двоичным кодом комбинации 101 и 010, путем подачи сигналов I и О на соответст- jr вующие его информационные входы. На разрешающий вход мультиплексора 12 подается сигнал (импульсы) Зпи (фиг, Зг) длительностью V-joinp , сформированный реверсивными счетчиками 15, 16 и D-триггером 20, При одновременном поступлении комбинаций 101 и 010 из регистра 13 на адресные входы мультиплексора 12 и импульса S, на

20

разрешающий вход на его выходе фор25 мируется импульс запретного интервала, расположенный в началте третьего импульса триад 101 или 010 (фиг, Зе), Реверсивные счетчики 15 и 16 работают в режиме вычитания и осуществляют де30 ление тактовой частоты.f, поступающей из формирователя 4, c кoзффициeн- A

том деления ..б,.п,1 п,

где п

Работой реверсивных счетчиков 15, 16

и соответственно коэффициенты деления реверсивных счетчиков 15 и 16,

управляет D-триггер 20, Допустим, что в нек;оторый момент времени с выхода реверсивного счетчика 16 подается короткий отрицательный импульс, который

ДО поступает на 3-вход D-трйггера 20, Так как в следующий момент времени на 3- входе D-триггера 20 имеется 1, а на D-входе постоянно поддерживается логический О, то D-триггер 2U опрокинет45 ся в нулевое состояние .при поступлении на его С-вход переднего фронта инвертированного сигнала 5ц-, До наступления этого момента логический О подается на (С) вход строба парал50 лельной записи реверсивного счетчика 15, При этом через установочные входы реверсивного счетчика 15 вводится коэффициент деления (в двоичном коде) с выходов блока 21 установки,

55После опрокидывания D-триггера 20

в нулевое состояние на тактовом входе реверсивного счетчика 15 имеется I и он передгшм фронтом сигнала тактовой частоты 3т начинает считать, Посде отсчета п, импульсов на выходе реверсивного счетчика 15 образуется короткий отрицательный импульс, который через инвертор 18 поступает на тактовый вход реверсивного счетчика 16, Посредством обратной связи с вы- з|ода реверсивного счетчика 16 на его аход строба параллельной записи осу- П1ествляется запись коэффициента делеьия . После отсчета п импульсов t:a выходе реверсивного счетчика 16 форшруется короткий импульс, и да- jrtee процесс счета продолжается ана- 14огично, Блок 22 установки осущест- аляет установку коэффициента деления реверсивного счетчика 16,

формула изобретения Устройство асинхронного сопряже- ;ия дис1фетного сигнала с синхронным г 1фровым трактом, содержащее на пере- Дающей стороне последовательно соеди- йенные формирователь стробирующих импульсов и блок стробирования сигна- ла, на приемной стороне - формирователь последовательностей задающих тактовых импульсов, формирователь корректирующих импульсов, блок добавления-исключения импульсов, делитель частоты и бл,ок памяти, причем инфор- 1 ационный вход блока памяти .является банальным входом устройства, отливающееся тем, что, с целью.повышения помехоустойчивости асинхронного сопряжения, введены на приемной стороне последовательно соединенные формирователь последовательностей кор 1|)екционных тактовых импульсов, фор- мироватёль стробирукяцих импульсов и флок считывания, а также формирова- Фель сигнала запретных интервалов, при.этом первый выход формирователя последовательностей задающих тактовых импульсов подсоединен к первому taKTOBOMy входу формирователя сигна- ла запретных интервалов, второй так

j

о 5 о 0 5

5

товый вход которого объединен с входом формирователя последовательное- ; тей коррекционных тактовых импульсов и вторым тактовым входом формирователя стробирующих импульсов и подключен к второму выходу формировате- теля последовательностей задающих тактовых импульсов, выход блока добавления-исключения импульсов через

делитель частоты подсоединен к третьему тактовому входу формирователя, стробирующих импульсов, второй и третий выходы которого подсоединены соответственно к первому и второму входам записывающего сигнала блока памяти и первому и второму стробиругацим входам формирователя корректирующих сигналов, третий стробирующий вход, вход сигнала запретных интервалов, выход корректирующего сигнала и выход управляющего сигнала которого подключены соответственно к первому выходу формирователя стробирующих импульсов, выходу формирователя сигнала запретных интервалов, корректирующему входу блока добавления-исключения импульсов и.управляющему входу блока считывания, информационный вход которого подключен к выходу блока памяти, первый и второй тактовые входы блока добавления-исключения импульсов подклю- чёнь соответственно к первому и второму вь1ходам формирователя последовательностей коррекционных тактовых импульсов, а информационный вход формирователя сигнала запретных интервалов подключен к информационному входу блока памяти, причем информацион-: ный вход и выход блока стробирования входного сигнала на передающей сторо. не и .выход блока считывания на приемной стЪроне являются соответственно входом инфор рационного дискретного сигнала, канальным выходом и выходом информационного дискретного сигнала устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| Цифровой компенсатор выпадений телевизионного сигнала яркости | 1985 |

|

SU1269274A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Кодер кода 3В2 @ | 1984 |

|

SU1244803A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для управления @ -фазным шаговым двигателем | 1987 |

|

SU1473066A1 |

| Цифровой измеритель ускорения вала | 1991 |

|

SU1791781A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости асинхронного сопряжения. Устройство содержит на передающей стороне блок стробирования 1 и формирователь (Ф) 2 стробирующих импульсов, а на приемной стороне Ф 3 сигнала запретных интервалов, Ф 4 последовательностей задающих тактовых импульсов, Ф 5 стробирующих импульсов, Ф 6 последовательностей коррекционных тактовых импульсов, Ф 7 корректирующих сигналов, делитель 8 частоты, блок 9 памяти, блок 10 добавления - исключения импульсов и блок 11 считывания. Импульсная последовательность от источника дискретного сигнала (ДС) поступает на передающую сторону, где в передаваемом сигнале возникают вставки, т.е. получаются искажения за счет того, что часть эл-тов ДС стробируется дважды. На приемной стороне сигнал, принятый из синхронного цифрового тракта (СЦТ), стробируется со скоростью ДС. Далее формируются корректирующие импульсы, с помощью которых происходит стробирование сигнала из СЦТ импульсной последовательностью, но с корректированной фазой. Результат этого стробирования - правильно восстановленный исходный сигнал. 3 ил.

| Устройство для асинхронного ввода двоичной информации со стаффингом в цифровой канал | 1974 |

|

SU474110A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для асинхронного сопряжения в синхронном канале связи | 1972 |

|

SU454702A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-11-30—Публикация

1987-07-28—Подача