ел

00 00

to

О

to

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство тактовой синхронизации регенератора | 1985 |

|

SU1283992A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ ПЕРЕРЫВОВ ЦИФРОВОГО СИГНАЛА В РАДИОКАНАЛЕ | 1973 |

|

SU390676A1 |

| Устройство автоматической подстройки частоты | 1989 |

|

SU1698987A1 |

| Регенератор двоичных сигналов | 1984 |

|

SU1185630A1 |

| Устройство для контроля искажений дискретных сигналов в радиоканалах | 1989 |

|

SU1578822A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости. Устройство определения перерывов цифрового сигнала в радиоканале содержит выделитель 1 фронтов, блок фазирования 2, формирователи 3 и 4 импульсов, соответствующих центру посылки, а также началу и концу посылки, эл-ты И 5 и 6, блок задержки 7 и интегратор 8. Для повышения помехоустойчивости в устройство введены вычитающий счетчик 9 дешифраторы 10 и 11, блоки задержки 12 и 13, эл-т ИЛИ 14 и RS - триггер 15. 1 з.п.ф-лы, 2 ил.

фие.1

Изобретение относится к области Электросвязи и может быть использовано в системах радиотелеуправления - телесигнализации, использующих режим синхронной связи с перерывами при Необходимости фиксации возникновения эвлрийных телесигналов во время перерывов связи.

Целью изобретения является повыше- |ше помехоустойчивости.

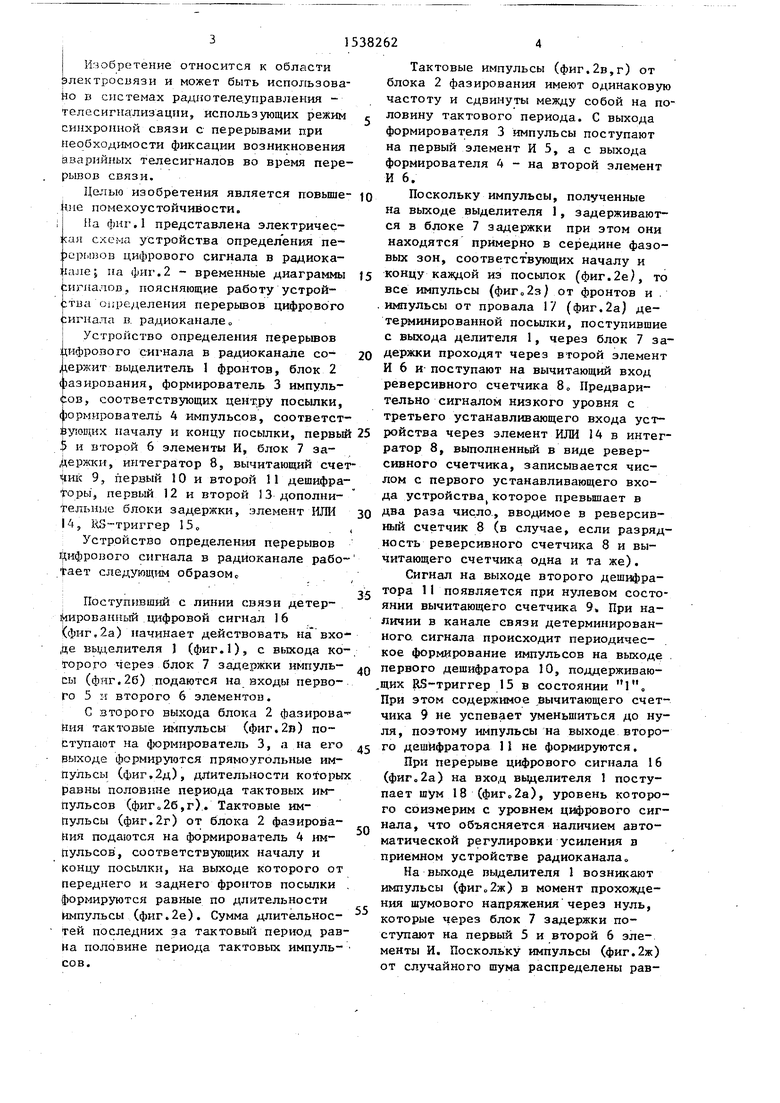

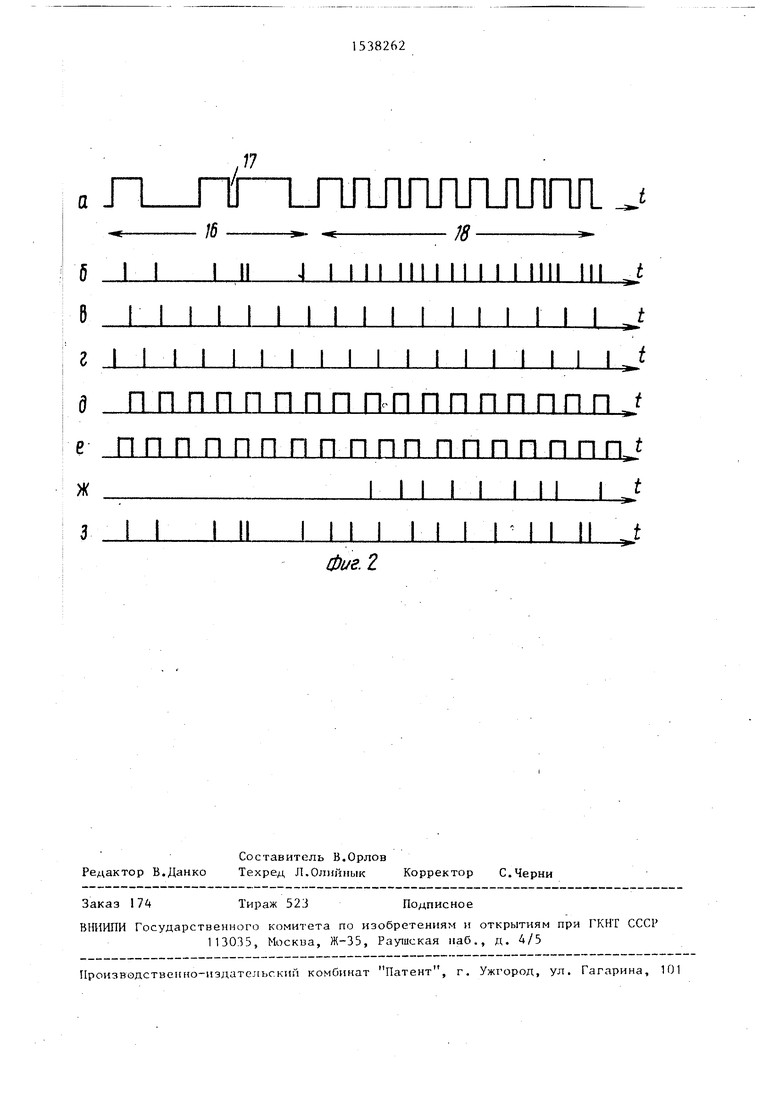

На фиг.1 представлена электрическая схема устройства определения пе- рерьшоп цифрового сигнала в радиоканале; на фиг.2 - временные диаграммы сигналов, поясняющие работу устройства определения перерывов цифрового сигнала в радиоканале,

Устройство определения перерывов цифрового сигнала в радиоканале содержит выделитель 1 фронтов, блок 2 газирования, формирователь 3 импульсов, соответствующих центру посылки, формирователь 4 импульсов, соответствующих началу и концу посылки, первый $ и второй 6 элементы И, блок 7 задержки, интегратор 8, вычитающий счет- Чик 9, первый 10 и второй 11 дешифраторы, первый 12 и второй 13 дополнительные блоки задержки, элемент ИЛИ 14, КЗ-триггер 15„,

Устройство определения перерывов Цифрового сигнала в радиоканале рабо- тает следующим образом

Поступивший с линии связи детер- ированный цифровой сигнал 16 (фиг.2а) начинает действовать на входе выделителя 1 (фиг.1), с выхода которого через блок 7 задержки импульсы (фчг,2б) подаются на входы первого 5 LI второго 6 элементов.

С второго выхода блока 2 фазирова- Ния тактовые импульсы (фиг.2в) поступают на формирователь 3, а на его Выходе формируются прямоугольные им- Пульсы (фиг,2д), длительности которых равны половине периода тактовых импульсов (фиГо2б,г). Тактовые им- Пульсы (фиг.2г) от блока 2 фазирования подаются на формирователь 4 им- пульсов, соответствующих началу и Концу посылки, на выходе которого от Переднего и заднего фронтов посылки формируются равные по длительности импульсы (фиг.2е). Сумма длительностей последних за тактовый период рав- Иа половине периода тактовых импуль- сов.

0

5

0

5

0

5

0

5

0

5

Тактовые импульсы (фиг.2в,г) от блока 2 фазирования имеют одинаковую частоту и сдвинуты между собой на половину тактового периода. С выхода формирователя 3 импульсы поступают на первый элемент И 5, а с выхода формирователя 4 - на второй элемент И 6.

Поскольку импульсы, полученные на выходе выделителя 1, задерживаются в блоке 7 задержки при этом они находятся примерно в середине фазовых зон, соответствующих началу и концу каждой из посыпок (фиг.2е), то все импульсы (фиг02з) от фронтов и .импульсы от провала 17 (фиг.2а) детерминированной посыпки, поступившие с выхода делителя 1, через блок 7 задержки проходят через второй элемент И 6 и поступают на вычитающий вход реверсивного счетчика 80 Предварительно сигналом низкого уровня с третьего устанавливающего входа устройства через элемент ИЛИ 14 в интегратор 8, выполненный в виде реверсивного счетчика, записывается числом с первого устанавливающего входа устройства(которое превышает в два раза число, вводимое в реверсивный счетчик 8 (в случае, если разрядность реверсивного счетчика 8 и вычитающего счетчика одна и та же).

Сигнал на выходе второго дешифратора 11 появляется при нулевом состоянии вычитающего счетчика 9, При наличии в канале связи детерминированного сигнала происходит периодическое формирование импульсов на выходе первого дешифратора 10, поддерживающих RS-триггер 15 в состоянии При этом содержимое вычитающего счетчика 9 не успевает уменьшиться до нуля, поэтому импульсы на выходе второго дешифратора 11 не формируются.

При перерыве цифрового сигнала 16 () на вход выделителя 1 поступает шум 18 (), уровень которого соизмерим с уровнем цифрового сигнала, что объясняется наличием автоматической регулировки усиления я приемном устройстве радиоканала,

На выходе выделителя 1 возникают импульсы (фиг„2ж) в момент прохождения шумового напряжения через нуль, которые через блок 7 задержки поступают на первый 5 и второй 6 элементы И. Поскольку импульсы (фиг.2ж) от случайного шума распределены рав5

номерно в интервале всей длительности посылки, а длительность центральных импульсов (фиг.2д) равны сумме длительностей импульсов начала и конца посылки (фиг.2е), то появление импульсов (фиг.2ж,з) с выходов пер- фого 5 и второго 6 элементов И равновероятно

Фазовое смещение выходных сигналов первого 5 и второго 6 элементов, соответствующих временному расположению центральной части и боковым частям элементарной посылки, интегрируется реверсивным счетчиком 8. При этом импульсы (фиг.2ж,з) из-за различного управляющего воздействия их на реверсивный счетчик 8 практически не изменяют содержимого последнего, так как после поступления импульса на суммирующий вход реверсивного счетчика 8 с большой вероятностью поступает импульс на его вычитающий вход Таким образом, импульсы на выходе первого дешифратора 10 не формируются, а следовательно, через интервалы .времени, определяемые коэффициентом деления вычитающего счетчика 9, появляются импульсы на выходе второго дешифратора 11, осуществляющие установку в нуль RS-триггера 15.

Первый 12 и второй 13 дополнительный блоки задержки предназначены для предотвращения формирования ложных выходных сигналов на выходе первого дешифратора 10 при переключении реверсивного счетчика 8 и увеличения длительности выходного импульса первого дешифратора 10„ Формула изобретения

382626

выделителя фронтов, причем вход вы- делителя фронтов является входом устройства, отличающееся тем, что, с целью повышения помехоустойчивости, введены последовательно соединенные первый дополнительный блок задержки, первый дешифратор, второй дополнительный блок задержки,

10 элемент ИЛИ, вычитающий счетчик, второй дешифратор и R+S-триггер, при этом выходы первого и второго элементов И, элемента ИЛИ и блока задержки подсоединены соответственно к

15 первому, второму и третьему управляющим входам интегратора и входу первого дополнительного блока задержки, дополнительный вход формировате. ля импульсов, соответствующих цент20 РУ посылки, и тактовый вход вычитающего счетчика подключены к первому выходу блока фазирования, второй выход которого подсоединен к дополнительному входу формирователя им-(

25 пульсов, соответствующих началу и концу посылки, и стробирующему входу второго дешифратора, выход интегратора подсоединен к информационному входу первого дешифратора, выход

30 которого подсоединен к S-входу RS- триггера, причем установочные входы интегратора и вычитающего счетчика, второй вход элемента ИЛИ и прямой выход RS-триггера являются соответст35 венно первым, вторым и третьим устанавливающими входами и выходом устройства.

40 ватель импульсов, соответствующих центру посылки, и формирователь импульсов, соответствующих началу и концу посыпку выполнены в виде RS- триггеров, причем S- и R-входы и

45 прямой выход RS-триггеров являются соответственно входом, дополнительным входом и выходом формирователя импульсов, соответствующих центру посылки, и формирователя импульсов,

0 соответствующих началу и концу посылки, а интегратор выполнен в виде реверсивного счетчика, устанавливающий вход, вход сложения, вход вычитания, вход разрешения записи и

5 выходы разрядов которого являются со ответственно устанавливающим входом, первым, вторым и третьим управляющими входами и выходом интегратора.

Фиг. 2

| Шляпоберский В.И | |||

| Основы техники передачи дискретных сообщений | |||

| М.: Связь, 1973, с.287-289 | |||

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ ПЕРЕРЫВОВ ЦИФРОВОГО СИГНАЛА В РАДИОКАНАЛЕ | 0 |

|

SU390676A1 |

Авторы

Даты

1990-01-23—Публикация

1988-03-28—Подача