Изобретение относится к автоматике и вычислительной технике и предназначено для использования в цифровых системах обмена массивами данных между устройствами.

Известен преобразователь последовательного кода в параллельный, содержащий блок приемных регистров, распределитель импульсов, группу элементов И, триггер записи, триггер подготовки, элемент ИЛИ, элемент НЕ и четыре элемента И.

Недостатки данного преобразователя заключаются в сравнительно большом объеме оборудования и ограниченной области применения. Объем оборудования обусловлен необходимостью иметь для обработки и хранения информации элементы с разрядностью, равной разрядности принимаемых слов. Ограничение области применения прежде всего связано с невозможностью хранения всего массива принимаемой информации в буферном устройстве, что вынуждает считывать каждое информационное слово массива за время приема следующего слова.

Наиболее близким по технической сущности к заявляемому устройству является выбранный в качестве прототипа преобразователь последовательного кода в параллельный, содержащий входной регистр, распределитель импульсов, блок памяти, счетчик по модулю m, счетчик по модулю n, триггер, выходной регистр, два элемента задержки, три элемента И-ИЛИ и два элемента И.

Недостатками данного устройства являются невозможность контроля правильности записи информации в блок памяти в связи с разделением во времени приема информации в блок памяти и ее считывания, сравнительно большое время подготовки к чтению информационного слова n циклов работы распределителя импульсов), а также ограниченные возможности, связанные со строго определенным размером массива принимаемой информации и разрядностью слов и необходимостью постоянно находиться в режиме готовности приема информации устройству, принимающему на обработку преобразованную информацию, что неприемлимо при работе в реальном масштабе времени.

Цель изобретения - повышение точности и быстродействия преобразователя, а также расширение области его применения.

Цель достигается тем, что в преобразователь последовательного кода в параллельный, содержащий распределитель импульсов, вход которого является входом синхронизации преобразователя, первый выход распределителя импульсов соединен с первым входом входного регистра, второй вход которого является информационным входом преобразователя, выходной регистр, первый счетчик, выходы которого соединены с первыми входами блока памяти, а первый вход счетчика является управляющим входом преобразователя, триггер, первый и второй элементы И дополнительно введены формирователь серии импульсов, второй и третий счетчики, блок контроля записи информации, блок выходных ключей, формирователь импульсов, блок кода начального состояния, блок формирования сигнала готовности, элементы ИЛИ, третий и четвертый элементы И, выход первого элемента ИЛИ соединен с первым входом формирователя серии импульсов, второй выход распределителя импульсов соединен с первыми входами первого и четвертого элементов И и вторым входом формирователя серии импульсов, первый выход которого соединен с первым входом второго элемента ИЛИ и первым входом выходного регистра, второй выход соединен с первым входом третьего элемента ИЛИ, третий и четвертый выходы распределителя импульсов соединены с первыми входами соответственно второго и третьего элементов И, пятый выход распределителя импульсов соединен с первыми входами второго счетчика и триггера, второй вход и выход которого подключены соответственно к первому выходу распределителя импульсов и второму входу третьего элемента ИЛИ, выход которого соединен со вторым входом блока памяти, выходы которого соединены с первыми входами блока контроля записи информации и вторыми входами выходного регистра, выходы которого соединены с первыми входами блока выходных ключей, выходы которого являются информационными выходами преобразователя, первый выход второго счетчика соединен со вторым входом второго элемента ИЛИ, второй выход второго счетчика соединен со вторыми входами первого и четвертого элементов И, выход первого элемента И соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом формирователя импульсов, а выход соединен с третьим входом входного регистра, выходы которого соединены с третьими входами блока памяти и вторыми входами блока контроля записи информации, третий выход второго счетчика соединен со вторыми входами второго и третьего элементов И, выходы которых соединены соответственно с четвертым входом блока памяти и третьим входом блока контроля записи информации, выход которого является выходом сигнала ненормы преобразователя, выход второго элемента ИЛИ соединен с первым входом третьего счетчика, первые выходы которого соединены с объединенными пятыми входами блока памяти и третьими входами выходного регистра, второй выход третьего счетчика соединен с третьим входом четвертого элемента И, выход которого соединен с объединенными вторыми входами второго и третьего счетчиков, третьи входы которых соединены соответственно с первыми и вторыми выходами блока кода начального состояния, при этом третий выход третьего счетчика соединен с объединенными третьим входом формирователя серии импульсов и вторым входом первого счетчика, выходы которого соединены с входами блока формирования сигнала готовности, выход которого является выходом сигнала готовности преобразователя, объединенные первый вход первого элемента ИЛИ и второй вход блока выходных ключей являются входом считывания преобразователя, второй вход первого элемента ИЛИ и третий вход первого счетчика объединены и являются входом записи преобразователя, четвертые входы первого счетчика являются адресными входами преобразователя, четвертый вход формирователя серии импульсов, вход формирователя импульсов, четвертые входы второго и третьего счетчиков объединены и соединены с управляющим входом преобразователя.

Введение элементов ИЛИ, третьего и четвертого элементов И, второго и третьего счетчиков, формирователя серии импульсов, формирователя импульсов, блока кода начального состояния, блока формирования сигнала готовности, блока контроля записи информации и блока выходных ключей, позволяет повысить точность и быстродействие преобразователя и расширить область его применения.

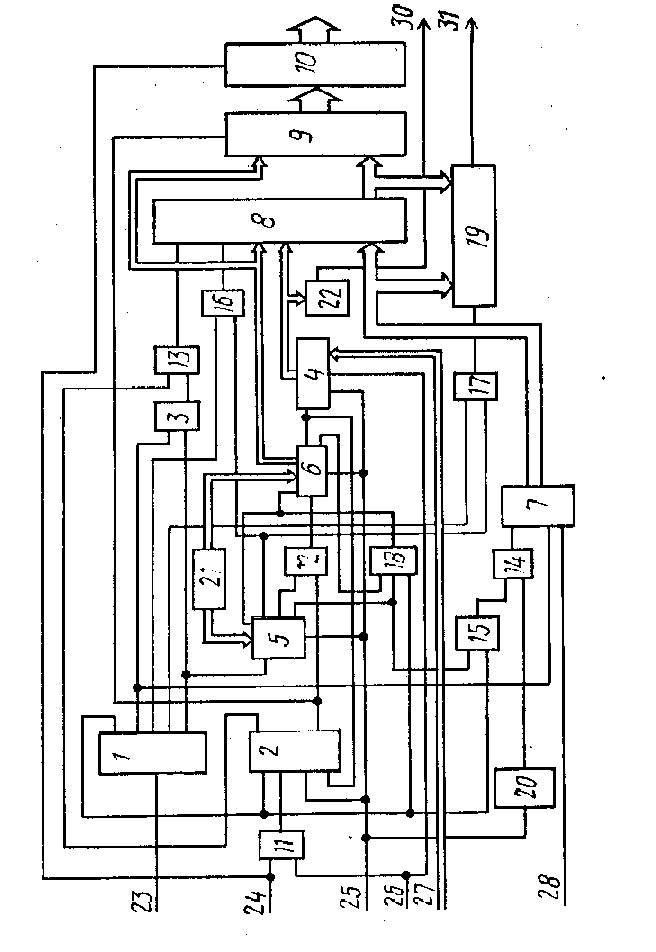

На чертеже представлена структурная схема преобразователя.

Преобразователь содержит распределитель 1 импульсов, формирователь 2 серии импульсов, триггер 3, первый, второй и третий счетчики 4-6, входной регистр 7, блок 8 памяти, выходной регистр 9, блок выходных ключей 10, элементы ИЛИ 11-14, элементы И 15-18, блок 19 контроля записи информации, формирователь 20 импульсов, блок 21 кода начального состояния, блок 22 формирования сигнала готовности, вход 23 синхронизации преобразователя, вход 24 считывания, управляющий вход 25, вход 26 записи, адресные входы 27, информационный вход 28, информационные выходы 29, выход 30 сигнала готовности и выход 31 сигнала ненормы преобразователя.

Преобразователь работает следующим образом.

При появлении сигнала на управляющем входе 25, указывающем на начало работы преобразователя в режиме приема, формирователь 20 импульсов вырабатывает короткий импульс, который, поступая через четвертый элемент ИЛИ 14 на третий вход входного регистра 7, устанавливает его в исходное состояние. При появлении сигнала на управляющем входе 25 устанавливаются в ненулевое положение также первый, второй и третий счетчики 4-6, а работа формирователя 2 серии импульсов запрещается. Емкости первого, второго и третьего счетчиков 4-6 равны соответственно m, k и n/k, при этом k - число третьих входов блока 8 памяти и разрядность входного регистра 7.

Распределитель 1 импульсов в отсутствии сигнала на входе 23 синхронизации генерирует импульсы на втором выходе. Эти импульсы поступают на второй вход формирователя 2 серии импульсов, а также на первые входы первого и четвертого элементов И 15 и 18.

Так как с выходов второго и третьего счетчиков 5 и 6 на вторые входы первого и четвертого элементов И 15 и 18 и третьего входа четвертого элемента И 18 поступают разрешающие сигналы нулевого состояния, то импульсы со второго выхода распределителя 1 импульсов попадут на третий вход входного регистра 7 и подтвердят его исходное состояние, а также запишут во второй и третий счетчики 5 и 6 коды, соответствующие хранящимся в блоке 21 кода начального состояния, при этом во второй счетчик 5 записывается остаток от деления числа (n - N) на число k (т. е. (n - N) - [n - N)/k] ˙ k), где N - количество разрядов в принимаемом слове в пределах от 1 до n, а в третий счетчик 6 записывается результат целочисленного деления [(n - N)/k] .

Поступление на информационный вход 28 преобразователя каждого бита информации сопровождается сигналом на входе 23 синхронизации преобразователя, по которому распределитель 1 импульсов прекращает генератор импульсы на своем втором выходе и вырабатывает серию синхроимпульсов, первый из которых (с первого выхода распределителя 1 импульсов) осуществляет запись очередного информационного разряда во входной регистр 7 и устанавливает триггер 3, сигнал с которого, поступая на блок 8 памяти через третий элемент ИЛИ 13, позволяет считывать информацию на выходе блока 8 памяти.

По следующему синхроимпульсу с третьего выхода распределителя 1 импульсов, поступающему на второй элемент И 16, в случае, если второй счетчик 5 заполнен полностью, осуществляется запись в блок 8 памяти k бит информации с выходов входного регистра 7. В противном случае синхроимпульс не изменяет состояние блока 8 памяти.

По синхросигналу с четвертого выхода распределителя 1 импульсов, если на третьем выходе второго счетчика 5 присутствует сигнал заполнения счетчика, осуществляется проверка правильности записи k бит информации в блок 8 памяти преобразователя, путем сравнения информации на входах и выходах блока 8 памяти. В случае несовпадения информации, вырабатывается сигнал 31 ненормы.

Последний в серии синхроимпульс с пятого выхода распределителя 1 импульсов сбрасывает триггер 3, снимая тем самым режим чтения блока 8 памяти, и по заднему фронту последнего синхроимпульса осуществляет прибавление единицы к содержимому второго счетчика 5. В случае переполнения второго счетчика 5 сигнал переноса с первого выхода, проходя через второй элемент ИЛИ 12, увеличивает также на единицу и содержимое третьего счетчика 6, (а в случае переполнения третьего счетчика 6, сигнал переноса увеличивает на единицу также и содержимое первого счетчика 4), устанавливая новый адрес обращения к блоку 8 памяти для приема новой порции информации.

После выработки серии синхроимпульсов распределитель 1 импульсов прекращает выработку импульсов на всех своих выходах до окончания сигнала синхронизации на входе 23 преобразователя. Длительность импульсов на выходах распределителя 1 импульсов определяется необходимостью завершения формирования всей совокупности операций по приему бита информации до снятия бита информации с информационного входа 28 преобразователя с одной стороны и быстродействием примененных элементов схемы с другой стороны.

По окончании сигнала синхронизации, если во втором счетчике 5 будет находиться нулевой код (счетчик сброшен), то импульсы, вырабатывающиеся на втором выходе распределителя импульсов 1, установят в исходное состояние входной регистр 7, подготавливая его к приему новой порции (k бит) информации.

Таким образом, синхронизирующие импульсы на выходах распределителя 1 импульсов обеспечивают прием каждого бита информации во входной регистр 7, перезапись информации в блок 8 памяти, проверку правильности записи информации в блок 8 памяти, а также осуществляют счет принятых битов информации и смену адреса обращения к блоку 8 памяти. Применение синхронизирующих импульсов позволяет избежать проведения операций во время переходных процессов на информационных входах преобразователя, что повышает помехоустойчивость устройства.

По окончании приема N-разрядного слова сигнал переполнения с выхода третьего счетчика 6 поступает на счетный вход первого счетчика 4, а на входы четвертого элемента И 18 поступят разрешающие сигналы нулевого состояния со второго и третьего счетчиков 5 и 6 и до приема следующего слова импульсы со второго выхода распределителя 1 импульсов запишут во второй и третий счетчики 5 и 6 указанные выше коды начального состояния, таким образом подготавливая их к приему нового N-разрядного слова. После приема M N-разрядных слов, где М - количество принимаемых слов в пределах от 1 до m, блок 22 формирования сигнала готовности вырабатывает сигнал готовности 30. Сигнал готовности 30 может быть использован для управления режимом работы преобразователя.

После окончания приема информации сигнал с управляющего входа 25 снимается и, следовательно, разрешается работа формирователя 2 серии импульсов. Когда устройство, принимающее информацию с преобразователя, примет сигнал готовности 30, оно может инициировать обмен информацией с преобразователем. Для этого необходимо подать на преобразователь сигнал 26 записи, сопровождая ее номером считываемого слова на адресных входах 27 преобразователя. После этого по команде чтения можно прочитать выбранное слово, подав команду 24 считывания.

При подаче сигнала 26 записи в первый счетчик 4 записывается номер считываемого слова (от 0 до m - 1), а по заднему фронту команды запускается формирователь 2 серии импульсов, который формирует на своем первом выходе серию импульсов, а на втором выходе потенциальный сигнал. Потенциальный сигнал обеспечивает режим чтения блока 8 памяти, а каждый импульс на первом выходе формирователя 2 серии импульсов обеспечивает запись k бит информации из блока 8 памяти в соответствующие разряды выходного регистра 9, выбор которых осуществляется по сигналам с первых выходов третьего счетчика, поступающих на третьи входы выходного регистра. По заднему фронту импульса на первом выходе формирователя 2 серии импульсов осуществляется прибавление единицы к содержимому третьего счетчика 6, устанавливая тем самым новый адрес для чтения следующих k бит информации. При переполнении третьего счетчика 6 сигнал переноса увеличивает на единицу содержимое первого счетчика 4 и сбрасывает формирователь 2 импульсов в исходное положение.

После завершения указанных операций в выходном регистре 9 будет находиться информационное слово из массива с заданным номером, а в первом счетчике 4 будет подготовлен номер следующего слова массива. Для подготовки слова к чтению требуется n/k импульсов с выхода формирователя 2 импульсов в отличие от n импульсов в прототипе.

При подаче сигнала на вход 24 считывания информации из выходного регистра 9 считывается в параллельном коде через блок выходных ключей 10, а при снятии команды 24 чтения вновь запустится формирователь 2 серии импульсов, и аналогично тому, как это происходило по сигналу 26 записи произойдет подготовка к чтению следующего информационного слова массива. Такая организация чтения позволяет читать последовательно все слова массива, не повторяя команды 26 записи.

В предлагаемом преобразователе может использоваться выходной регистр 9, не имеющий адресных входов. В этом случае соединение первых выходов третьего счетчика 6 с третьими входами выходного регистра 9 отсутствует, а запись информации в соответствующие разряды выходного регистра 9 осуществляется при помощи иного механизма выбора, например, посредством сдвига.

В случае, если есть гарантия, что входной регистр 7 будет установлен в исходное состояние импульсами со второго выхода распределителя 2 импульсов перед приемом первого бита массива информации, формирователь импульсов 20 и четвертый элемент ИЛИ 14 могут быть исключены, а выход первого элемента И 15 подключен непосредственно к третьему входу входного регистра 7.

Если в конкретном случае не требуется иметь возможность варьировать количество и разрядность слов в принимаемом массиве информации, то преобразователь может быть упрощен за счет исключения из него четвертого элемента И 18, блока 21 кода начального состояния, и блок 22 формирования сигнала готовности, при этом сигнал готовности может формироваться первым счетчиком 4, например, с помощью сигнала переноса.

Открытие для чтения блока 8 памяти во время приема информации необходимо лишь при приеме битов по счету кратных k и начало чтения блока 8 памяти может быть организовано после приема очередного бита информации во входной регистр 7, поэтому установка триггера 3 может осуществляться по сигналу с выхода второго элемента И 15.

Предлагаемый преобразователь обеспечивает осуществление контроля за правильностью записи информации в блок памяти, сокращает время подготовки информационного слова для чтения примерно в k раз по сравнению с прототипом, и расширяет область его применения за счет обеспечения функционирования в системах реального времени и преобразования массивов информации с произвольным количеством кодов произвольной разрядности. (56) Авторское свидетельство СССР N 851396, кл. G 06 F 5/04, 1979.

Авторское свидетельство СССР N 970355, кл. G 06 F 5/04, 1981.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОНТРОЛЯ ЦИФРОВЫХ СЕЙСМОРЕГИСТРИРУЮЩИХ КАНАЛОВ | 1991 |

|

RU2040019C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ В КОД | 1991 |

|

RU2007027C1 |

| Преобразователь последовательного кода в параллельный | 1990 |

|

SU1805548A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2038694C1 |

| Устройство для управления вводом изображения | 1989 |

|

SU1751738A1 |

| ИНТЕГРАТОР С БОЛЬШИМ ВРЕМЕНЕМ ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2034331C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в цифровых системах обмена массивами данных между устройствами. Цель изобретения - повышение точности и быстродействия преобразователя, а также расширение его области применения за счет возможности преобразования слов различной длины. Преобразователь содержит распределитель 1 импульсов, формирователь 2 серии импульсов, триггер 3, первый, второй и третий счетчики 4 - 6, входной регистр 7, блок 8 памяти, выходной регистр 9, блок выходных ключей 10, элементы ИЛИ 11 - 14, элементы И 15 - 18, блок 19 контроля записи информации, формирователь 20 импульсов, блок 21 кода начального состояния и блок 22 формирования сигнала готовности. 1 ил.

ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ, содержащий распределитель импульсов, вход которого является входом синхронизации преобразователя, первый выход распределителя импульсов соединен с первым входом входного регистра, второй вход которого является информационным входом преобразователя, выходной регистр, первый счетчик, выходы которого соединены с первыми входами блока памяти, а первый вход счетчика является управляющим входом преобразователя, триггер, первый и второй элементы И, отличающийся тем, что, с целью повышения точности и быстродействия преобразователя и расширения области его применения за счет возможности преобразования слов различной длины, в него введены формирователь серии импульсов, второй и третий счетчики, блок контроля записи информации, блок выходных ключей, формирователь импульсов, блок кода начального состояния, блок формирования сигнала готовности, элементы ИЛИ, третий и четвертый элементы И, выход первого элемента ИЛИ соединен с первым входом формирователя серии импульсов, второй выход распределителя импульсов соединен с первыми входами первого и четвертого элементов И и вторым входом формирователя серии импульсов, первый выход которого соединен с первым входом второго элемента ИЛИ и первым входом выходного регистра, второй выход соединен с первым входом третьего элемента ИЛИ, третий и четвертый выходы распределителя импульсов соединены с первыми входами соответственно второго и третьего элементов И, пятый выход распределителя импульсов соединен с первыми входами второго счетчика и триггера, второй вход и выход которого подключены соответственно к первому выходу распределителя импульсов и второму входу третьего элемента ИЛИ, выход которого соединен с вторым входом блока памяти, выходы которого соединены с первыми входами блока контроля записи информации и вторыми входами выходного регистра, выходы которого соединены с первыми входами блока выходных ключей, выходы которого являются информационными выходами преобразователя, первый выход второго счетчика соединен с вторым входом второго элемента ИЛИ, второй выход второго счетчика соединен с вторыми входами первого и четвертого элементов И, выход первого элемента И соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом формирователя импульсов, а выход соединен с третьим входом входного регистра, выходы которого соединены с третьими входами блока памяти и вторыми входами блока контроля записи информации, третий выход второго счетчика соединен с вторыми входами второго и третьего элементов И, выходы которых соединены соответственно с четвертым входом блока памяти и третьим входом блока контроля записи информации, выход которого является выходом сигнала ненормы преобразователя, выход второго элемента ИЛИ соединен с первым входом третьего счетчика, первые выходы которого соединены с объединенными пятыми входами блока памяти и третьими входами выходного регистра, второй выход третьего счетчика соединен с третьим входом четвертого элемента И, выход которого соединен с объединенными вторыми входами второго и третьего счетчиков, третьи входы которых соединены соответственно с первыми и вторыми выходами блока кода начального состояния, при этом третий выход третьего счетчика соединен с объединенными третьим входом формирователя серии импульсов и вторым входом первого счетчика, выходы которого соединены с входами блока формирования сигнала готовности, выход которого является выходом сигнала готовности преобразователя, объединенные первый вход первого элемента ИЛИ и второй вход блока выходных ключей являются входом считывания преобразователя, второй вход первого элемента ИЛИ и третий вход первого счетчика объединены и являются входом записи преобразователя, четвертые входы первого счетчика являются адресными входами преобразователя, четвертый вход формирователя серии импульсов, вход формирователя импульсов, четвертые входы второго и третьего счетчиков объединены и соединены с управляющим входом преобразователя.

Авторы

Даты

1994-02-15—Публикация

1990-11-21—Подача