ел

С

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ | 1990 |

|

RU2007865C1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Устройство для группового управления лифтами | 1982 |

|

SU1089024A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1988 |

|

SU1682997A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Устройство для ввода и вывода динамически изменяющейся информации | 1982 |

|

SU1115043A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

Изобретение относится к вычислительной технике и предназначено для использования в цифровых системах обмена массивами данных.

Целью изобретения является расширение области применения преобразователя за счет возможности работы преобразователя в системах реального времени и обеспечения контроля преобразуемой информации.

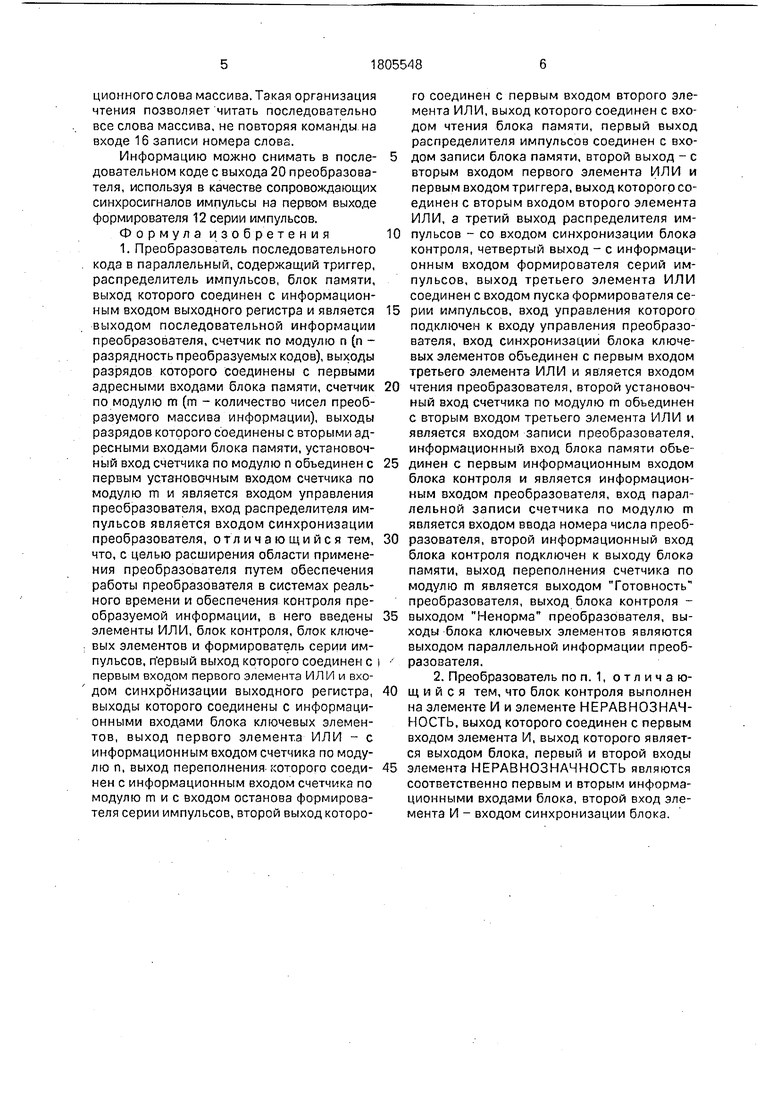

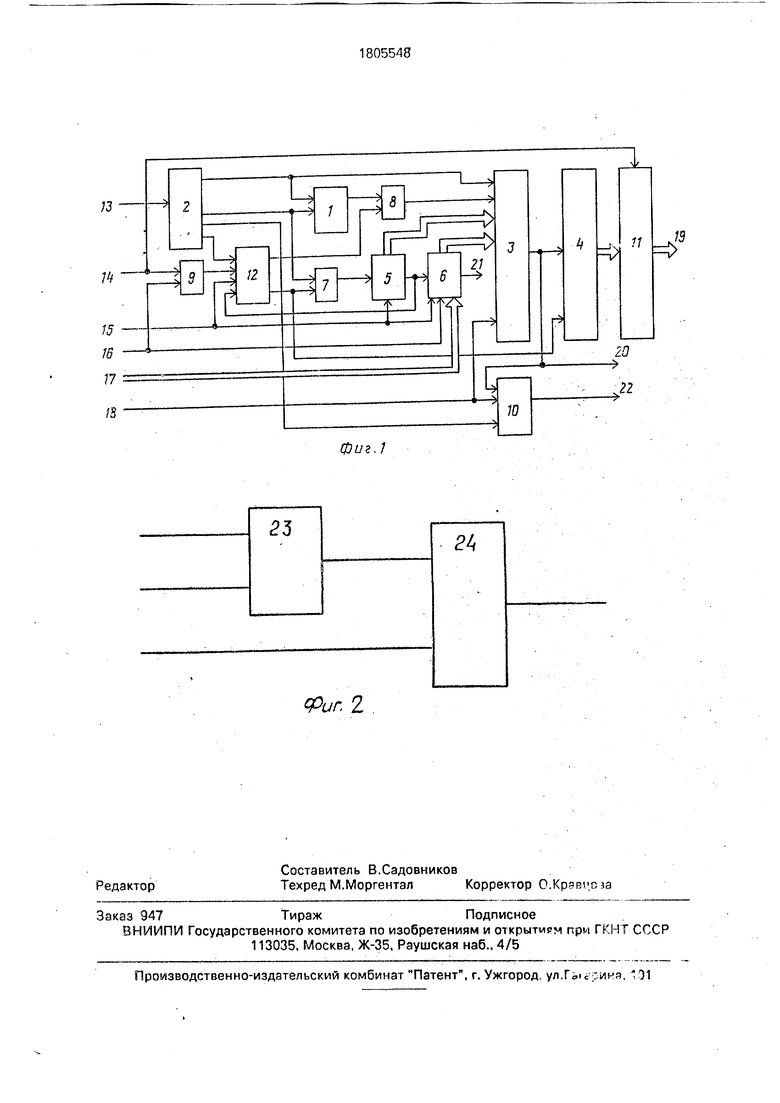

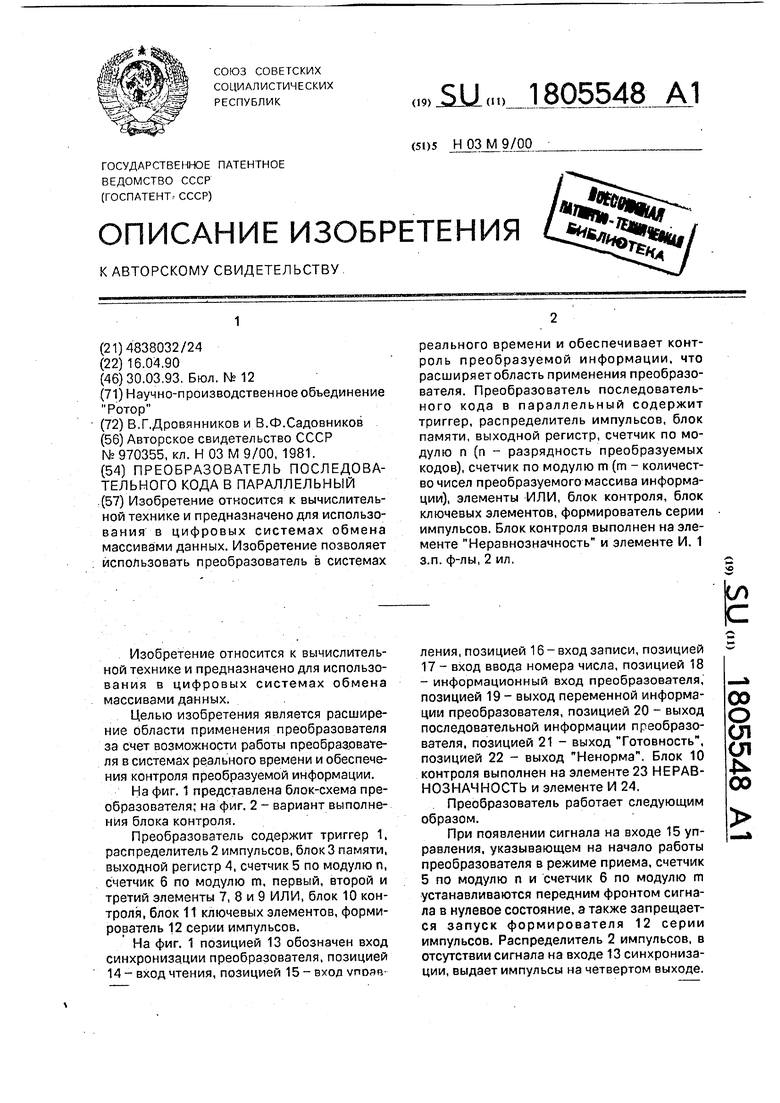

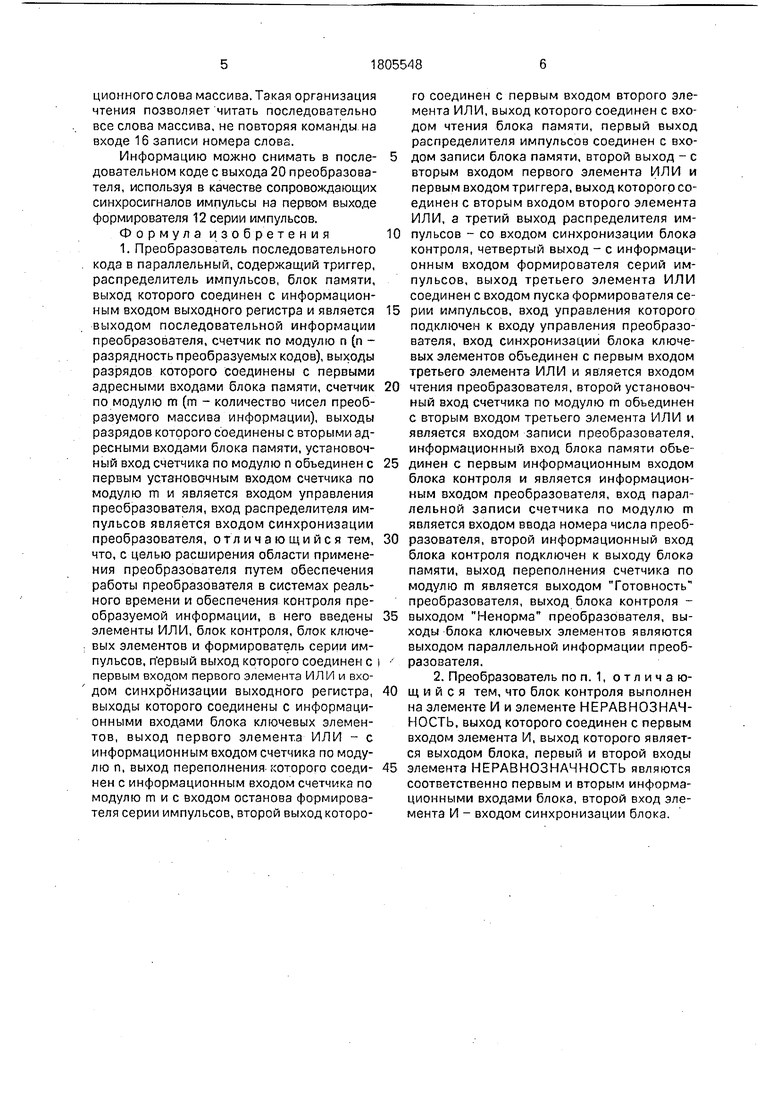

На фиг. 1 представлена блок-схема преобразователя; на фиг. 2 - вариант выполнения блока контроля.

Преобразователь содержит триггер 1, распределитель 2 импульсов, блок 3 памяти, выходной регистр 4, счетчик 5 по модулю п, счетчик 6 по модулю т, первый, второй и третий элементы 7, 8 и 9 ИЛИ, блок 10 контроля, блок 11 ключевых элементов, формирователь 12 серии импульсов.

На фиг. 1 позицией 13 обозначен вход синхронизации преобразователя, позицией 14-вход чтения, позицией 15-вход упоявления,позицией 16 - вход записи, позицией 17 - вход ввода номера числа, позицией 18 - информационный вход преобразователя, позицией 19 - выход переменной информации преобразователя, позицией 20 - выход последовательной информации преобразователя, позицией 21 - выход Готовность, позицией 22 - выход Ненорма. Блок 10 контроля выполнен на элементе 23 НЕРАВНОЗНАЧНОСТЬ и элементе И 24.

. Преобразователь работает следующим образом.

При появлении сигнала на входе 15 управления, указывающем на начало работы преобразователя в режиме приема, счетчик 5 по модулю п и счетчик 6 по модулю m устанавливаются передним фронтом сигнала в нулевое состояние, а также запрещается запуск формирователя 12 серии импульсов. Распределитель 2 импульсов, в отсутствии сигнала на входе 13 синхронизации, выдает импульсы на четвертом выходе.

00

о ел ел

Јь

00

Эти импульсы поступают на информационный вход формирователя 12 серии импульсов.

Поступление на информационный вход 18 преобразователя каждого бита информации сопровождается сигналом на входе 13 синхронизации преобразователя, по которому распределитель 2 импульсов вырабатывает серию из трех синхроимпульсов, первый из которых (с первого выхода распределителя. 2 импульсов) осуществляет синхронизацию записи очередного информационного разряда в блок 3 памяти и устанавливает триггер 1. сигнал с которого, поступая на блок 3 памяти через второй элемент 8 ИЛИ, позволяет считывать записанный бит информации на выходе блока 3 памяти.

Следующий синхроимпульс серии (с третьего выхода распределителя 2 импульсов) осуществляет проверку правильности записи бита информации в блок 3 памяти преобразователя, путем сравнения информации на входе и выходе блока 3 памяти. В случае несовпадения информации блок 10 контроля вырабатывает сигнал на выходе 22 Ненорма.

Последний синхроимпульс серии (со второго выхода распределителя 2 импульсов) сбрасывает триггер 1, снимая тем самым режим чтения блока 3 памяти, и, проходя через первый элемент 7 ИЛИ, по заднему фронту осуществляет прибавление единицы к содержимому счетчика 5 по модулю п, устанавливая адрес блока 3 памяти для приема нового бита информации. В случае переполнения счетчика 5 по модулю п, сигнал переноса увеличивает на единицу также и содержимое счетчика 6 по модулю т.

После выработки серии из трех синхроимпульсов распределитель 2 импульсов останавливается до окончания сигнала синхронизации на входе 13 преобразователя. Длительность импульсов на выходах распределителя 2 импульсов определяется необходимостью завершения формирования всей совокупности синхроимпульсов до снятия бита информации с информационного входа 18 преобразователя с одной стороны и быстродействием примененных элементов схемы с другой стороны.

Таким образом синхронизирующие импульсы на выходах-распределителя 2 импульсов обеспечивают запись каждого бита информации в блок 3 памяти, проверку правильности записи информации в блок 3 памяти, а также осуществляют счет принятых битов информации и смену адреса обращения к блоку 3 памяти.

После принятия всего массива информации, состоящего из m n-разрядных слов, счетчик 6 по модулю m вырабатывает сигнал переноса, и преобразователь выдает сигнал

на выходе 21 Готовность, указывающий на возможность передачи информации на обработку. Сигнал Готовность при необходимости может быть использован для управления режимом работы преобразова0 теля.

После окончания приема информации сигнал с входа 15 управления снимается и, следовательно, разрешается работа формирователя 12 серии импульсов. Когда внеш5 нее устройство, принимающее информацию с преобразователя, примет сигнал Готовность, оно может инициировать обмен информацией с преобразователем. Для этого необходимо подать на вход 16 преобразова0 теля команду записи, сопровождая ее номером считываемого слова на входе 17 преобразователя. После этого по команде чтения можно прочитать выбранное слово, подав команду на вход 14 чтения.

5 при подаче команды на вход 16 записи номера слова в счетчик 6 по модулю m записывается номер считываемого слова (от 0 до т-1), а по заднему фронту команды запускается формирователь 12 серии импульсов,

0 который формирует на своем первом выходе серию импульсов, а на втором выходе потенциальный сигнал. Потенциальный сигнал обеспечивает режим чтения блока 3 памяти, а импульсы на выходе формирователя

5 12 обеспечивают запись битов информации из блока 3 памяти в соответствующий разряд выходного регистра 4 и осуществляют прибавление единицы к содержимому счетчика 5 по модулю п, устанавливая адрес

0 блока 3 памяти для чтения нового бита информации. При переполнении счетчика 5 по модулю п, сигнал переноса увеличивает на единицу содержимое счетчика 6 по модулю m и сбрасывает формирователь 12 импуль5 сов в исходное положение.

После завершения указанных операций в выходном регистре 4 будет находиться информационное слово из массива с заданным номером, а в счетчике 6 по модулю m

0 будет подготовлен номер следующего слова массива.

При подаче команды на вход 14 чтения информация из выходного регистра 4 считывается в параллельном коде через блок 11

5 ключевых элементов, а при снятии команды на входе 14 чтения вновь запустится формирователь 12 серии импульсов и аналогично тому, как это происходило по команде на входе 16 записи номера слова, произойдет гюдготовка к чтению следующего информзционного слова массива. Такая организация чтения позволяет читать последовательно все слова массива, не повторяя команды на входе 16 записи номера слова.

Информацию можно снимать в после- довательном коде с выхода 20 преобразователя, используя в качестве сопровождающих синхросигналов импульсы на первом выходе формирователя 12 серии импульсов.

Формула изобретения 1. Преобразователь последовательного кода в параллельный, содержащий триггер, распределитель импульсов, блок памяти, выход которого соединен с информационным входом выходного регистра и является выходом последовательной информации преобразователя, счетчик по модулю п (п - разрядность преобразуемых кодов), выходы разрядов которого соединены с первыми адресными входами блока памяти, счетчик по модулю m (m - количество чисел преобразуемого массива информации), выходы разрядов которого соединены с вторыми адресными входами блока памяти, установочный вход счетчика по модулю п объединен с первым установочным входом счетчика по модулю m и является входом управления преобразователя, вход распределителя импульсов является входом синхронизации преобразователя, отличающийся тем, что, с целью расширения области применения преобразователя путем обеспечения работы преобразователя в системах реального времени и обеспечения контроля преобразуемой информации, в него введены элементы ИЛИ, блок контроля, блок ключевых элементов и формирователь серии импульсов, п ервый выход которого соединен с первым входом первого элемента ИЛИ и входом синхронизации выходного регистра, выходы которого соединены с информационными входами блока ключевых элементов, выход первого элемента ИЛИ - с информационным входом счетчика по модулю п, выход переполнения, гсоторого соеди- нен с информационным входом счетчика по модулю тис входом останова формирователя серии импульсов, второй выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом чтения блока памяти, первый выход распределителя импульсов соединен с входом записи блока памяти, второй выход - с вторым входом первого элемента ИЛИ и первым входом триггера, выход которого соединен с вторым входом второго элемента ИЛИ, а третий выход распределителя импульсов - со входом синхронизации блока контроля, четвертый выход - с информационным входом формирователя серий импульсов, выход третьего элемента ИЛИ соединен с входом пуска формирователя серии импульсов, вход управления которого подключен к входу управления преобразователя, вход синхронизации блока ключевых элементов объединен с первым входом третьего элемента ИЛИ и является входом чтения преобразователя, второй установочный вход счетчика по модулю m объединен с вторым входом третьего элемента ИЛИ и является входом записи преобразователя, информационный вход блока памяти объединен с первым информационным входом блока контроля и является информационным входом преобразователя, вход параллельной записи счетчика по модулю m является входом ввода номера числа преобразователя, второй информационный вход блока контроля подключен к выходу блока памяти, выход переполнения счетчика по модулю m является выходом Готовность преобразователя, выход блока контроля - выходом Ненорма преобразователя, выходы блока ключевых элементов являются выходом параллельной информации преобразователя.

фиг.1

Фиг. 2

р

/5

| Преобразователь последовательного кода в параллельный | 1981 |

|

SU970355A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-03-30—Публикация

1990-04-16—Подача